Wafer flow sheet surface flatness detection device capable of avoiding false flaws

A surface flatness and detection device technology, which is applied in semiconductor/solid-state device testing/measurement, electrical components, semiconductor/solid-state device manufacturing, etc., can solve problems such as increasing processing costs, reducing production efficiency, and inaccurate data, so as to avoid Secondary maintenance, reduce processing costs, scan comprehensive effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

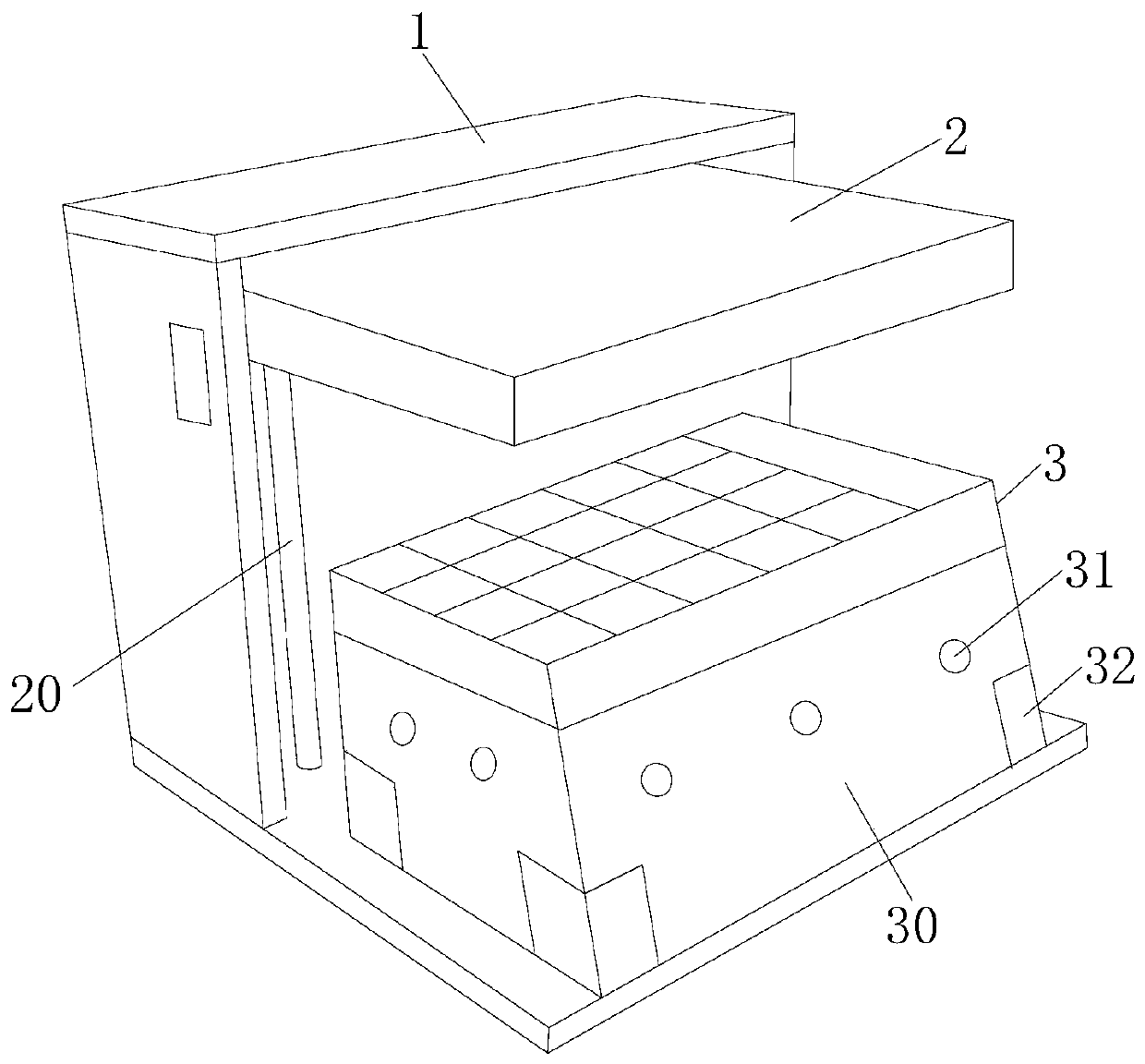

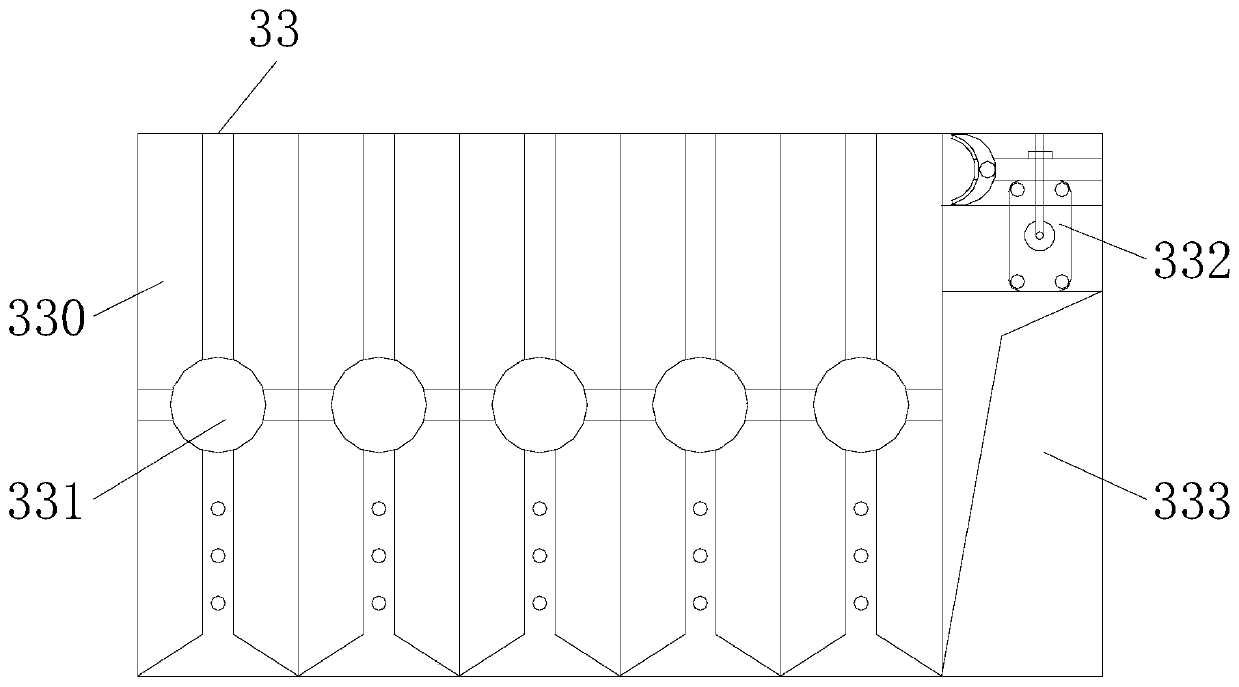

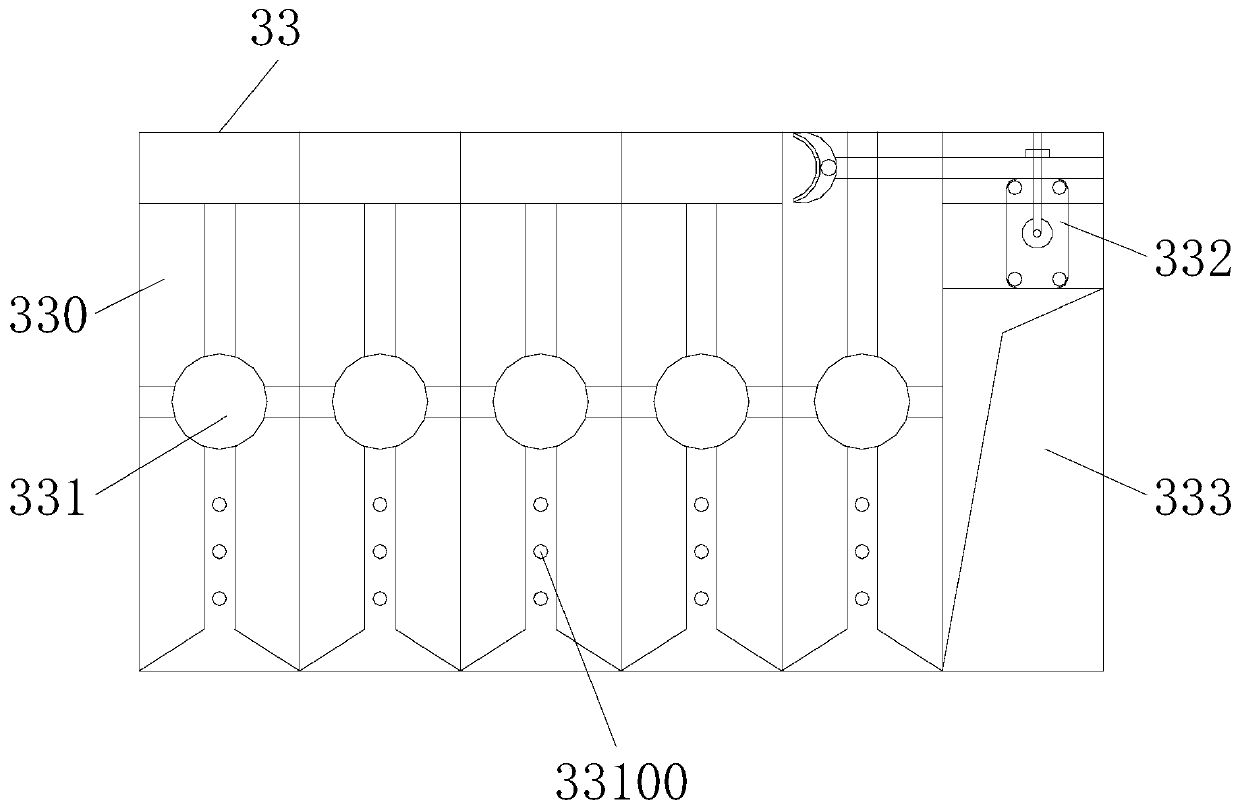

[0027] see Figure 1-9 , the present invention provides a technical scheme of a wafer surface flatness detection device that avoids false defects: its structure includes a test frame 1, a scanning board 2, and a delivery table 3, and the test frame 1 is connected to the scanning board 2 by rails. The scanning board 2 is threadedly connected with a threaded rod 20, the threaded rod 20 is installed on the test frame 1, the scanning board 2 can be lifted, and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More