Gate-around parasitic interconnection capacitance extraction method for source-drain raised FDSOI device

A technology of interconnection capacitance and extraction method, which is applied to semiconductor devices, electric solid-state devices, semiconductor/solid-state device components, etc., can solve problems such as the influence of circuit simulation accuracy, and achieve the effect of avoiding circuit simulation inaccuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

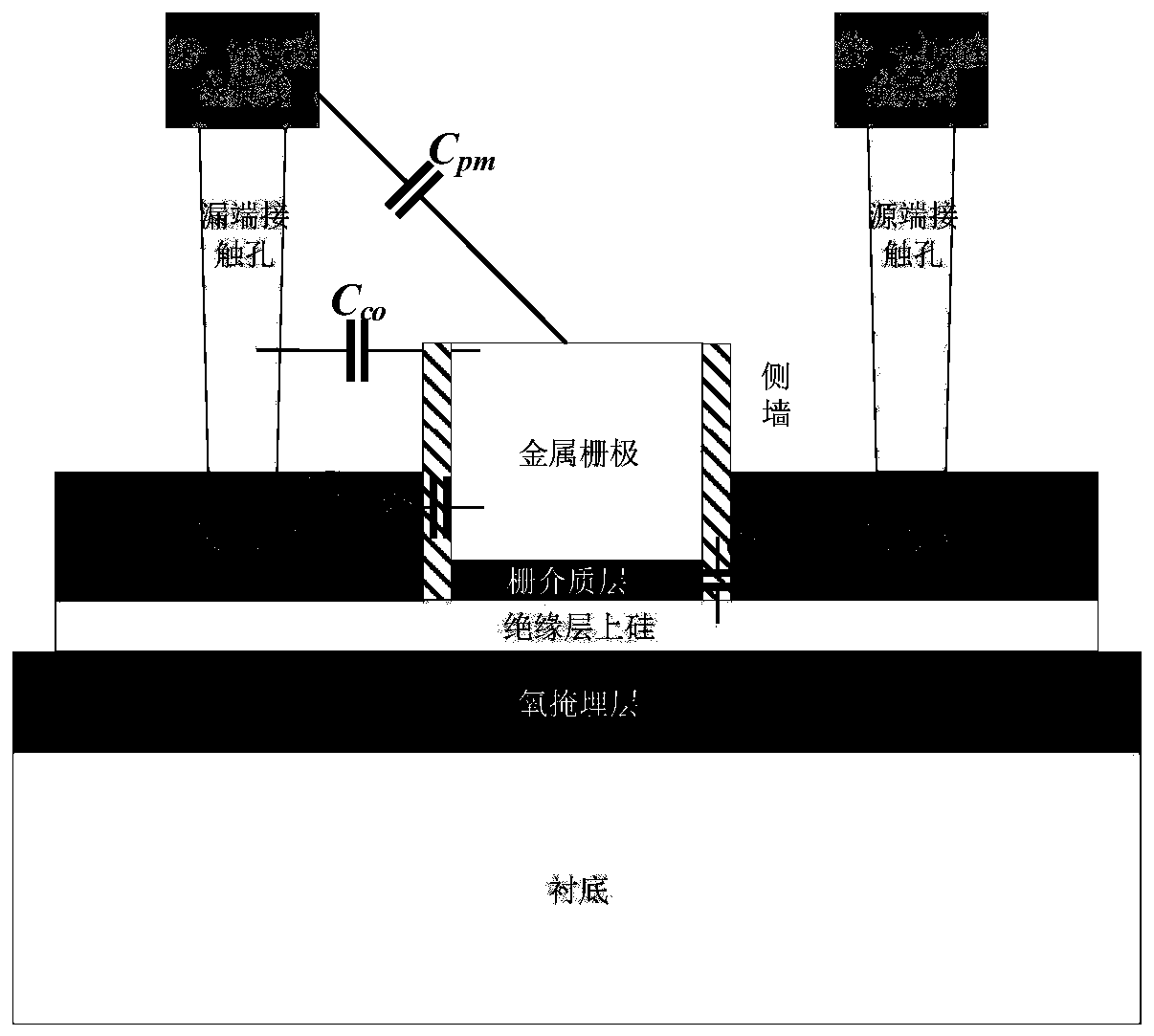

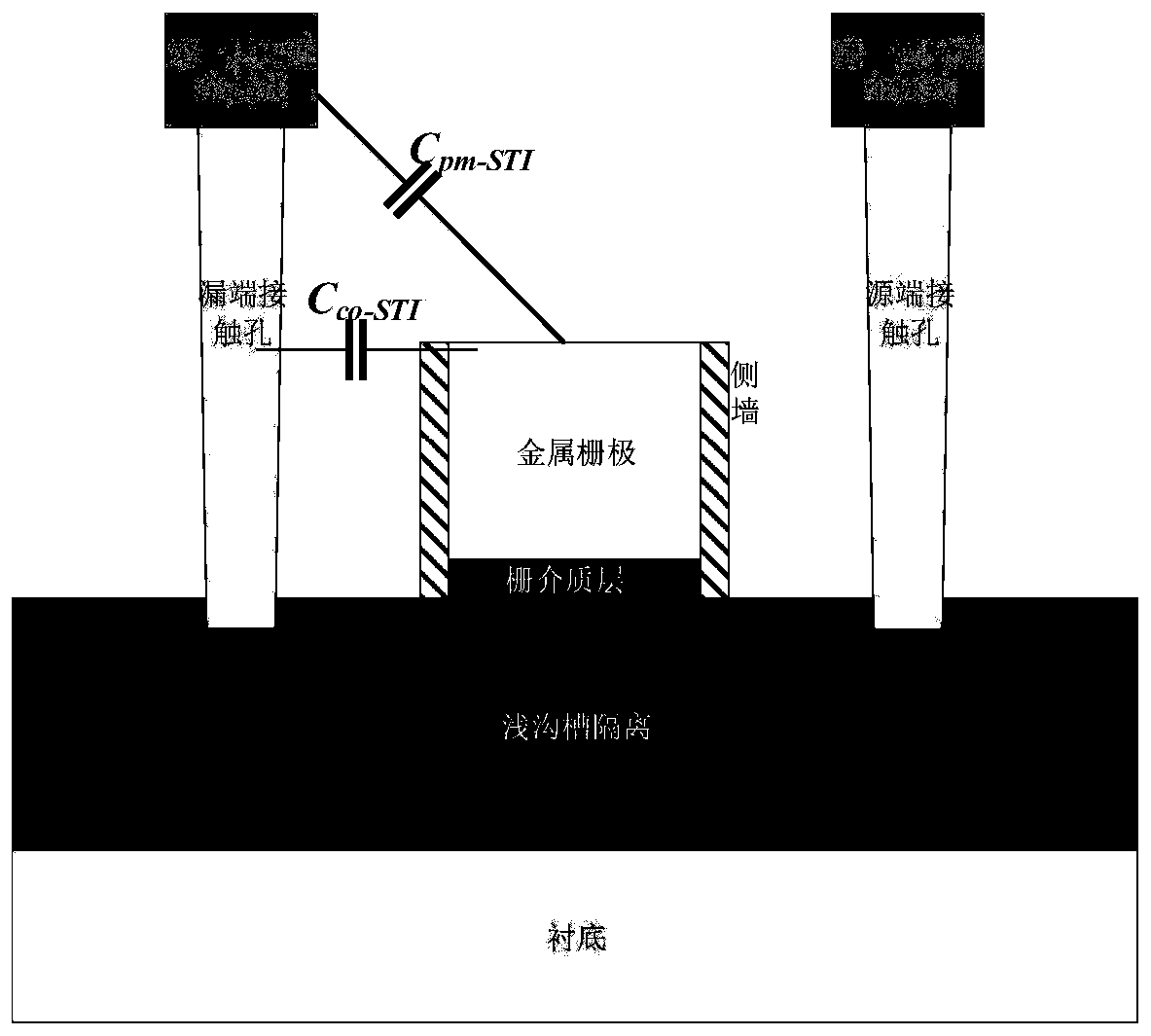

[0036] The method for extracting parasitic interconnection capacitance around the gate of the FDSOI device with raised source and drain proposed by the present invention, based on a three-dimensional field simulator, can accurately separate the interconnection capacitance C from the parasitic capacitance around the gate. co and C pm value. Concrete extraction method of the present invention has the following steps:

[0037] Step 1: Layout structure design, testing and process fluctuation value acquisition. The detailed steps are as follows:

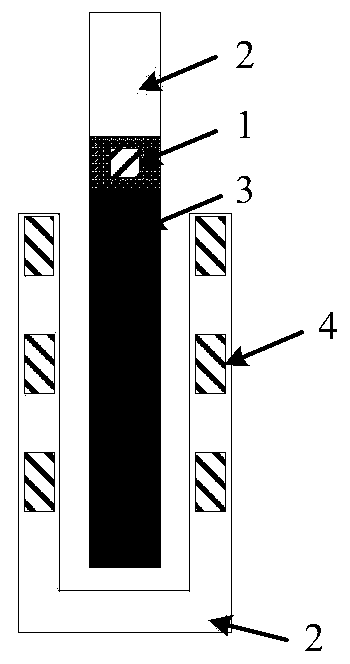

[0038] Step 1a: Design CT-on-STI de-embedding layout structure and CT-on-RSD parasitic extraction layout structure, such as image 3 and Figure 7 As shown in the figure, 1-gate contact hole, 2-first-layer interconnection metal line, 3-metal gate, 4-source or drain contact hole, 5-active region. pass figu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More