Systolic Array Based Sparse Neural Network Processor

A neural network and processor technology, applied in the field of computer architecture for sparse neural network computing, can solve the problems of irregularity of sparse patterns and difficulty in effectively utilizing the sparsity of neural networks, etc., to reduce memory capacity, reduce space overhead, The effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to specific embodiments and accompanying drawings.

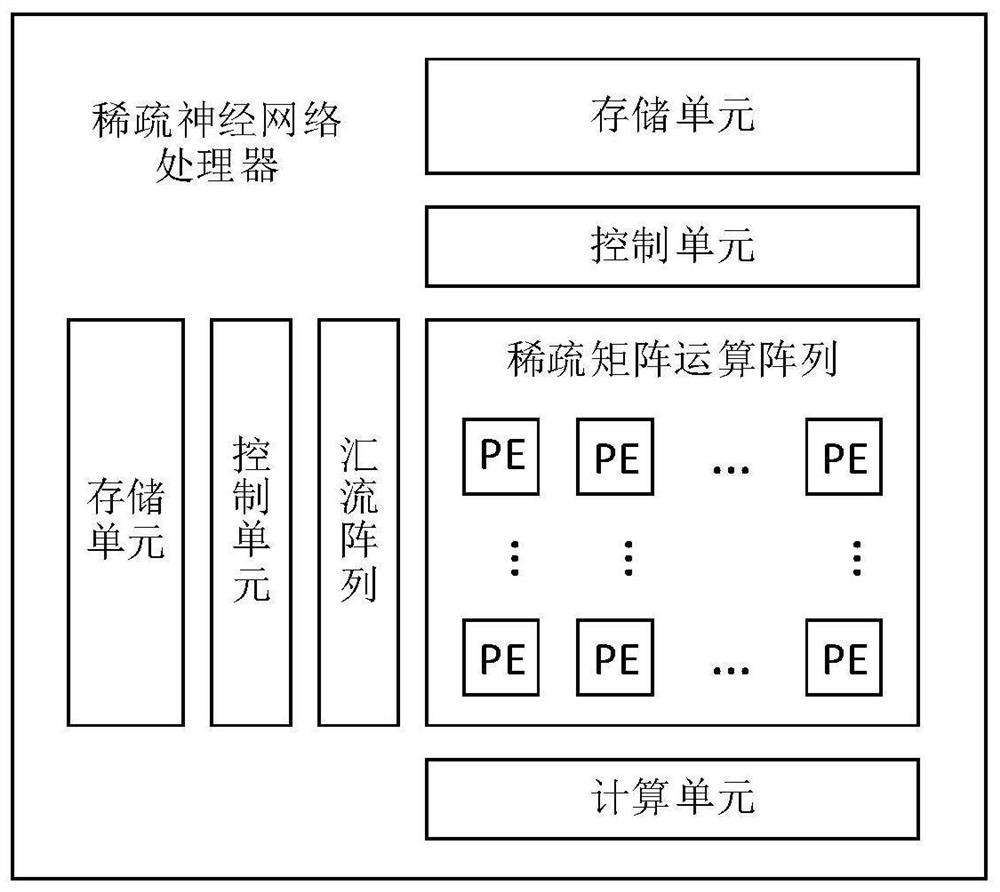

[0037] figure 1 It is a schematic diagram of the architecture of a sparse neural network processor according to an embodiment of the present invention. It includes storage unit, control unit, bus array, sparse matrix operation array and calculation unit. The storage unit is used to store the neural network weights, gradients, features, and instruction sequences for data flow scheduling. The control unit is connected with the storage unit, and according to the scheduling of the instruction sequence, obtains the required data from the storage, reshapes the data into the form of matrix operation, and then is bridged by the bus array and sent to the sparse matrix operation array. to complete the corresponding calculation. The calculation uni...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap