Self-adaptive read path delay calculation method and circuit for DRAM physical interface

A physical interface and path delay technology, which is applied in the adaptive read path delay calculation method and circuit field, can solve the problems of no read data delay calculation, etc., and achieve the effect of accurately calculating the read path delay, simplifying parameter information, and simplifying the method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071] In order to more clearly illustrate the technical solutions in the embodiments of the present invention, the drawings that need to be used in the description of the embodiments will be briefly introduced below. Obviously, the drawings in the following description are only some embodiments of the present invention. For those skilled in the art, other drawings can also be obtained based on these drawings without creative effort.

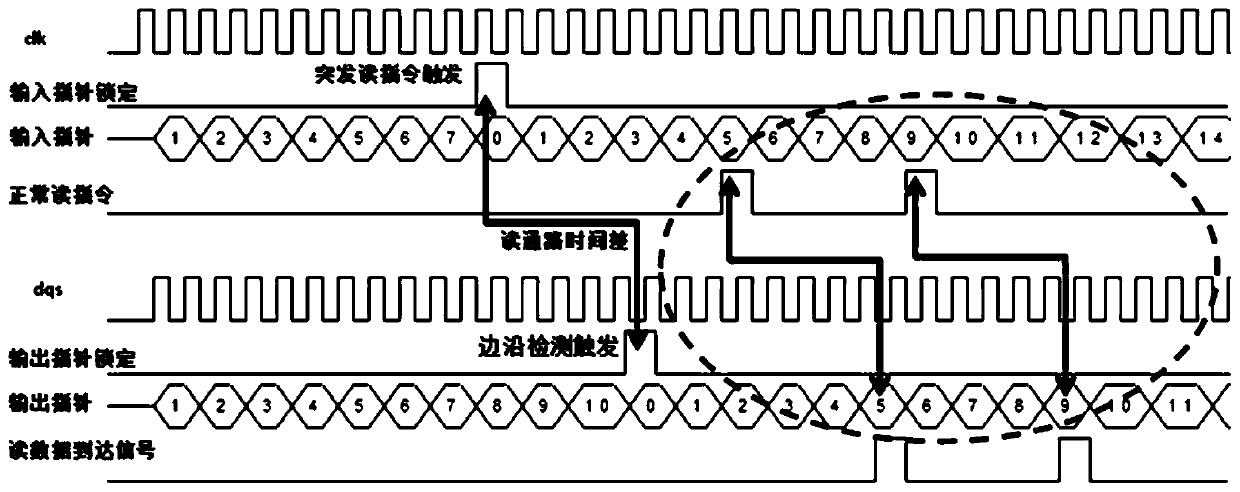

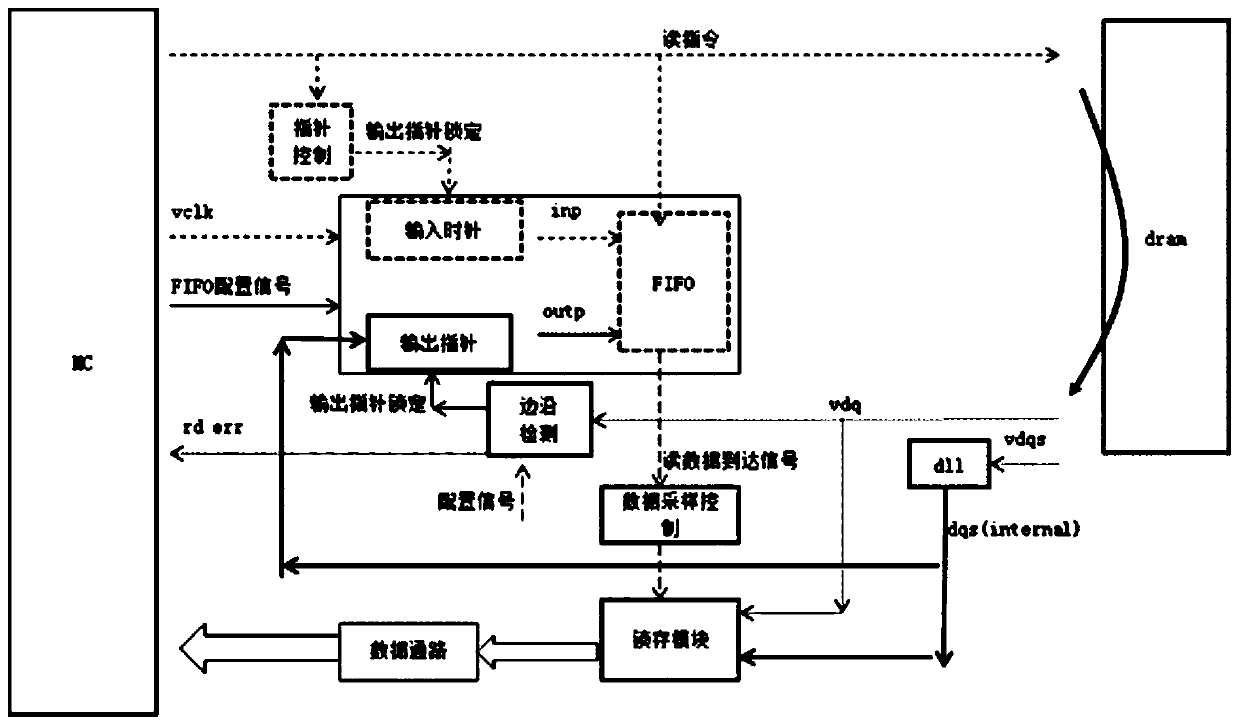

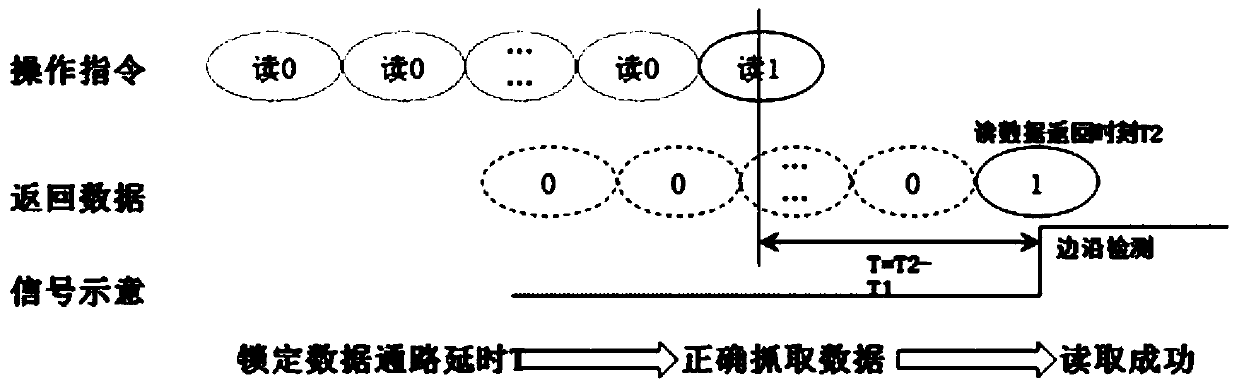

[0072] The present invention as figure 1 and figure 2 As shown, considering the impact of various delays in the entire read process on signal transmission, for the physical interface of the memory, whether the correct sampling and transmission of data determines whether the read operation process can be completed correctly. Correctly calculate and judge the arrival time of the read data, and sample and obtain it in time. Its essence lies in the calculation and determination of the signal path delay (the time difference between the time when t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More