Automatic layout wiring generation method based on sparse grids

A sparse grid, grid line technology, applied in special data processing applications, instruments, electrical digital data processing and other directions, can solve problems such as the efficiency cannot be optimized, the recording space is large, and the Hightower algorithm cannot be searched, etc. The effect of increasing space and exploring space, decreasing space availability, and decreasing storage space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

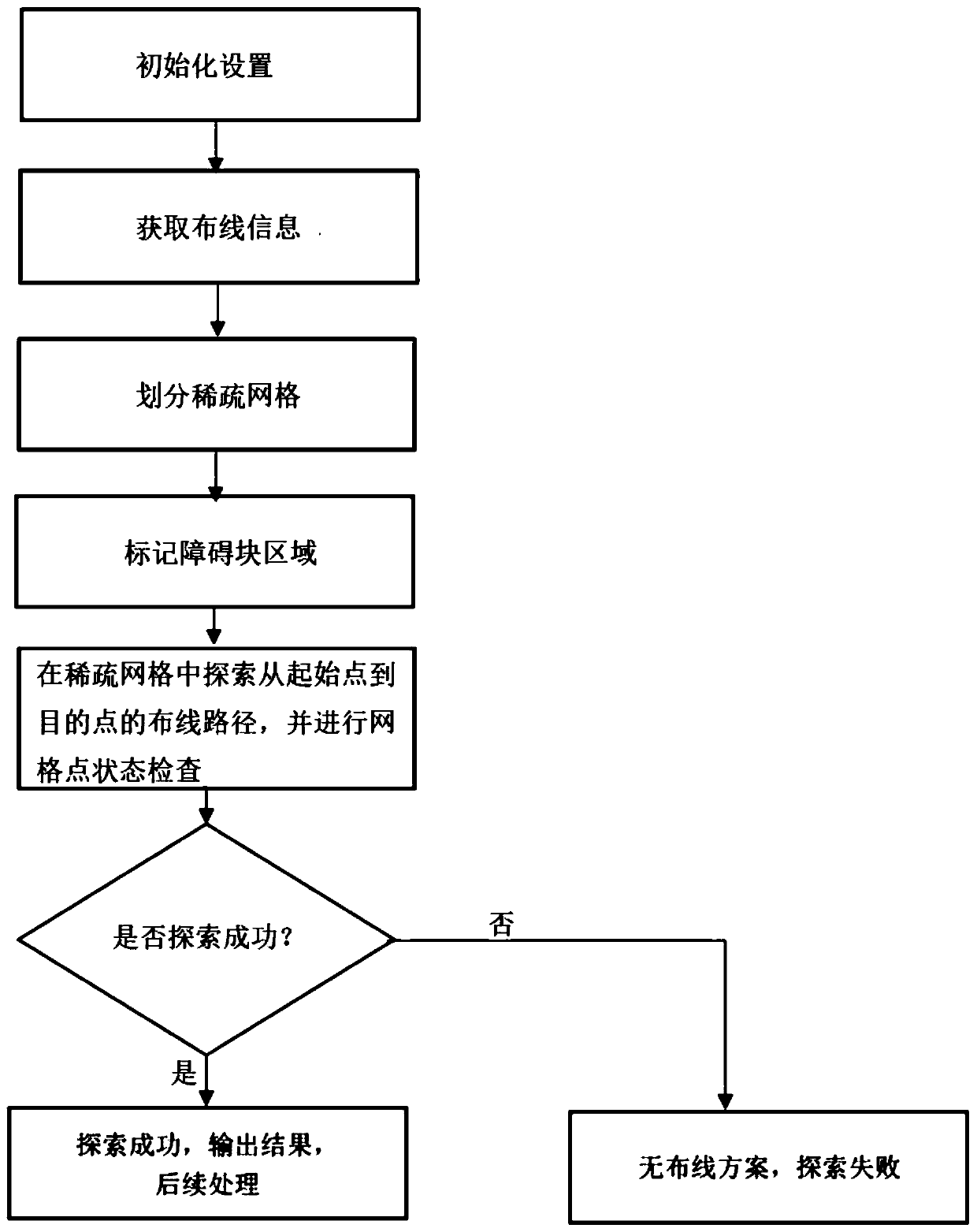

[0060] Such as figure 1 An automatic layout and routing generation method for sparsely divided grids is shown, which specifically includes the following steps:

[0061] Step (1), initialize settings:

[0062] Set the winding width to m, the winding gap to n, get all the components to be routed, and mark the pins of the components to be routed as unused.

[0063] Step (2), obtain wiring information:

[0064] Select two components to be routed, determine the route area, and obtain all obstacles that cannot be routed in the route area, including the existing route topology in the route area.

[0065] Select one pin from the unused pins of the two components as the start pin and the destination pin respectively. The method of determining the starting pin and the destination pin is as follows: for the two selected components to be routed, set one...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More