Redundancy error correction structure of OTP

A technology of redundant error correction and redundant storage, applied in the field of redundant error correction structure, which can solve the problems of reducing the error correction rate, unable to correct at the same time, and wasting the area of storage space.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

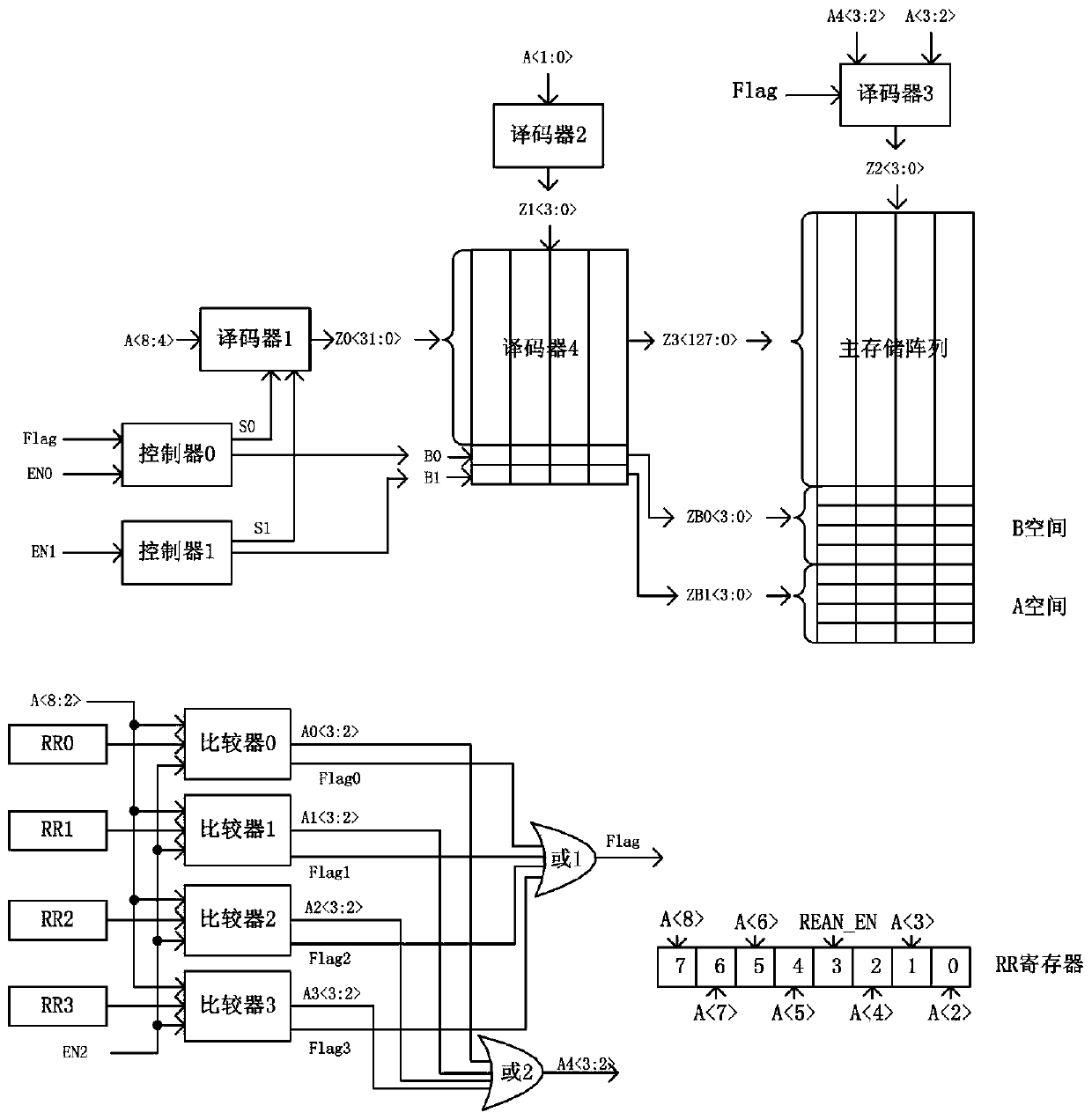

[0013] see figure 1 , this embodiment provides an OTP redundant error correction structure, including a redundant storage array, an address decoding module and a logic control module. The redundant storage array is divided into an A space for storing the address of the damaged storage unit and a B space for replacing the damaged storage unit; the address decoding module is used to decode the input address A, and at the same time Add redundant memory array address during decoding; the logic control module is used to compare the input address with the address of the damaged memory unit stored in the A space, and generate a control signal to control the memory read in the case of damaged memory cells in the main memory array. operate.

[0014] Wherein, the redundant storage array and the main storage array are in the same storage array area. The redundant storage array is divided into 16bytes B space and 16 bytes A space. The address decoding module includes 4 decoders: Decode...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More