memory allocation

A technology of memory allocation and memory, which is applied in the direction of memory architecture access/allocation, resource allocation, memory system, etc., and can solve problems that affect the performance of the processing system, conflicts, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The following description is presented by way of example to enable any person skilled in the art to make and use the invention. The present invention is not limited to the embodiments described herein, and various modifications to the disclosed embodiments will be apparent to those skilled in the art.

[0039] Embodiments will now be described by way of example only.

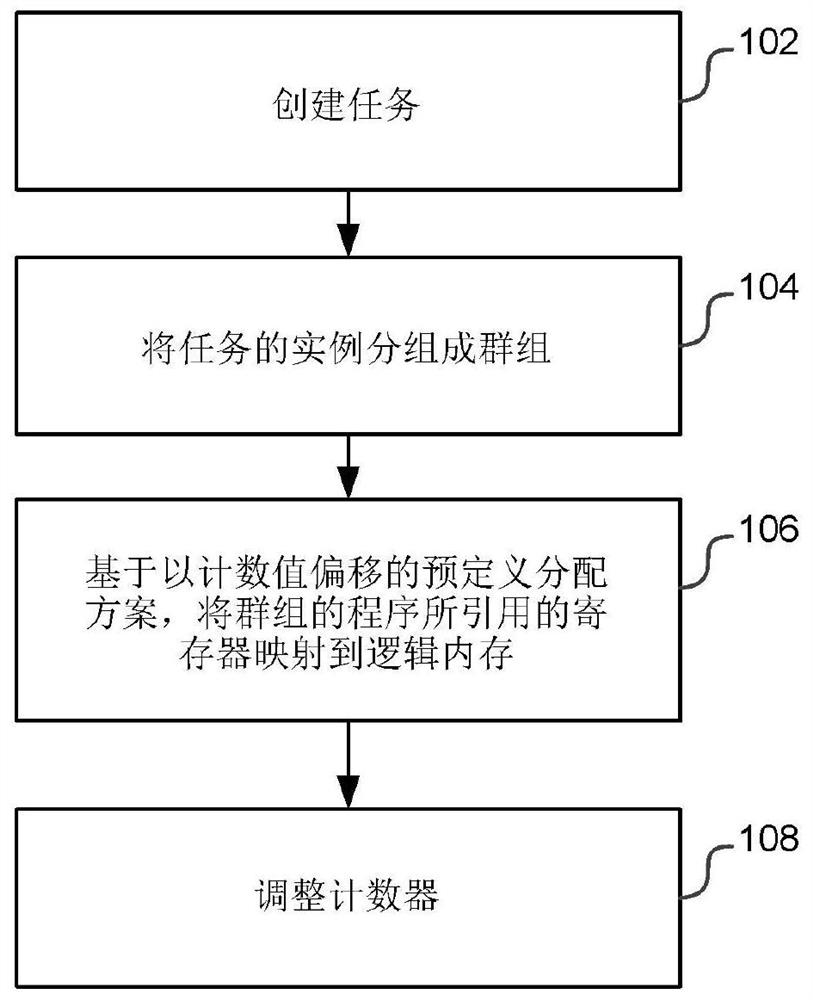

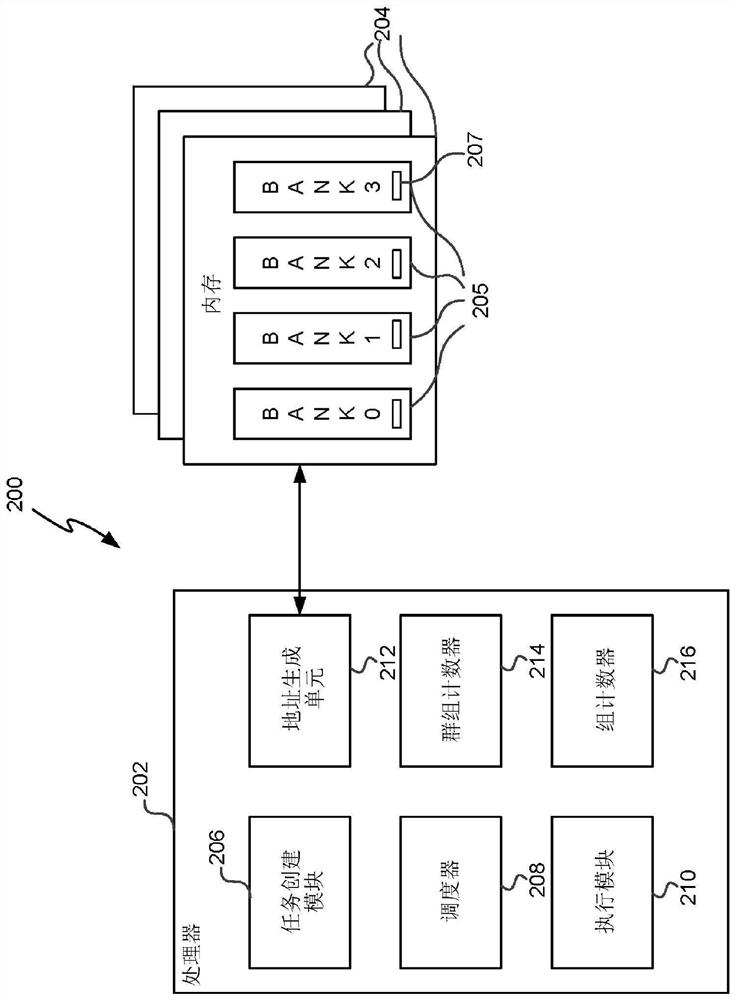

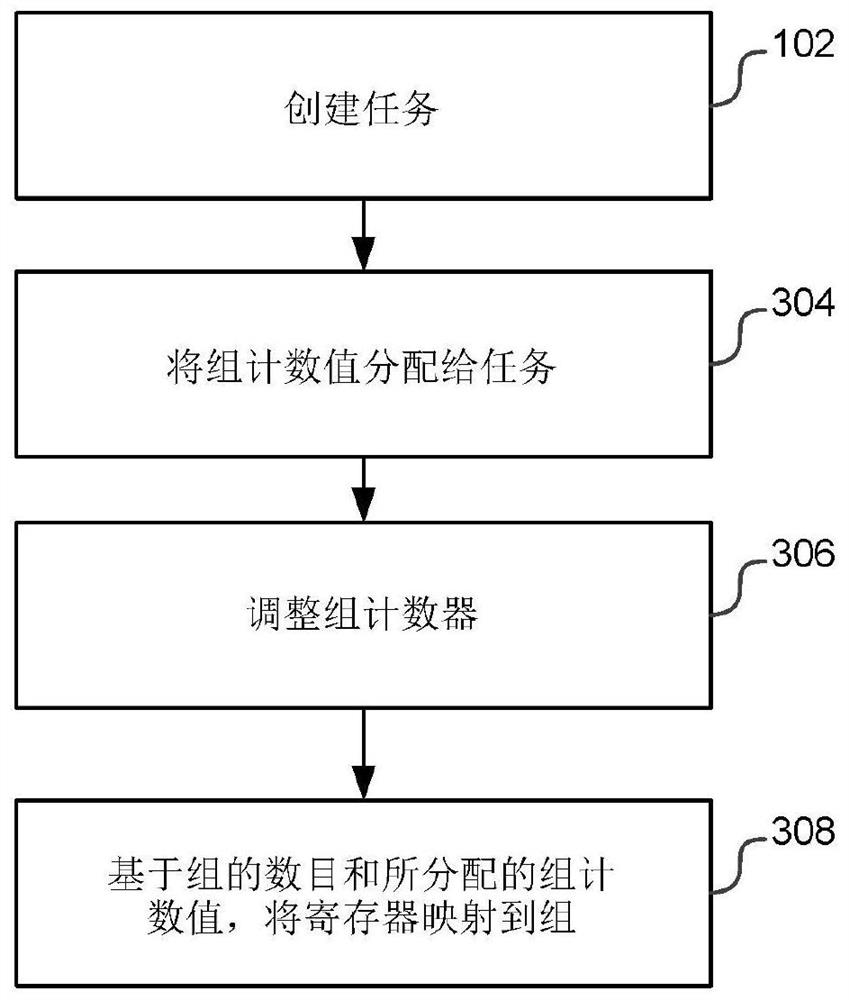

[0040] As described above, a processing system (eg, a system including a CPU or GPU and memory) may include multiple banks within the memory. An executed instruction (eg, a read or write instruction) typically does not refer to any particular group, but only to a register number, eg, read r0, where r0 refers to register 0. In known processing systems, an address generation unit maps register numbers to in-memory banks based on a defined formula (or relationship), such as:

[0041] (group number) = (register number) mod (number of groups)

[0042] (Equation 1)

[0043] And the address decoding logic with...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More