Pixel circuit, driving method thereof, display panel and display device

A technology of a pixel circuit and a driving module, which is applied in the fields of pixel circuits, display panels and display devices, can solve the problems of short data charging time and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

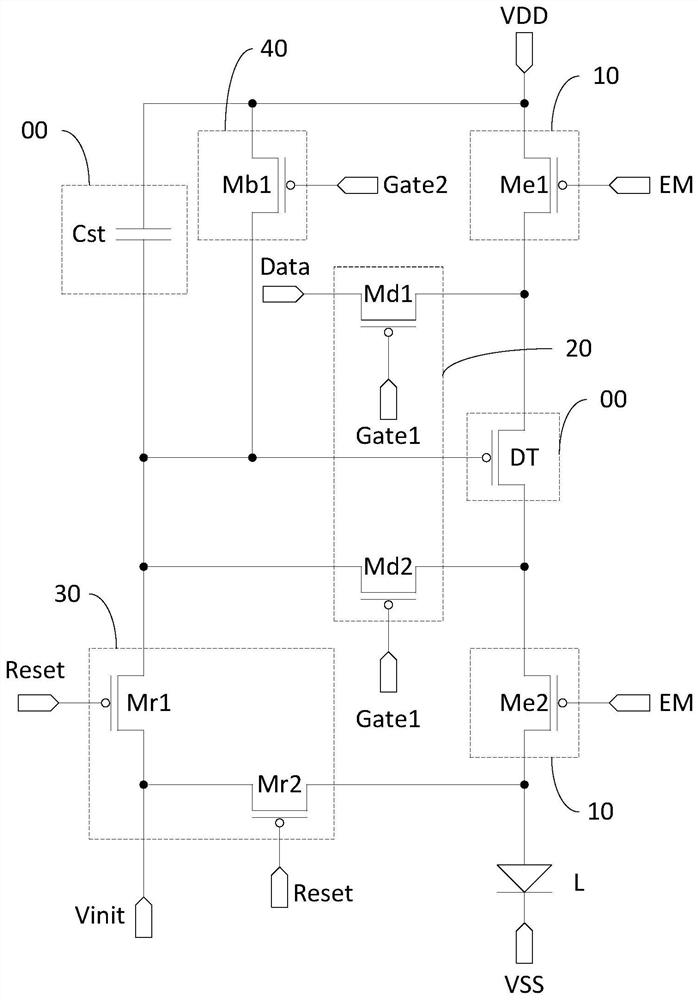

[0099] Below to Figure 5 shown on the display panel, as figure 1 The structure of the pixel circuit shown as an example, combined with Figure 7 The shown signal sequence diagram describes the working process of the above-mentioned display panel provided by the embodiment of the present invention. Among them, RE-n in the figure is the signal of the reset signal terminal Reset of the nth row of subpixels, Gate1-n is the signal of the first scanning signal terminal Gate1 of the nth row of subpixels, and Gate2-n is the signal of the nth row of subpixels The signal of the second scanning signal terminal Gate2, EM-n is the signal of the light emission control signal terminal EM of the nth row of sub-pixels. The working process of the first row of sub-pixels in the display panel is taken as an example for illustration below, and the working process of other rows of sub-pixels in the display panel may be basically the same as that of the first row of sub-pixels. Specifically, cho...

Embodiment 2

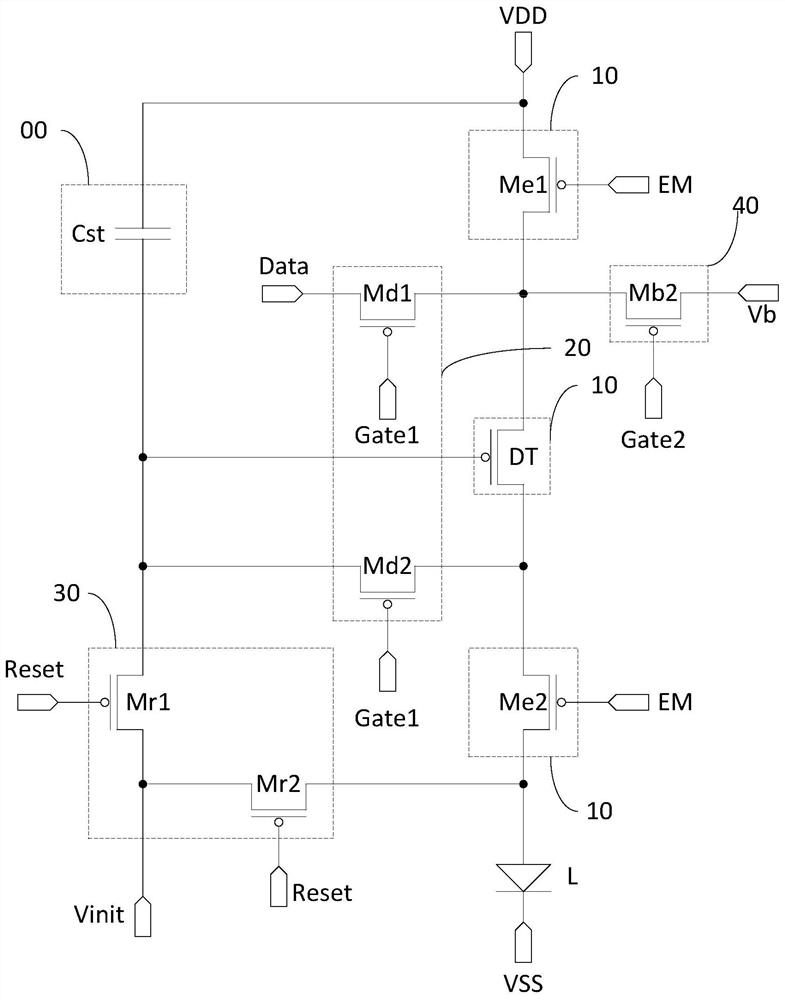

[0109] Below to Figure 5 shown on the display panel, as figure 2 The structure of the pixel circuit shown as an example, combined with Figure 7 The shown signal sequence diagram describes the working process of the above-mentioned display panel provided by the embodiment of the present invention. This embodiment is a modification of some of the implementation manners in the first embodiment. The following only describes the differences between this embodiment and the first embodiment, and the similarities will not be repeated here.

[0110] In the reset phase t1, the data writing phase t2, and the light emitting phase t3, Gate2-1=1, then the second black frame transistor Mb2 is turned off.

[0111]In the black picture insertion stage t4, RE-1=1, Gate1-1=1, Gate2-1=0, EM-1=0. If RE-1=1, the first reset transistor Mr1 and the second reset transistor Mr2 are turned off. Gate1-1=1, then the first data writing transistor Md1 and the second data writing transistor Md2 are tu...

Embodiment 3

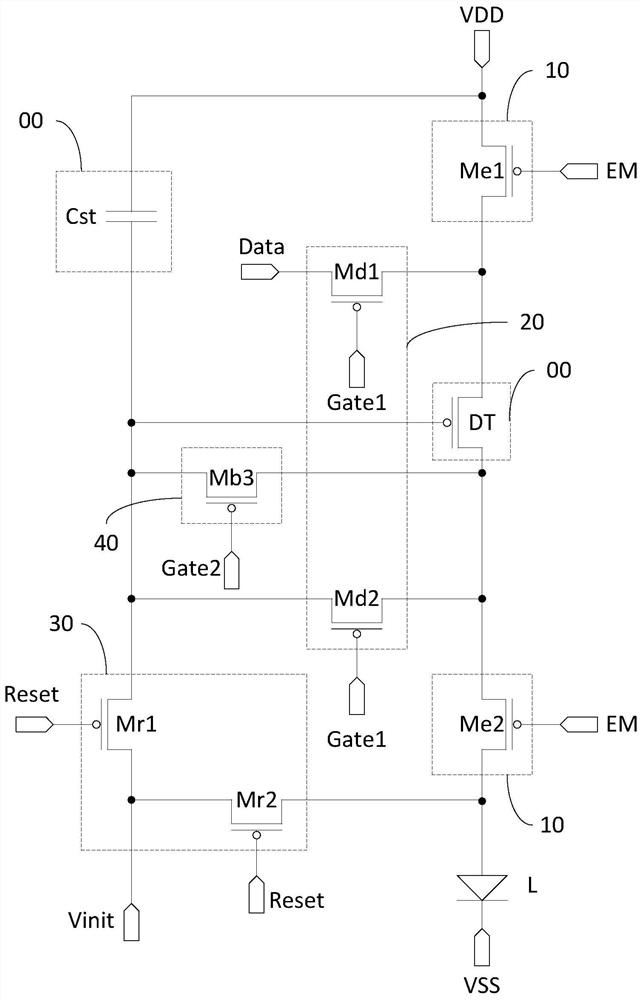

[0113] Below to Figure 5 shown on the display panel, as image 3 The structure of the pixel circuit shown as an example, combined with Figure 7 The shown signal sequence diagram describes the working process of the above-mentioned display panel provided by the embodiment of the present invention. This embodiment is a modification of some of the implementation manners in the first embodiment. The following only describes the differences between this embodiment and the first embodiment, and the similarities will not be repeated here.

[0114] In the reset phase t1, the data writing phase t2, and the light emitting phase t3, Gate2-1=1, the third black frame transistor Mb3 is turned off.

[0115] In the black picture insertion stage t4, RE-1=1, Gate1-1=1, Gate2-1=0, EM-1=0. If RE-1=1, the first reset transistor Mr1 and the second reset transistor Mr2 are turned off. Gate1-1=1, then the first data writing transistor Md1 and the second data writing transistor Md2 are turned o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More