Decoding processing method and device

A processing method and decoding technology, applied in the direction of using linear codes for error correction/detection, using block codes for error correction/detection, digital transmission systems, etc., can solve problems such as superior delay, poor performance, and use restrictions. Achieve the effect of improving decoding performance and reducing time complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

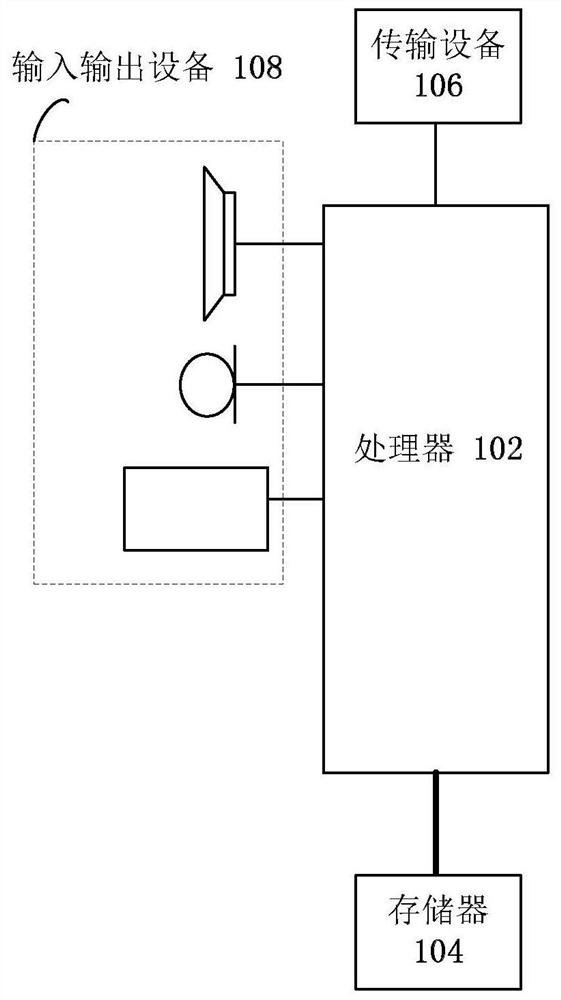

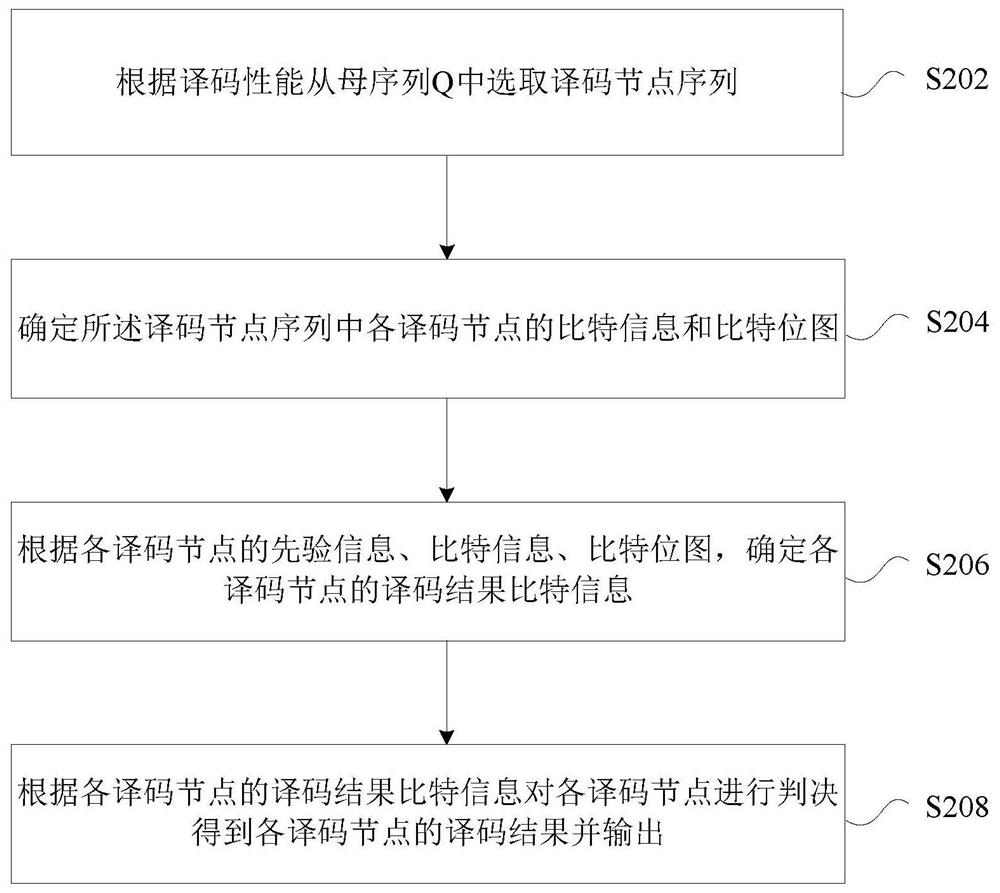

[0030] The method embodiment provided in Embodiment 1 of the present application may be executed in a mobile terminal, a computer terminal, or a similar computing device. Taking running on a mobile terminal as an example, figure 1 It is a hardware structural block diagram of a mobile terminal of a decoding processing method according to an embodiment of the present invention, as figure 1 As shown, the mobile terminal 10 may include one or more ( figure 1 Only one is shown in the figure) a processor 102 (the processor 102 may include but not limited to a processing device such as a microprocessor MCU or a programmable logic device FPGA) and a memory 104 for storing data. Optionally, the above-mentioned mobile terminal also A transmission device 106 for communication functions as well as input and output devices 108 may be included. Those of ordinary skill in the art can understand that, figure 1 The shown structure is only for illustration, and does not limit the structure o...

example 1

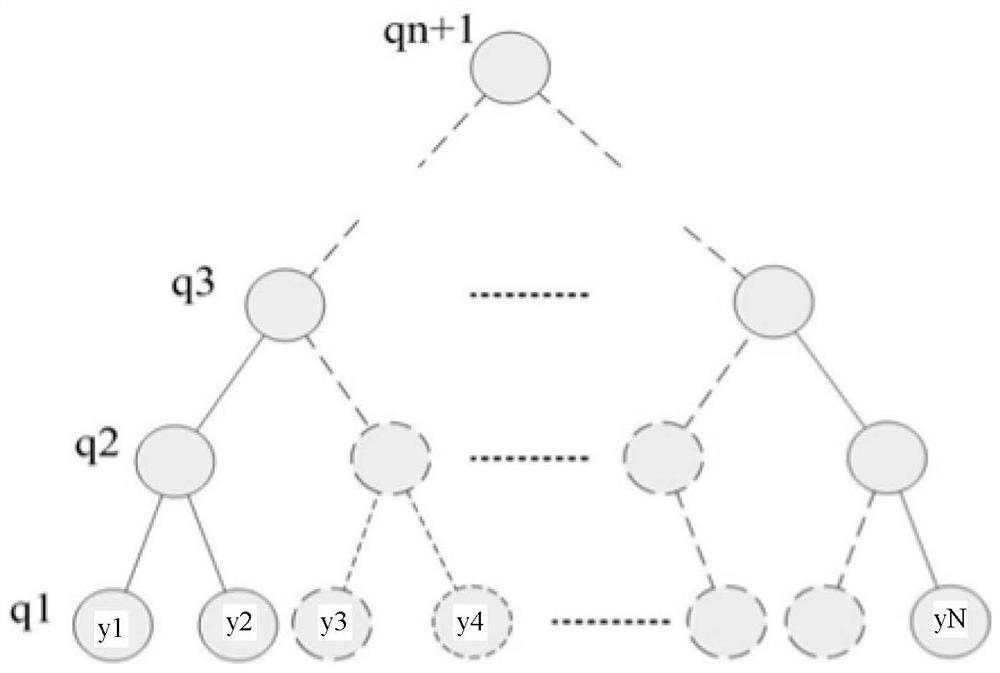

[0110] Assume that the number of information bits K=512, the mother code length N=1024, n=10, the freezing bits at the sending end are set to all zeros, and the modulation method is BPSK. The specific steps are as follows:

[0111] Step 1. Parameter determination: when the first BP decoding node in the decoding sequence contains information bits, the greater the serial decoding order S, the better the performance of the decoding Block Error Rate (BLER). Good, but at the same time it will increase the decoding delay. Therefore, when the block error rate BLER performance priority is greater than the decoding delay priority, in order to achieve the best decoding performance, set S to the largest S under the condition that the deepest decoding node contains information bits. If the decoding delay priority is greater than the BLER performance priority, select S=1. Other scenarios S can be set according to the performance requirements of specific services (such as delay requirement...

example 2

[0162] Assume that the number of information bits K=256, the mother code length N=1024, n=10, the freezing bits at the sending end are set to all zeros, and the modulation method (Binary Phase Shift Keying, referred to as BPSK), the specific steps are as follows:

[0163] Step 1. Strategy requirements: Consider the decoding block error rate and decoding delay in the compromise between information bits and transmission bits, then according to the bitmap V, it can be known that information bits are not included in the first 128 bits, and information bits are not included in the first 256 bits. including information bits. From N=1024, it can be known that the optional decoding node sequence Q{q 1 ,q 2 ,...,q 11}, according to the decoding delay and block error rate requirements, according to the following method to select the decoding node sequence in a variety of selection methods. In the case of parallel implementation of the BP decoding algorithm with prior information, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More