Multi-lane serializer device

一种串行器、多通道的技术,应用在同步装置、同步信息通道、并行/串行转换等方向,能够解决无法通知、无法第1时钟与加载信号相位差恢复等问题,达到简易结构、减低误码率的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. In addition, in the description of the drawings, the same reference numerals are assigned to the same elements, and overlapping descriptions are omitted. The present invention is not limited to these examples, and includes all changes within the meaning and range equivalent to the claims and the scope of the claims.

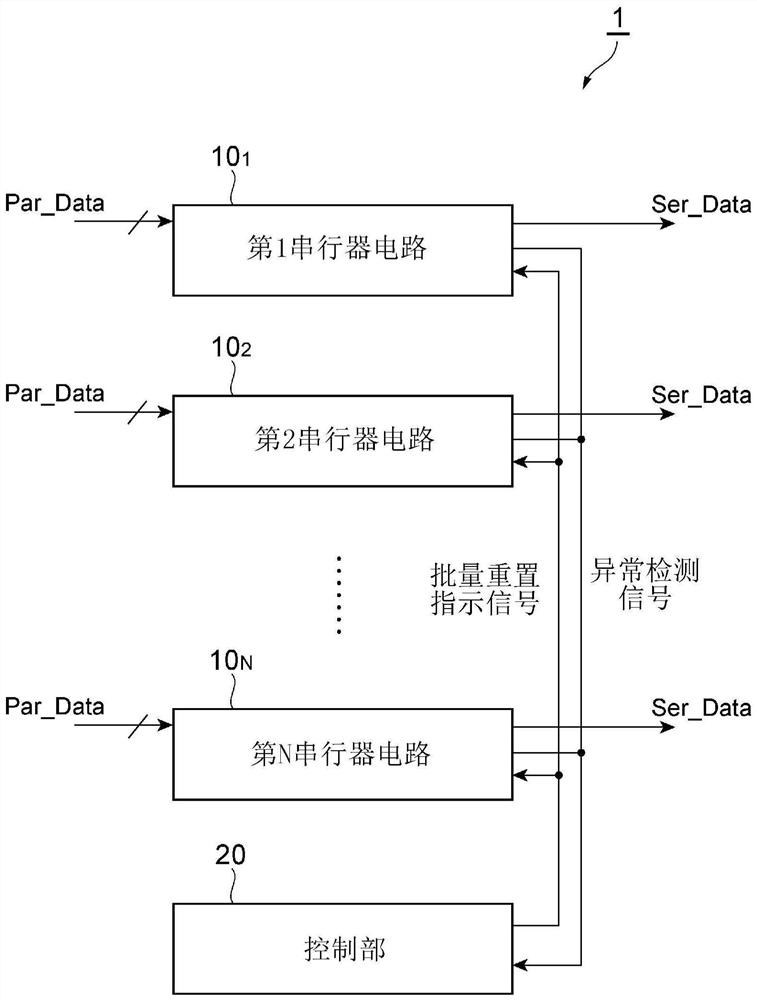

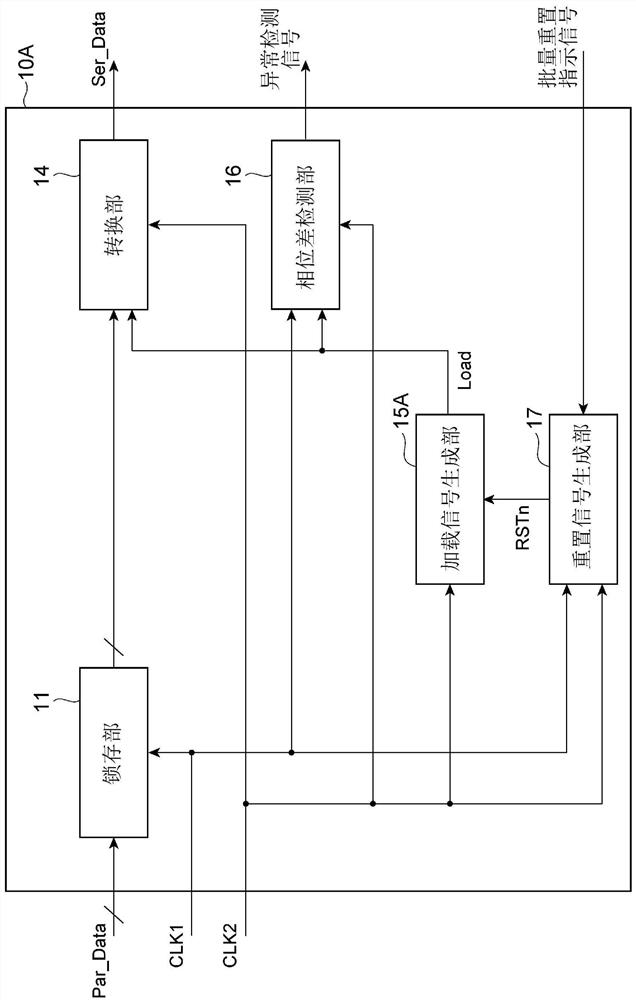

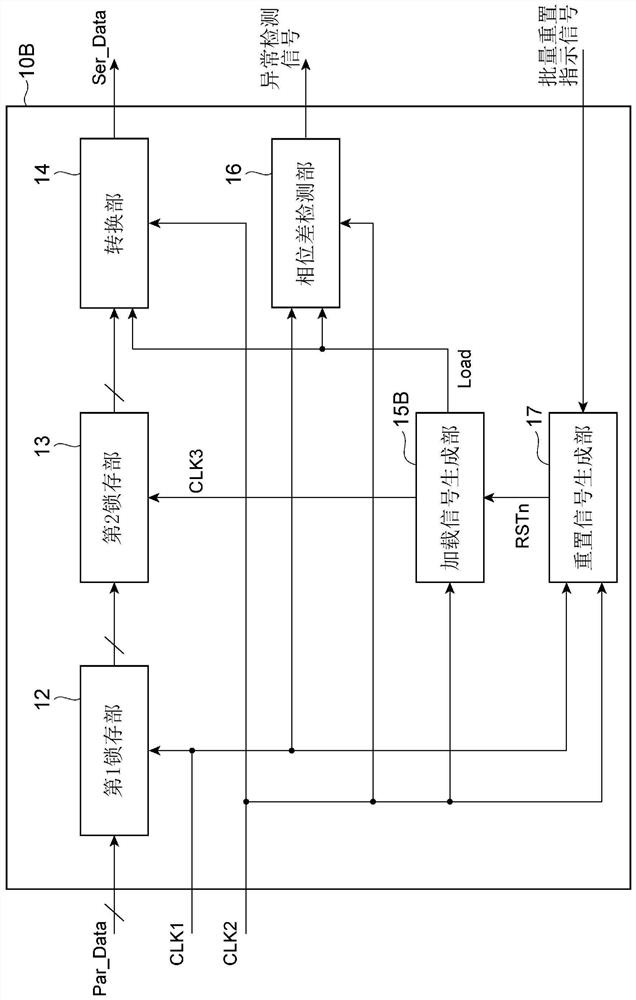

[0031] figure 1 It is a diagram showing the configuration of the multi-lane serializer device 1 . The multi-channel serializer device 1 includes a plurality of serializer circuits 10 1 ~10 N And the control unit 20. Each serializer circuit 10 n The parallel data Par_Data input in synchronization with the first clock CLK1 is serialized, and the serial data Ser_Data is output in synchronization with the second clock CLK2. N is an integer of 2 or more, and n is each integer of 1 or more and N or less. Each serializer circuit 10 n An abnormalit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com