Error correction circuit and method for operating the same

An error correction circuit and processing circuit technology, applied in the field of error correction circuits, can solve problems such as the increase of error leveling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Hereinafter, embodiments of the inventive concept may be described in detail and clearly to such an extent that those skilled in the art can easily realize the inventive concept.

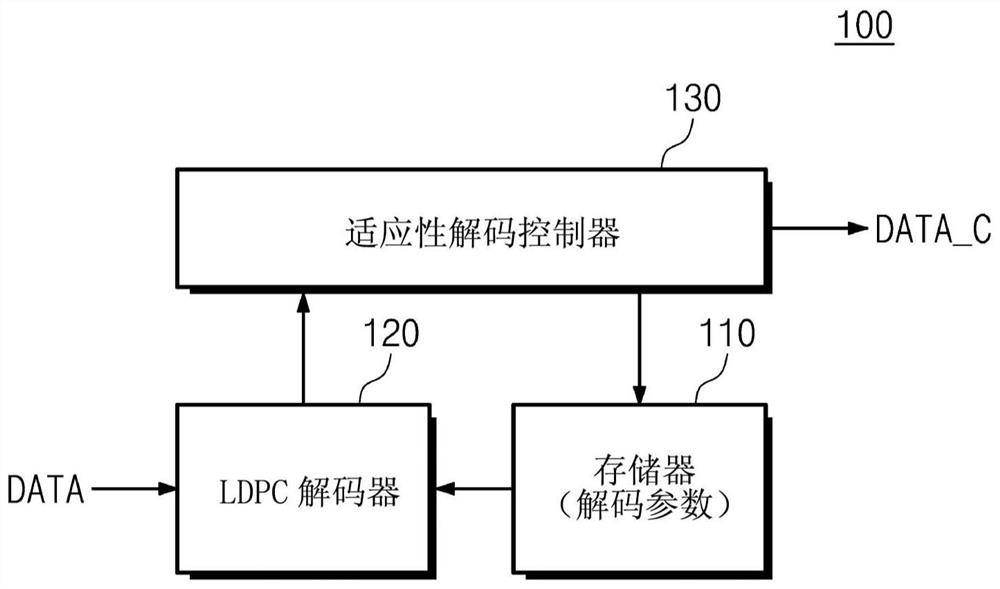

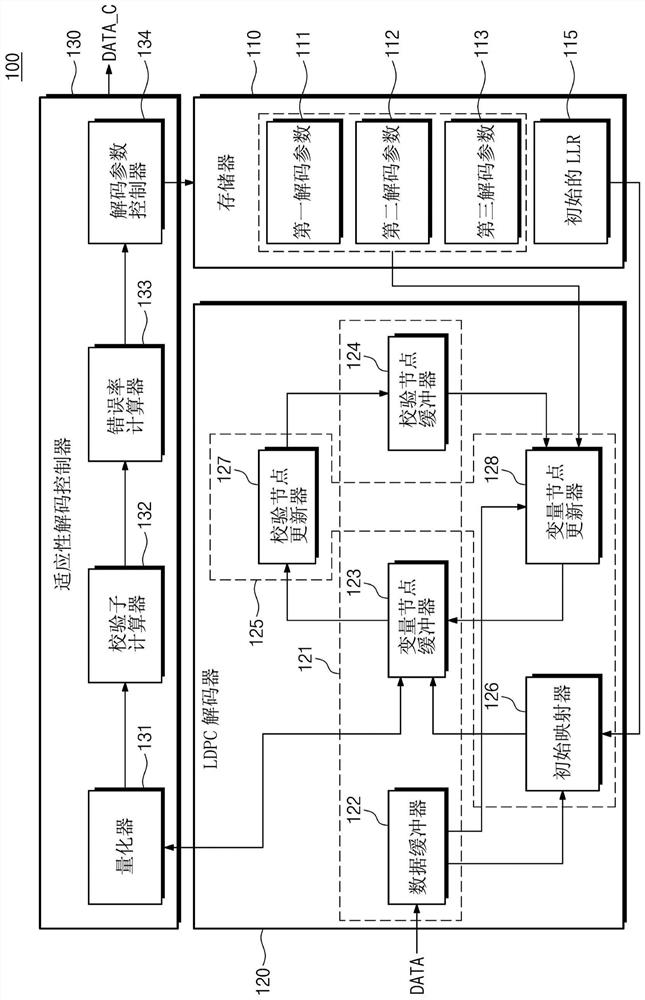

[0024] figure 1 is a block diagram illustrating an error correction circuit 100 according to some example embodiments of inventive concepts. refer to figure 1 , the error correction circuit 100 includes a memory 110 , a Low Density Parity Check (LDPC) decoder 120 and an adaptive decoding controller 130 . figure 1 Any or all of the elements may collectively be referred to as processing circuitry or processing circuitry, and may be implemented using hardware (eg, using hardware comprising CMOS logic gates). For example, LDPC decoder 120 and adaptive decoding controller 130 may be referred to as processing circuitry and / or processing circuitry.

[0025] The memory 110 may store decoding parameters used (eg, required) by the LDPC decoder 120 to perform error correction decoding (eg, LDPC decod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More