Clock legalization method based on heterogeneous FPGA layout

A clock and heterogeneous technology, applied in the field of VLSI physical design automation, can solve the problems of design complexity and scale increase, and achieve the effect of avoiding wiring failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

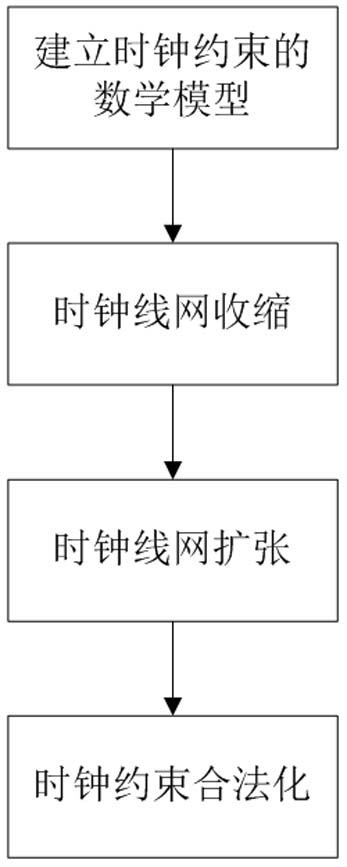

[0026] Such as figure 1 As shown, this embodiment provides a clock legalization method based on heterogeneous FPGA layout, including the following steps:

[0027] (1) Establish a mathematical model of clock constraints.

[0028] The specific implementation method of step (1) is:

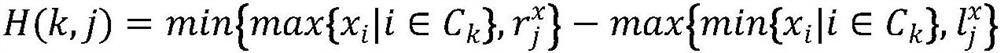

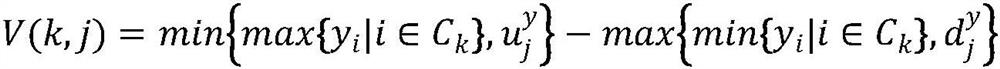

[0029] First of all, for the FPGA clock constraints, the following representation is made: with module v i The center coordinates of (x i ,y i ) to represent its position, let C k is the index set of blocks connected by clock k, namely {v i |i∈C k}. Let R be the set of clock regions, j∈R, let Indicates the x-coordinate of the left and right boundaries of clock region j. Indicates the y-coordinates of the upper and lower boundaries of clock region j. When the bounding box of the clock load overlaps with the clock region, the clock is located in t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More