In-chip multi-power system management circuit and method

A system management and power system technology, which is applied in the field of multi-power system management circuits in chips, can solve problems such as abnormal operation of chips, achieve precise control of delay time, avoid malfunctions, and eliminate malfunctions of chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

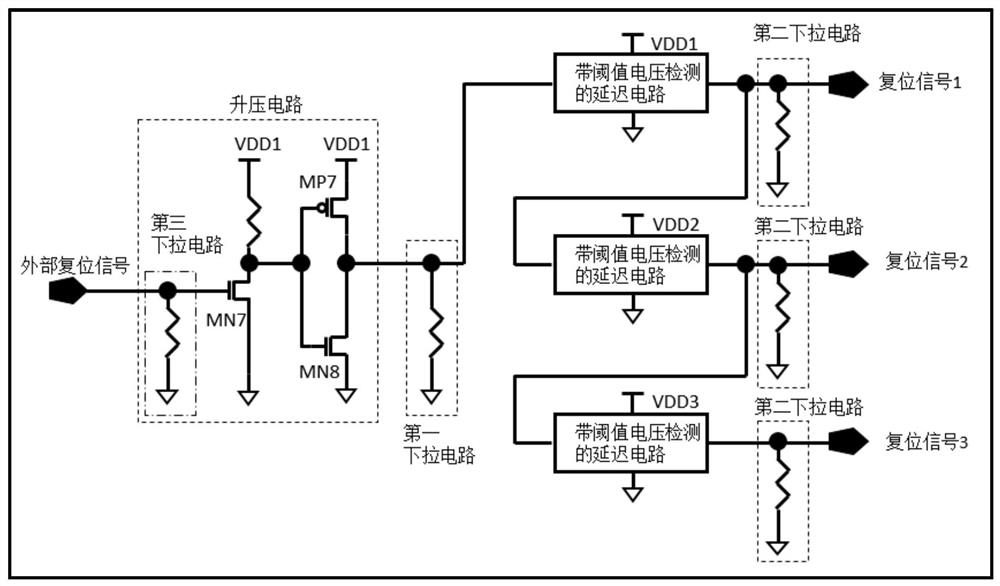

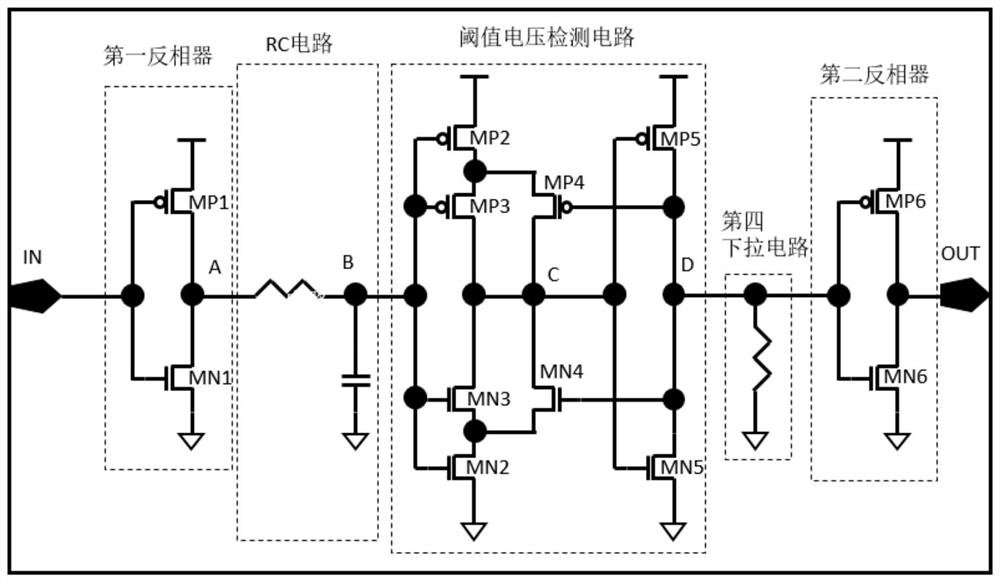

[0062] Such as Figure 1 to Figure 5 As shown, the present invention has a multi-power supply system management circuit in a chip, such as figure 1 As shown, the multi-power system management circuit provided in this embodiment includes a boost circuit, a first pull-down circuit, and three delay circuits, and the three delay circuits include a first delay circuit, a second delay circuit, and a third delay circuit. circuit;

[0063] One end of the boost circuit is connected to an external reset signal, the other end of the boost circuit is connected to a first pull-down circuit, and the first pull-down circuit is connected to the input end of the first delay circuit, and the output of the first delay circuit terminal outputs reset signal 1; the output terminal of the first delay circuit is also connected to the second delay circuit, and the output terminal of the second delay circuit outputs reset signal 2; the output terminal of the third delay circuit outputs reset signal 3;...

Embodiment 2

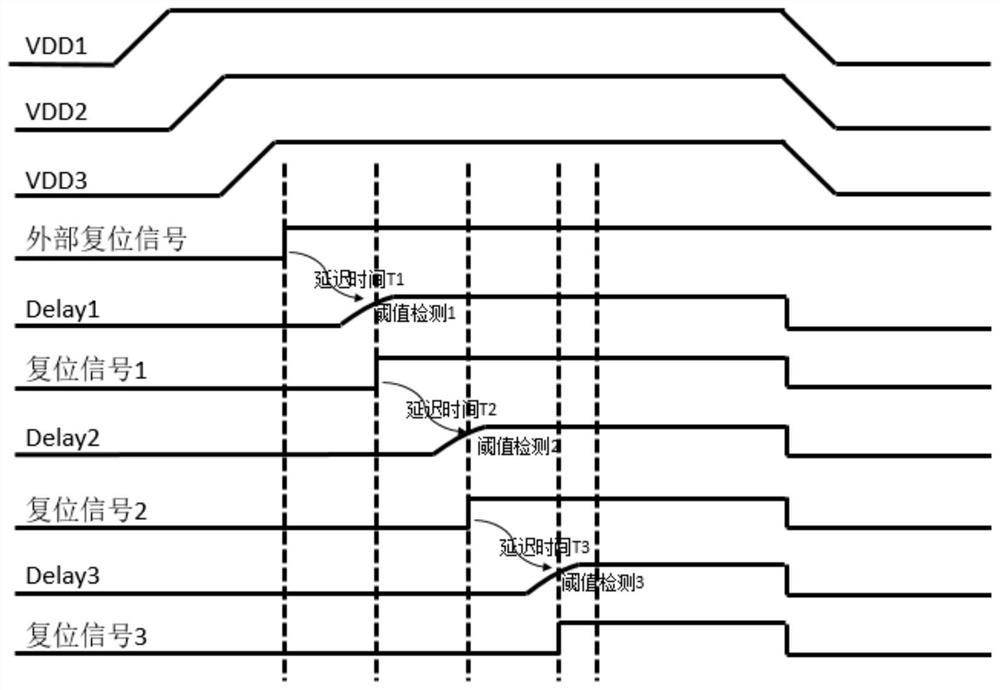

[0097] The difference between this embodiment and Embodiment 1 is that this embodiment provides an on-chip multi-power system management method, which is applied to the on-chip multi-power system management circuit described in Embodiment 1, and the method includes the above Three stages: before power-on, power-on, and power-off;

[0098] In the pre-power-on stage, the method includes:

[0099] When the external reset signal is in a steady state or in an unsteady state, the voltage of the external reset signal is fixed at a low potential of 0V through the third pull-down circuit, and the booster circuit does not work at this time;

[0100] The pull-down circuit can be implemented in various ways such as setting a resistor structure and setting a MOS tube.

[0101] The function of the pull-down circuit is to fix the voltage of the external reset signal at a low potential through the pull-down circuit, so as to prevent the chip from malfunctioning (that is, causing the chip to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More