Verification platform and verification method of system-on-chip

A system-level chip and verification platform technology, applied in the field of system-level chip verification platform, can solve the problems of delaying the start time of verification, affecting the verification progress, and unable to reuse software test programs, so as to reduce complexity and shorten the verification cycle Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The various aspects and examples of the present application will now be described. The following description provides specific details for thorough understanding and implementation of these examples. However, those skilled in the art will appreciate that this application can be practiced without many of these details.

[0028] Additionally, some well-known structures or functions may not be shown in detail, in order to concise, and avoid unnecessary blurring description.

[0029] Some concepts:

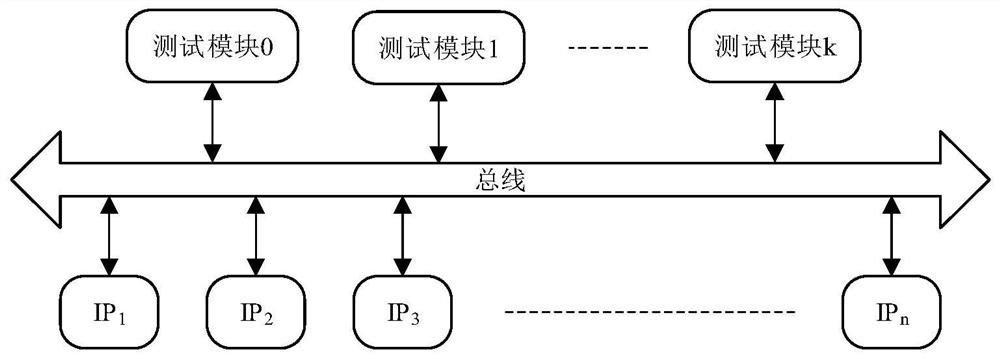

[0030] IP kernel module: IP (Intellectual Property) kernel module is a pre-designed component that has been verified with a certain determination function, which is generally integrated with chip design, and multiple IP kernel modules are generally integrated in SOC.

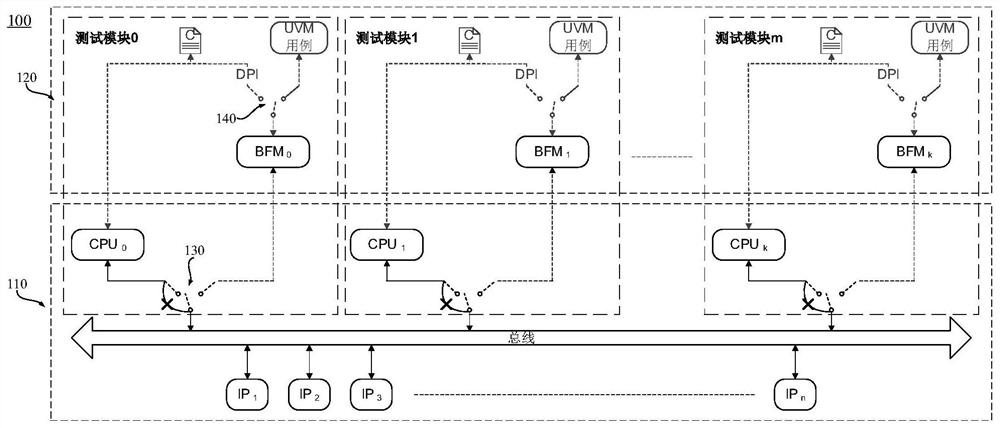

[0031] BFM: Bus Function Model, Bus Function Model.

[0032] DIRECT Program Interface, direct programming interface.

[0033] VIP: Verification IP, verify the IP module.

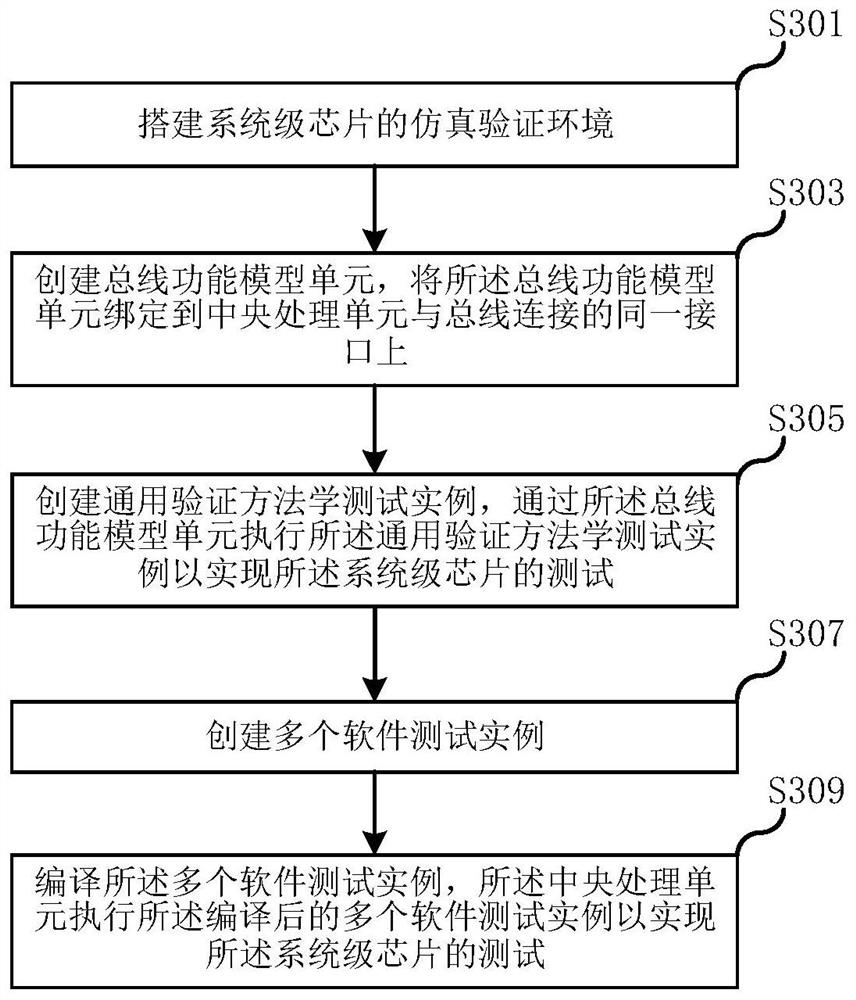

[0034] In order to make the purpose, technic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More