Superconducting quantum computing chip layout generation method and device

A computing chip and superconducting quantum technology, applied in the field of quantum computing, can solve the problems of human resource consumption, high consumption and high use cost, and achieve the effect of avoiding unnecessary waste, reducing use cost, and reducing construction complexity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to make the purpose, technical solution and advantages of the present application clearer, the technical solution of the present application will be clearly and completely described below in conjunction with specific embodiments of the present application and corresponding drawings. Apparently, the described embodiments are only some of the embodiments of the present application, rather than all the embodiments. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protection of this application.

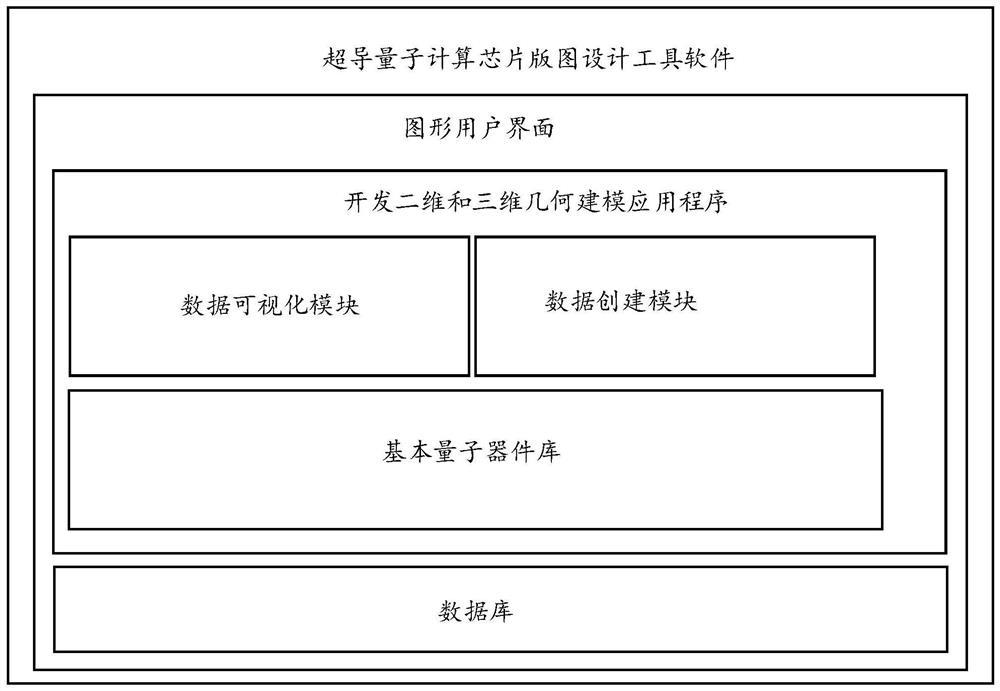

[0027] At present, researchers need to rely on chip layout design tools to make chip layouts. Since the superconducting quantum chip is a superconducting circuit physical system based on the Josephson junction, its preparation process is highly compatible with the existing semiconductor micromachining process. Therefore, researchers can still design s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More