Gate drive circuit and display panel

A gate drive circuit and capacitor adjustment technology, applied to static indicators, instruments, etc., can solve problems such as horizontal bright and dark lines on the display interface, clock signal resistance and capacitance load differences, and achieve the effect of facilitating design and increasing frame width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

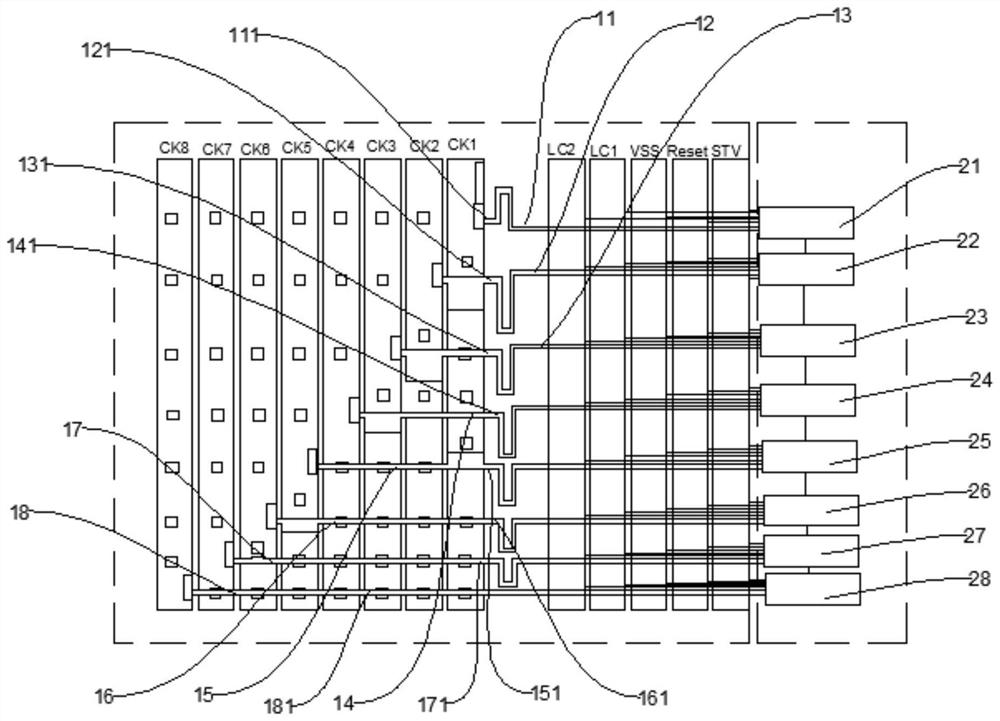

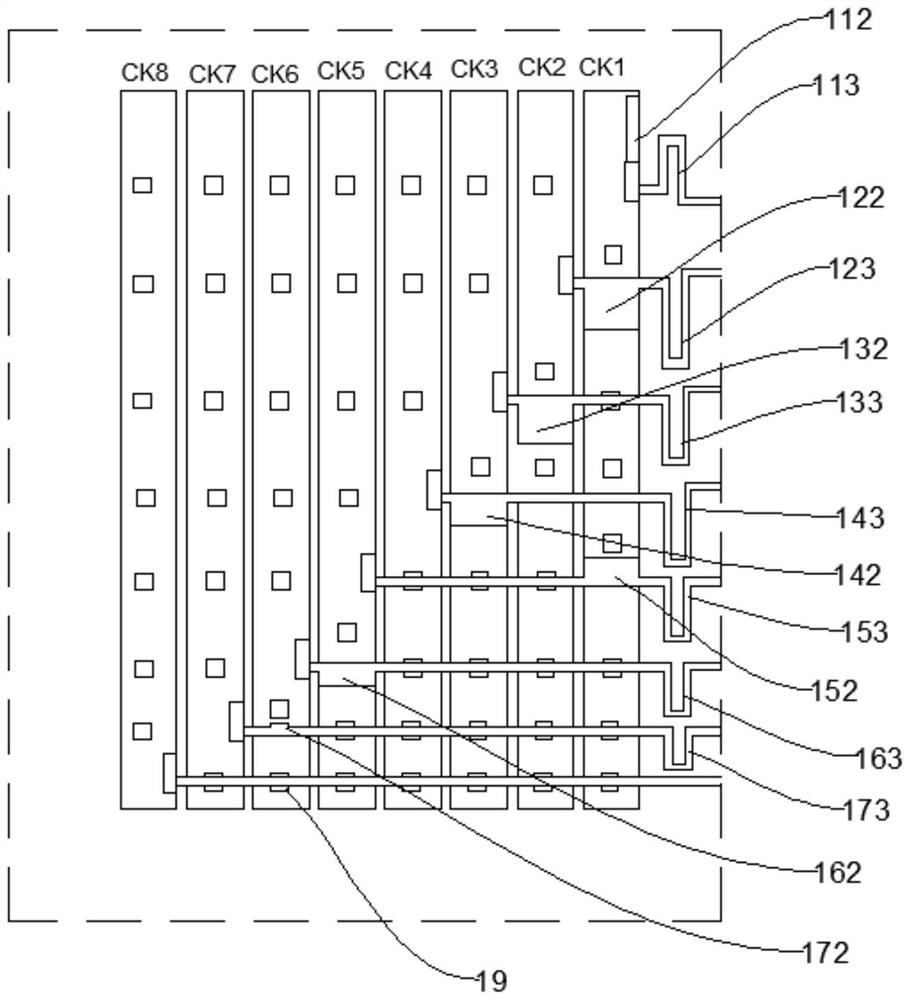

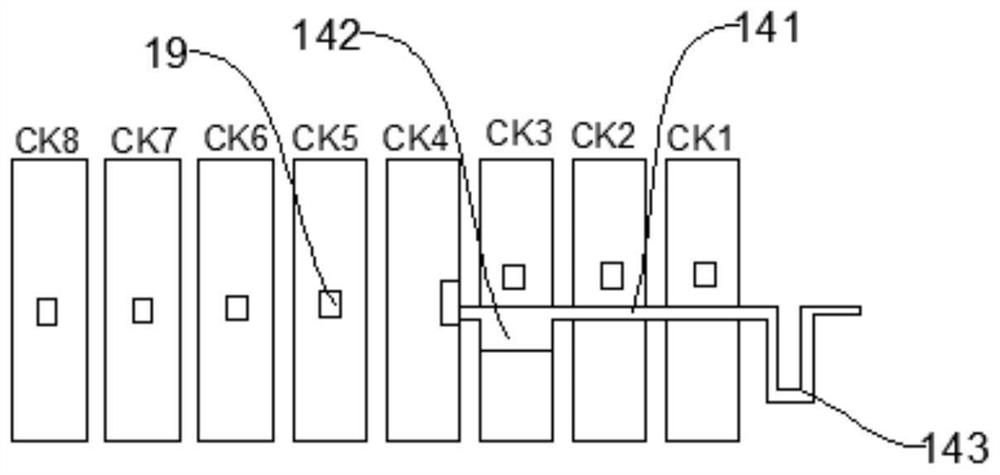

[0060] See figure 1 , figure 1 It is a structural diagram of a gate driving circuit according to the first embodiment. This embodiment provides a gate driving circuit, which includes a plurality of cascaded shift register units, n clock signal lines and control lines. The shift register unit has a clock signal terminal, and each shift register unit is correspondingly connected to a clock signal line through a connection line. Specifically, the connection line includes a conduction section, the first end of the conduction section is connected to the clock signal line, the second end of the conduction section is connected to the clock signal end of the shift register unit, the clock signal is transmitted to the shift register unit through the conduction section, n is a positive integer greater than 1, such as 2, 3, 4, 5, and 6.

[0061] Here, a plurality of shift register units can be arranged in sequence along the first direction, each shift register unit is a first-level ou...

Embodiment 2

[0094] see Image 6 , Image 6 It is a schematic structural diagram of a display panel according to the second embodiment. In the second embodiment, a display panel is also provided.

[0095] The display panel includes an effective display area 200 and a non-display area, the non-display area includes a gate drive circuit 100, the effective display area 200 includes a plurality of scan lines 300, and the gate drive circuit 100 includes a plurality of shift register units , the output end of any shift register unit provides a gate driving signal for at least one scan line 300 . Since the display panel of this embodiment has the gate driving circuit in the above embodiment, it has all the beneficial effects of the above gate driving circuit, which will not be repeated here.

[0096] In addition, the terms "first" and "second" are only used for descriptive purposes, and should not be construed as indicating or implying relative importance or implying the number of indicated te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More