Patents

Literature

51results about How to "Won't increase the width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

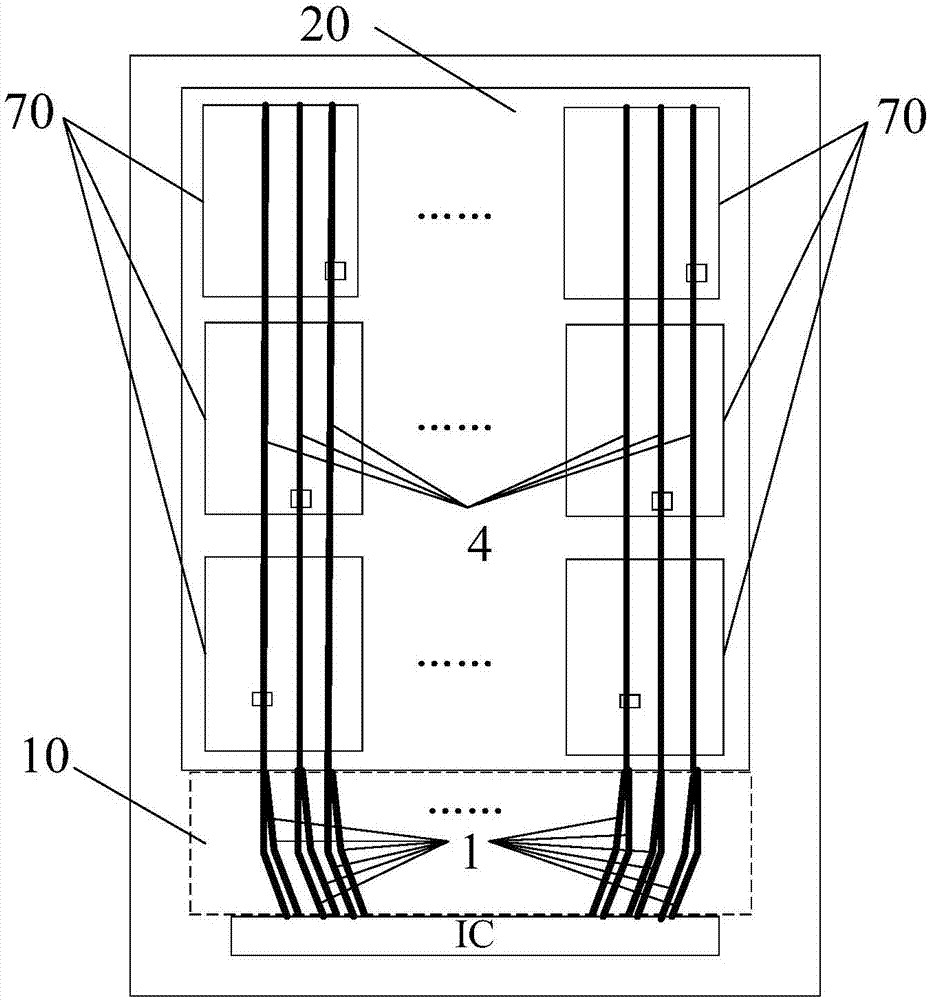

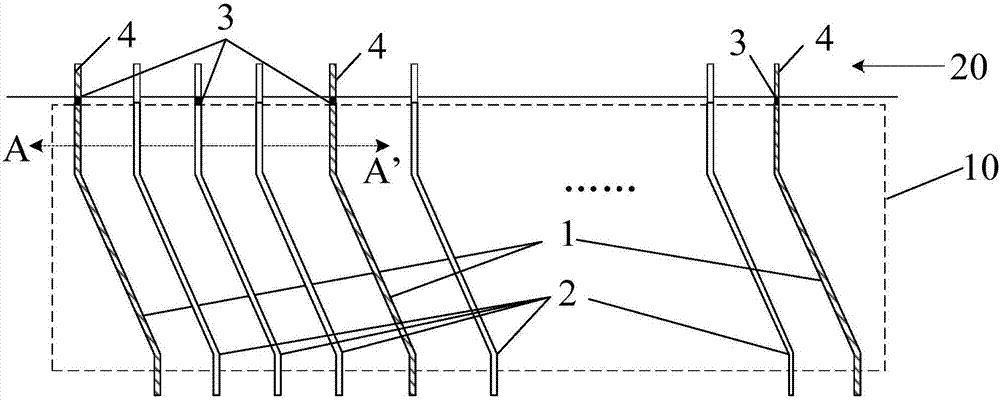

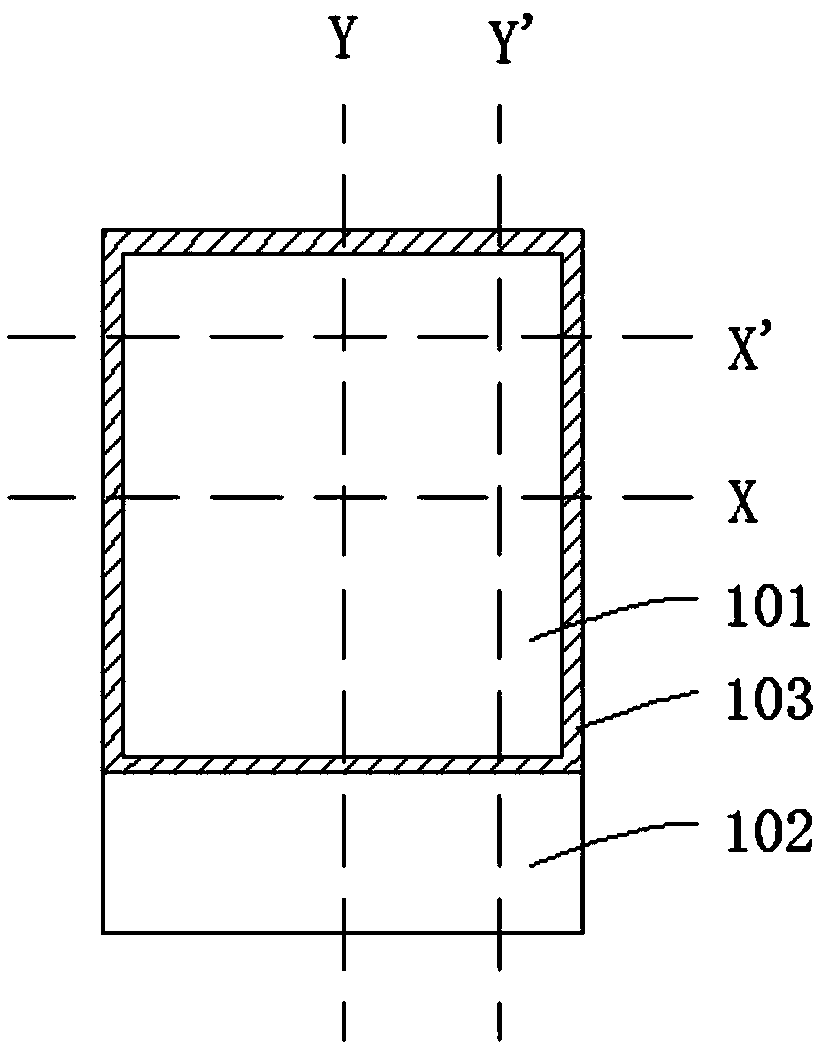

Display module, display device and spliced screen

ActiveCN111653207AImprove the display effectMake it collapsibleStatic indicating devicesNon-linear opticsComputer hardwareDisplay device

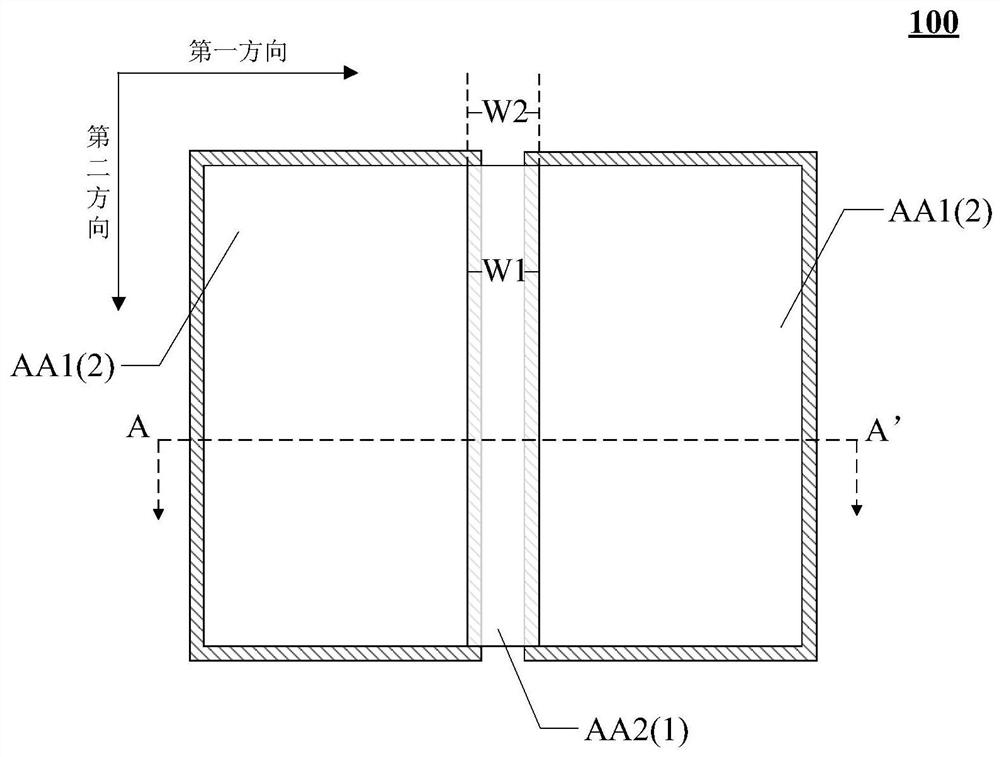

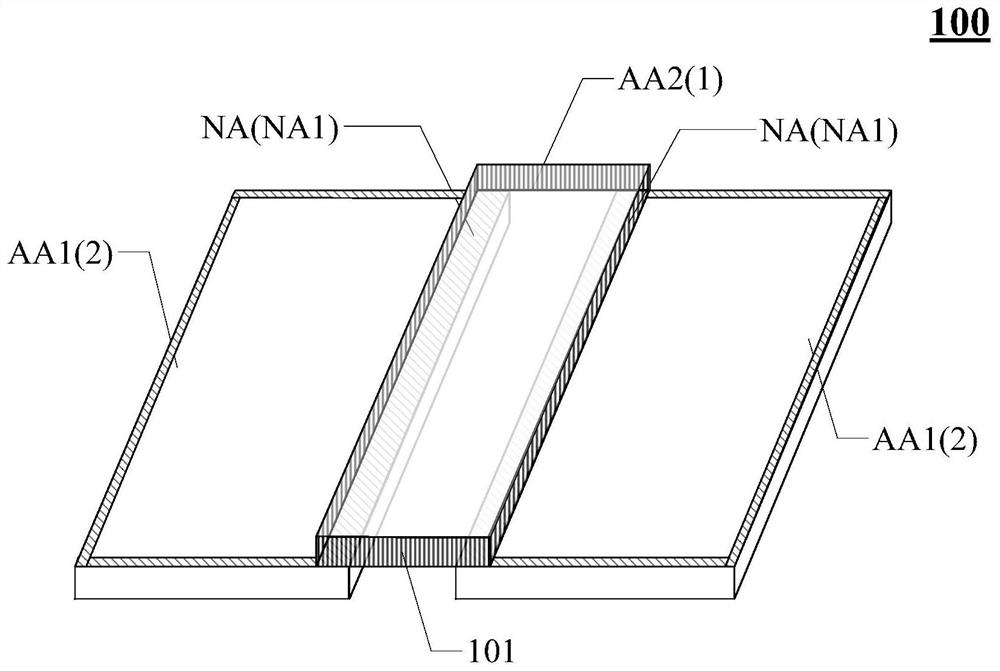

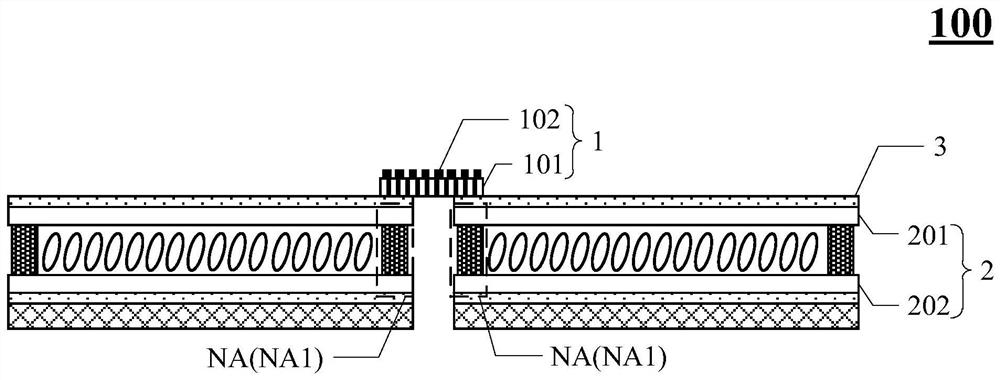

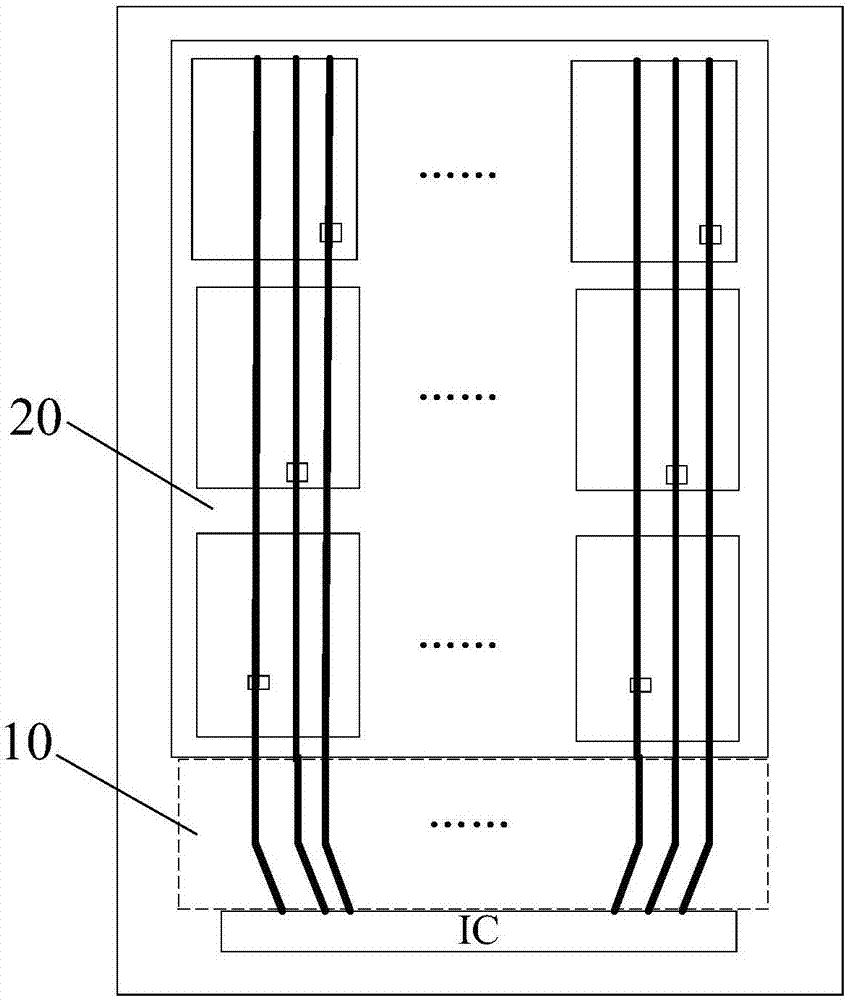

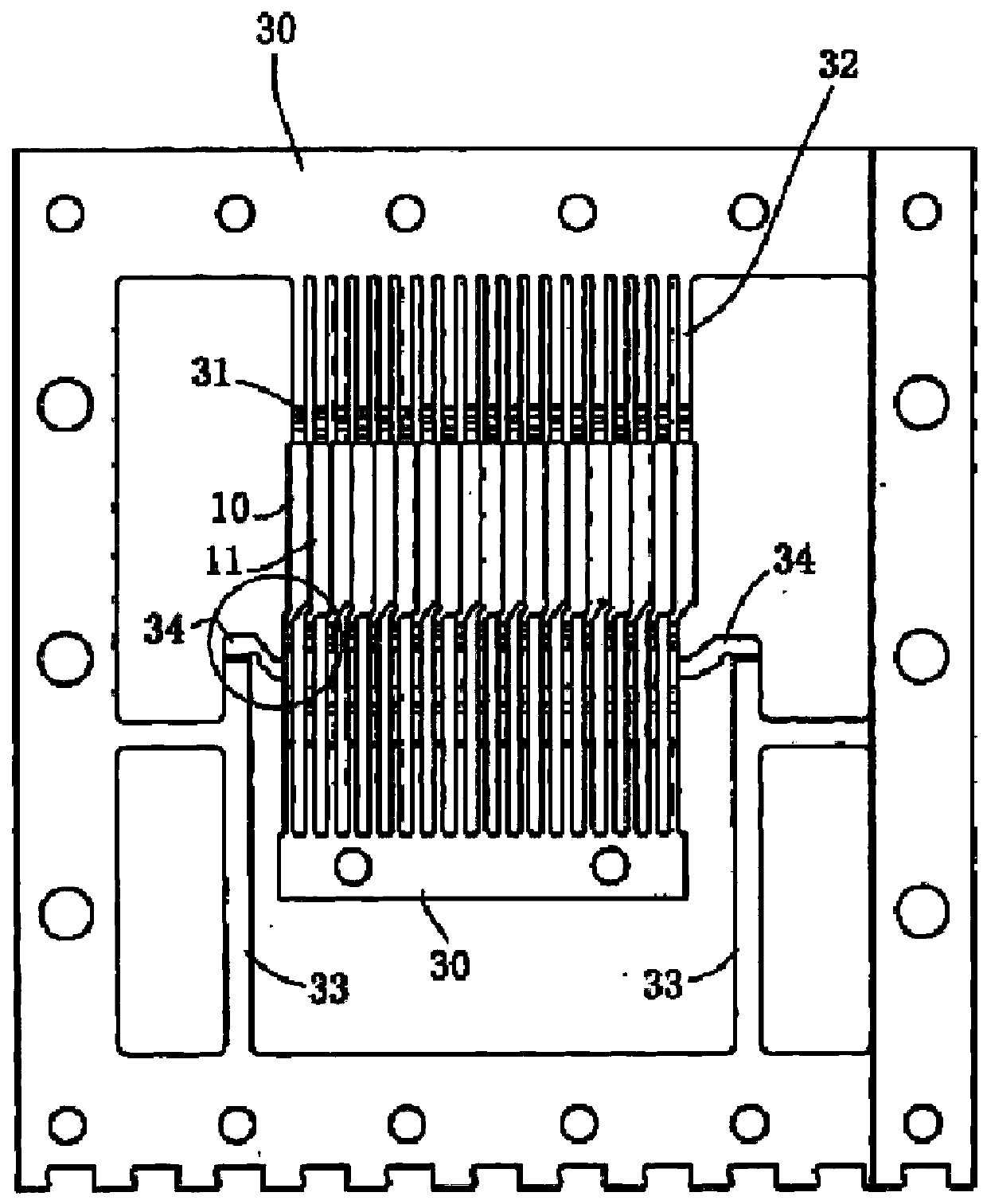

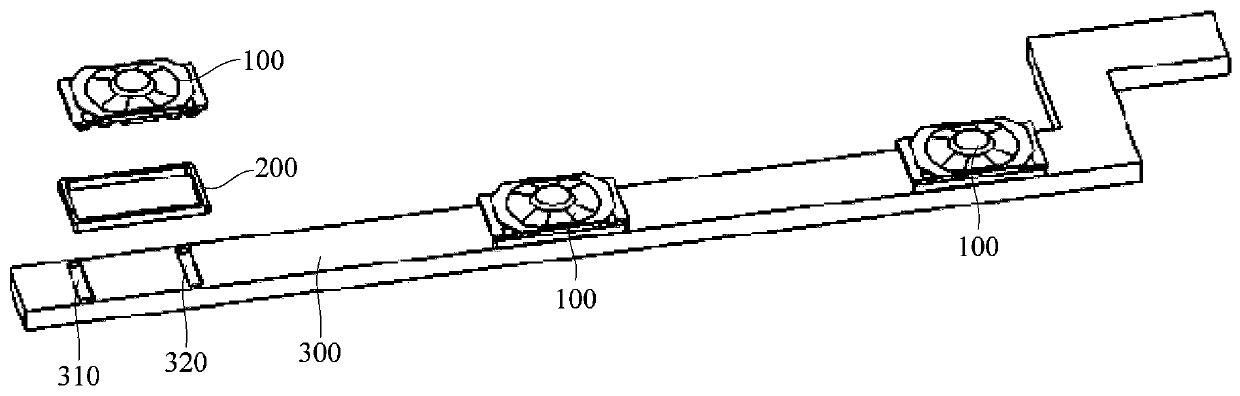

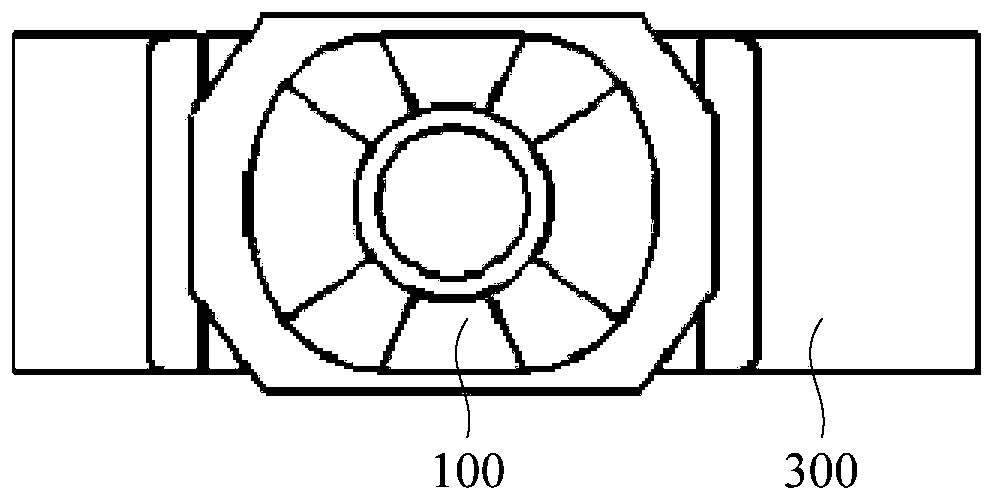

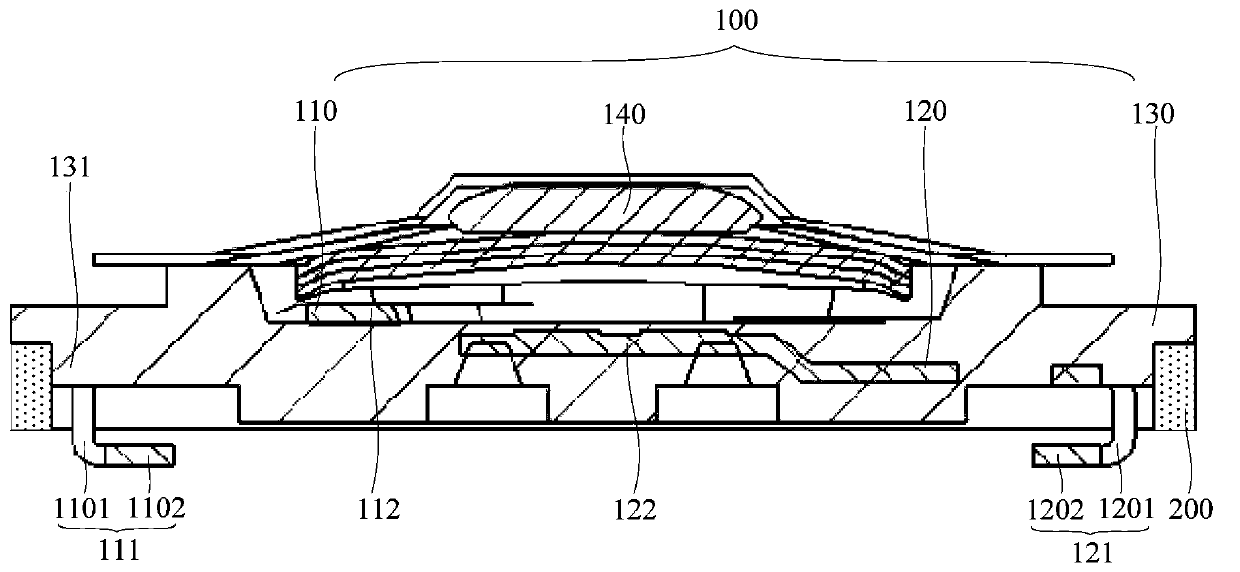

The invention discloses a display module, a display device and a spliced screen, and relates to the technical field of display. The display module comprises at least two main display areas and a spliced display area, and at least part of the spliced display area is located between adjacent two main display areas in the direction parallel to the light-emitting surface of the display module; in therange of the spliced display area, the display module comprises a first display panel in the direction perpendicular to the light-emitting surface of the display module, the first display panel comprises a first substrate, a driving circuit and a plurality of light-emitting devices, the driving circuit and the light-emitting devices are arranged on the first substrate, and the driving circuit is used for driving the light-emitting devices to emit light. By filling at least part of the first display panel between the adjacent two main display areas, the area between the two main display areas has a display function, splicing seams between the main display areas can be weakened or eliminated, and therefore module display of any size is achieved.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

Array substrate, touch panel and touch device

ActiveCN106959783ALower total resistanceReduce signal delayInput/output processes for data processingTouch panelElectricity

Embodiments of the present invention provide an array substrate, a touch panel and a touch device. In the embodiments of the present invention, the array substrate comprises a touch electrode layer, the touch electrode layer comprises a plurality of touch electrode units, and each touch electrode unit is electrically connected with at least one first touch signal line in a display area; at least part of the first touch signal lines are electrically connected with a plurality of second touch signal lines located in the sector; and a plurality of second touch signal lines are distributed in at least two metal layers. The technical scheme provided by the embodiments of the present invention can solve the problem of the display effect and touch sensitivity influenced by the large resistance of the touch signal line in the prior art to a certain extent.

Owner:SHANGHAI AVIC OPTOELECTRONICS

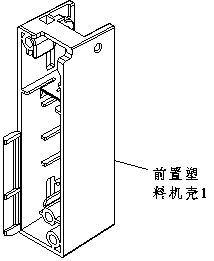

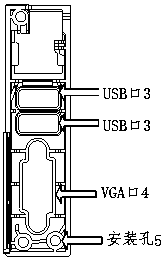

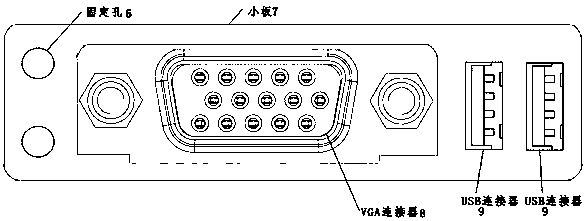

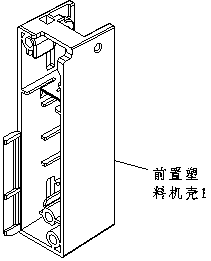

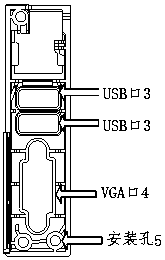

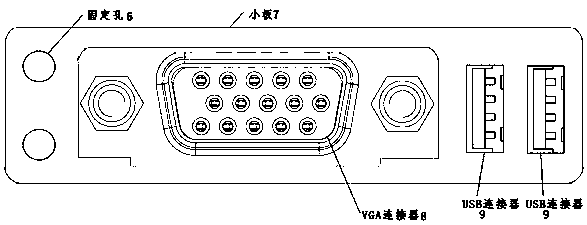

Server chassis capable of decreasing radiation and server

ActiveCN107635389AAvoid interferenceWon't increase the widthMagnetic/electric field screeningSupport structure mountingEngineeringUSB

The present invention relates to a server chassis capable of decreasing radiation and a server. The server chassis is characterized in that the server chassis includes a chassis, a small board and a main board; the small board is provided with a VGA connector and USB connectors; the chassis comprises a metal case and a front plastic case; a VGA opening for matching the VGA connector on the small board, USB openings for matching the USB connectors on the small board, and mounting holes are formed in the front plastic case; conductive fixing components can be plugged into the mounting holes in amatched manner, so that the small board can be installed on the front plastic case; fixing holes corresponding to the mounting holes of the front plastic case are formed in the small board; the conductive fixing components are plugged into the mounting holes and the fixing holes, so that the small board can be installed on the front plastic case; the front plastic case is subjected to conductivespraying treatment; and the metal case is fixedly connected with the front plastic case.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

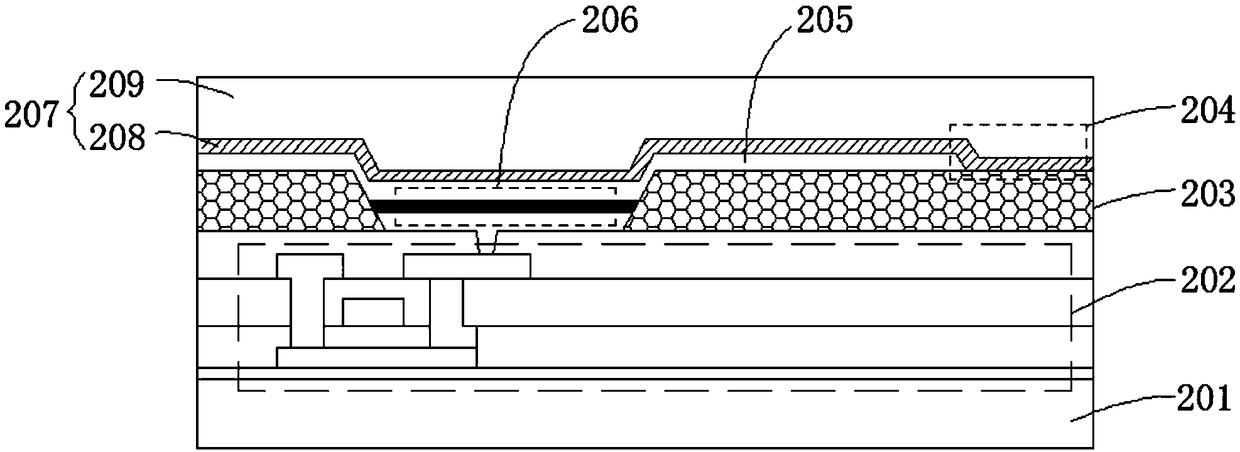

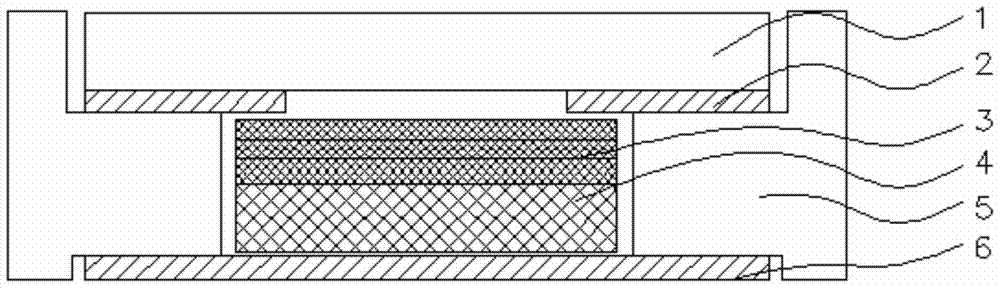

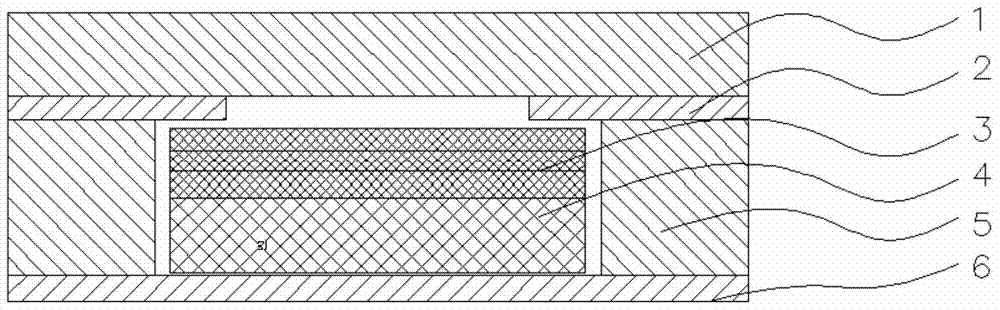

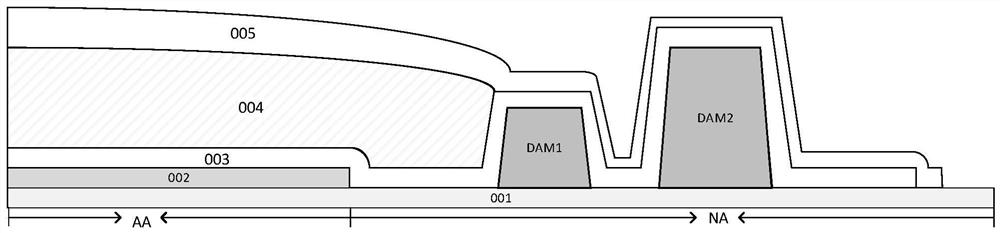

OLED display panel and encapsulation method thereof

InactiveCN108963104AImprove packaging effectExtend your lifeSolid-state devicesSemiconductor/solid-state device manufacturingInorganic materialsLight emitting device

The present invention provides an OLED display panel and an encapsulation method thereof. The OLED display panel includes a substrate, a thin film transistor layer formed on the substrate, an OLED light emitting layer prepared on the thin film transistor layer, and an encapsulation layer prepared on the OLED light emitting layer, wherein the OLED light emitting layer includes an OLED light emitting device, and the encapsulation layer includes a plurality of inorganic layers and organic layers which are alternately disposed, wherein at least one of the inorganic layers in the encapsulation layer contacts at least one inorganic material film layer in the OLED light emitting layer or the thin film transistor layer through a reserved region, so that an enhancement encapsulation enclosing ringat least surrounding the OLED light emitting device can be formed so as to encapsulate the OLED display panel.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

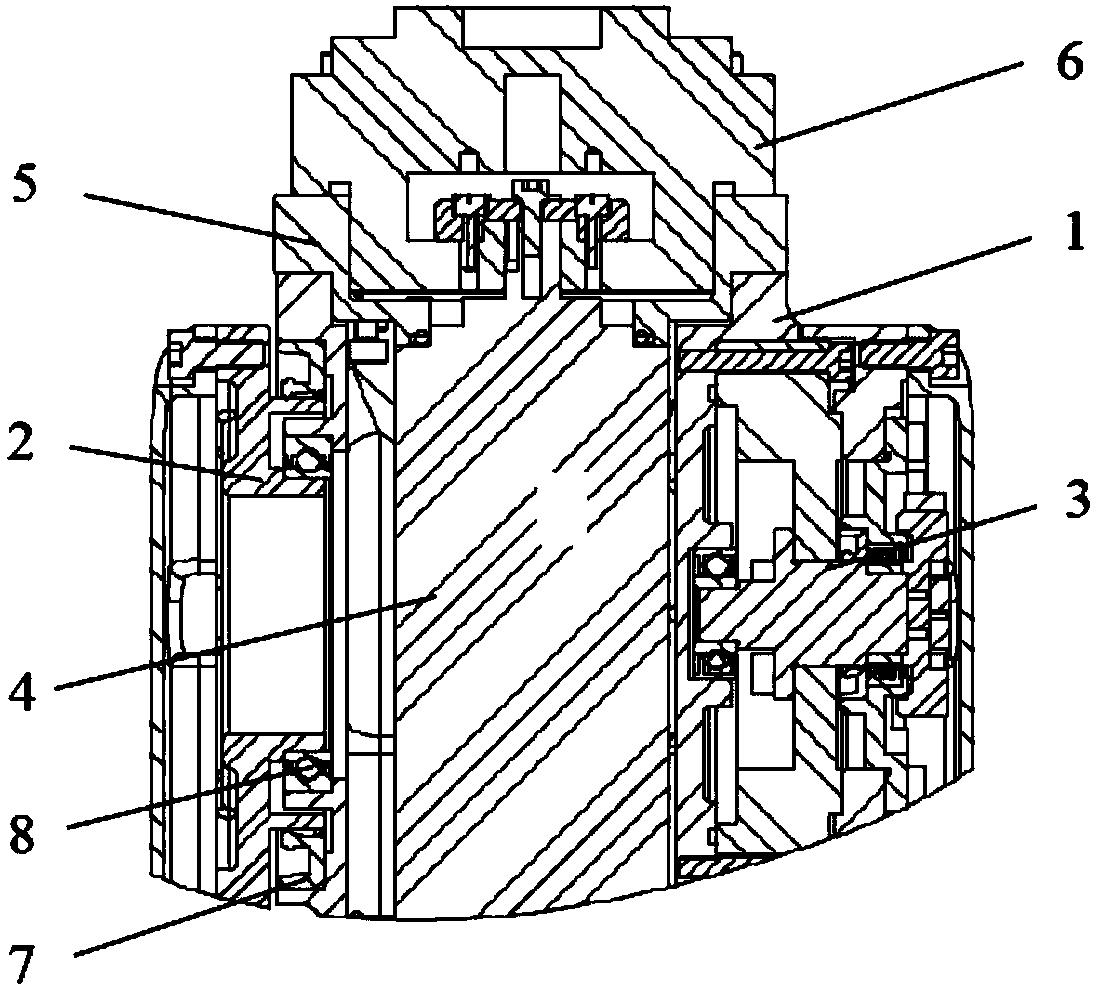

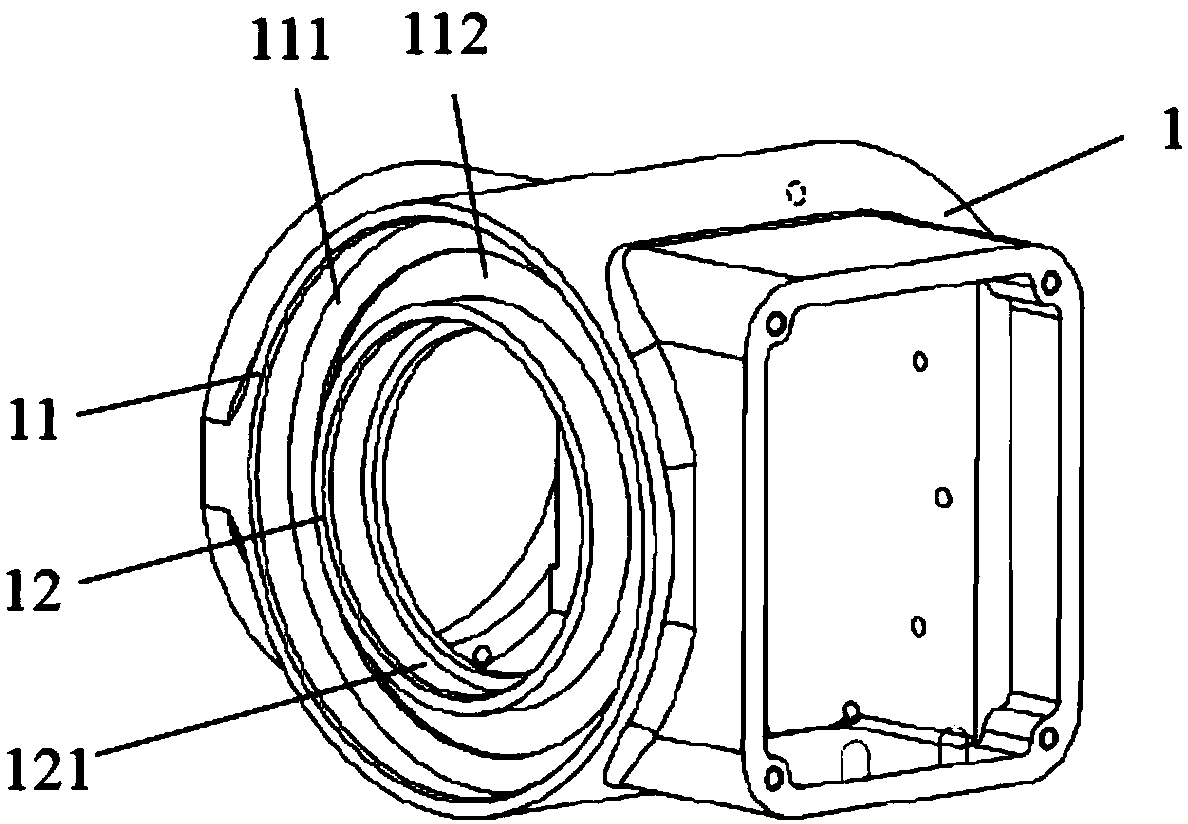

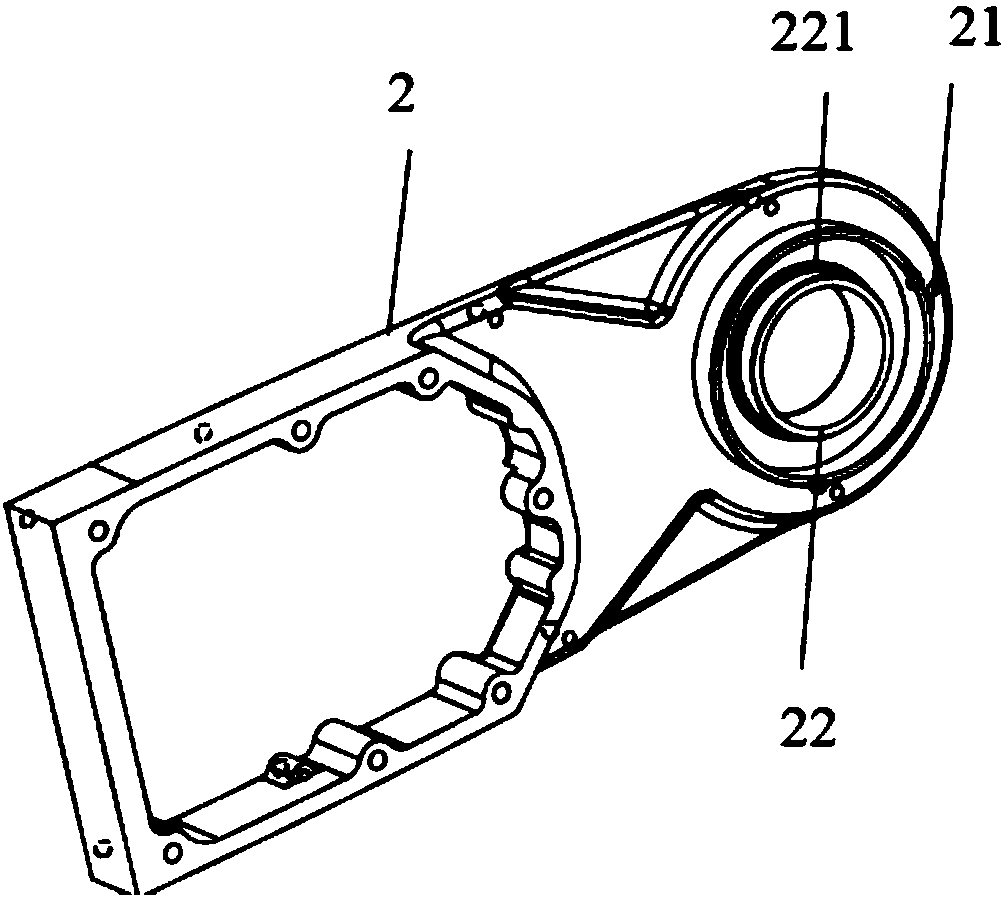

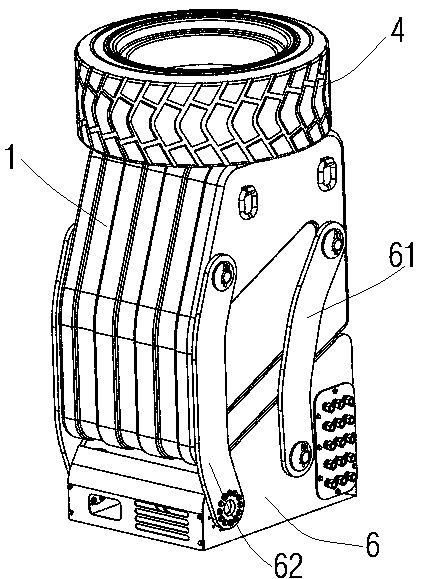

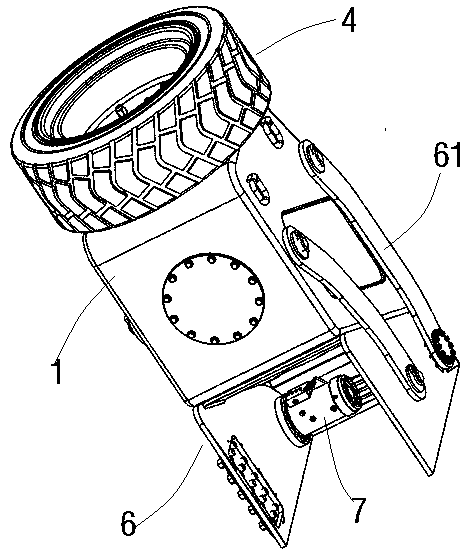

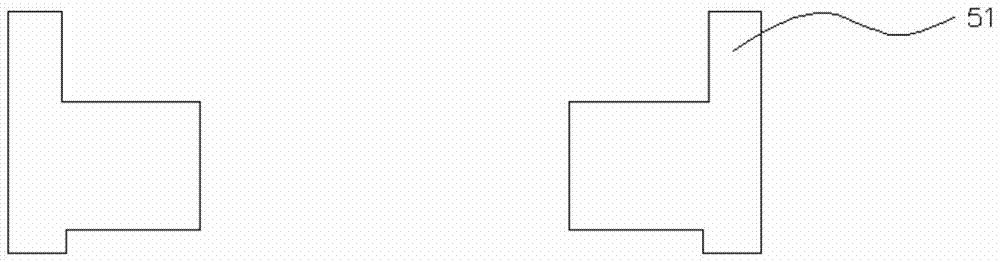

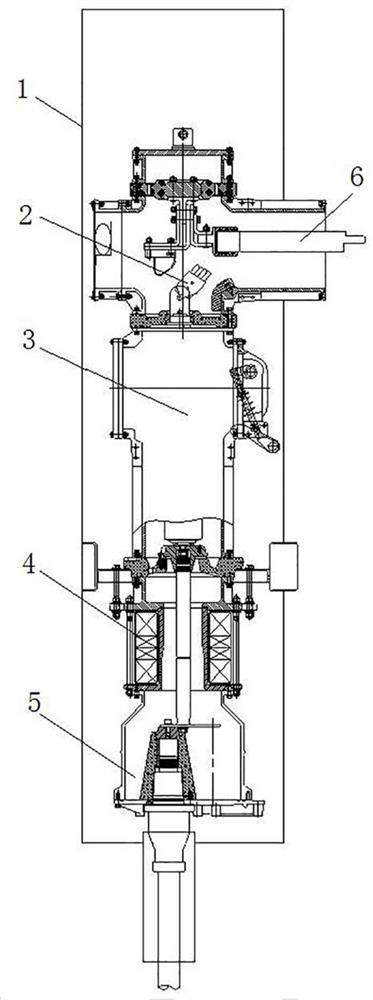

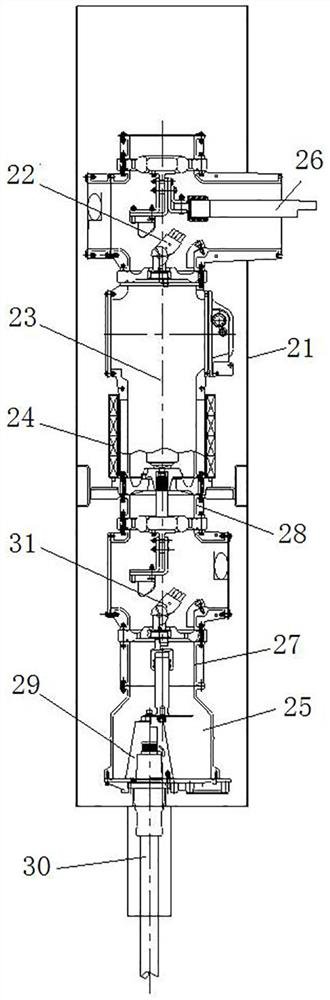

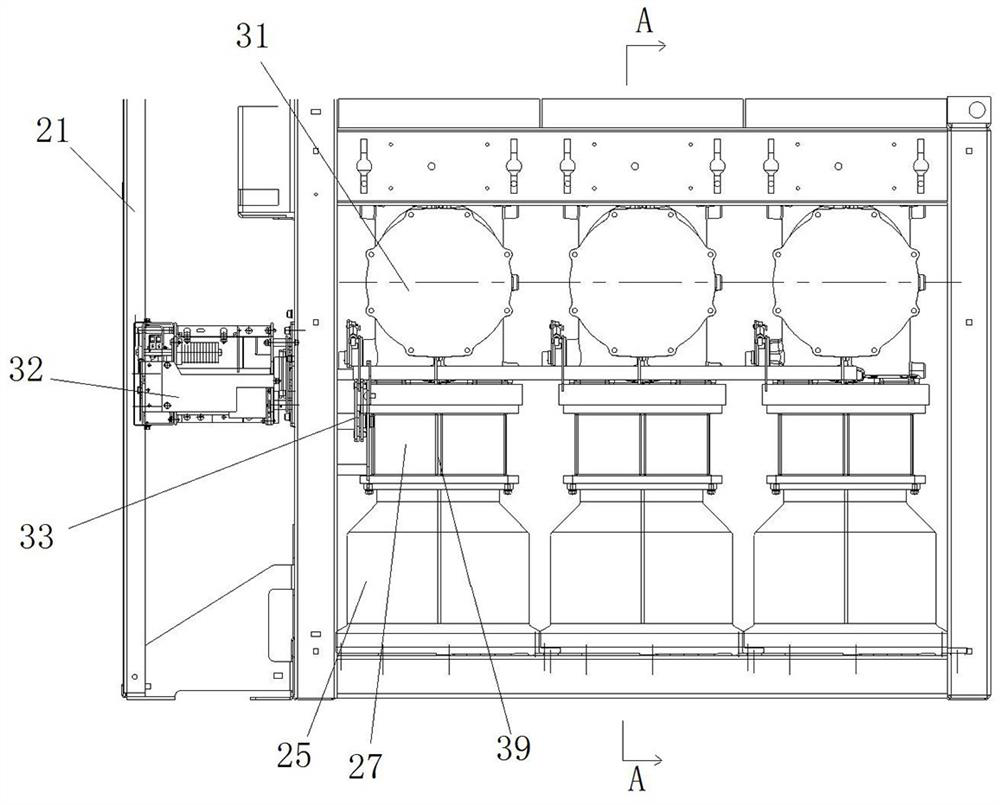

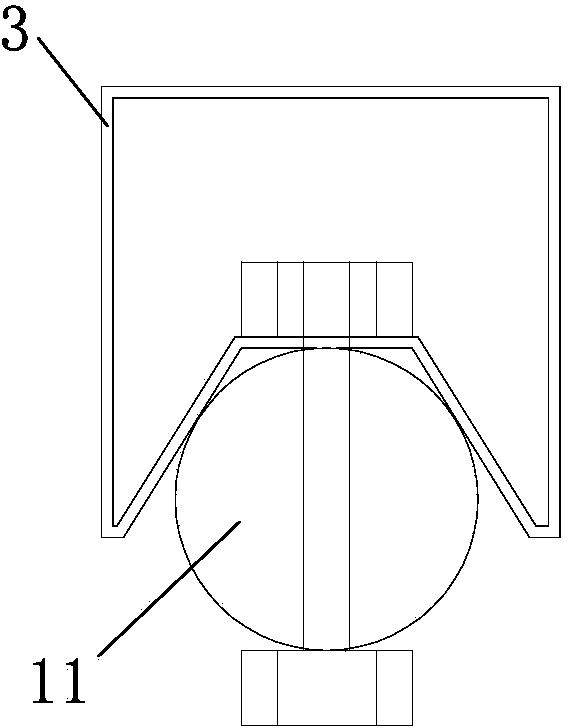

Industrial robot wrist

The invention discloses an industrial robot wrist including a wrist body and a wrist connecting body. The wrist body and the wrist connecting body are connected and positioned by a bearing, a gap labyrinth structure is formed at the junction of the wrist body and the wrist connecting body, and the gap labyrinth structure is located outside the bearing. The structure of the wrist of an industrial robot is designed rationally, double sealing on the robot wrist position is achieved by means of an oil seal and the gap labyrinth seal structure, and the protection level of the robot wrist is significantly improved; at the same time, since the oil seal and the bearing are almost on the same mounting surface, the width of the robot wrist is not increased, not only is the rigidity of the robot wrist ensured, but also it is ensured that the size of the robot wrist position is more compact, and more application fields can be met; and the sealing performance is high, the maintenance cost of the robot wrist is reduced, and the service life of a robot is prolonged.

Owner:EFORT INTELLIGENT EQUIP CO LTD

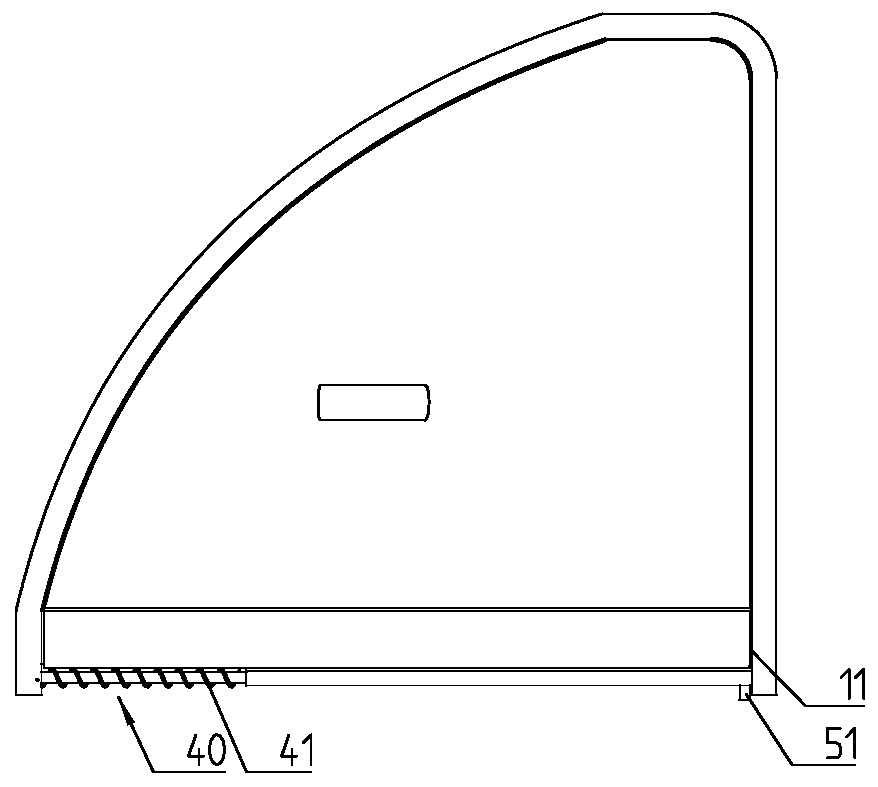

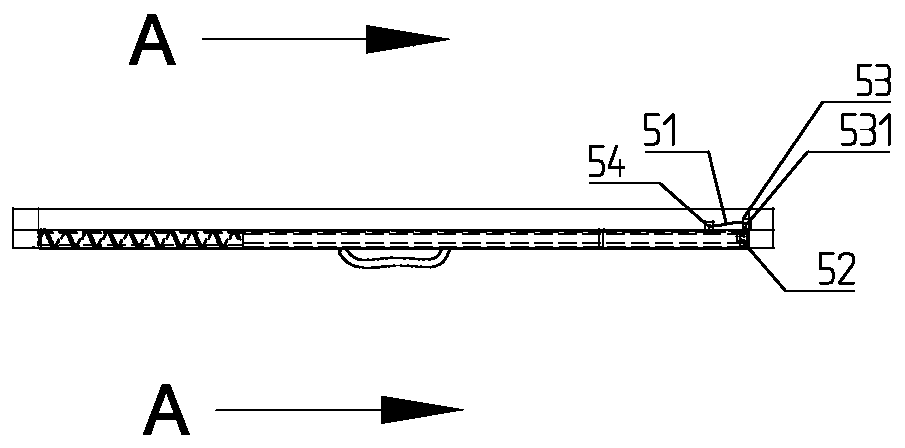

Hidden automobile pedal plate

PendingCN109823271AWon't increase the widthWill not reduce heightSteps arrangementCar doorEngineering

The invention discloses a hidden automobile pedal plate. The pedal plate is located below an automobile door. The pedal plate comprises a pedal plate containing cavity, an automobile body formed belowthe automobile door, a pedal plate body located inside the pedal plate containing cavity and pivoted into the pedal plate containing cavity, a linkage mechanism comprising the power input end and thepower output end, and a reset mechanism acting on the pedal plate body, wherein the power input end is connected with the automobile door, the power output end is connected with the pedal plate body,after the automobile door is opened, the linkage mechanism is driven to force the pedal plate body to be turned over to the horizontal position towards the exterior of the pedal plate containing cavity, and tendency force is applied to the pedal plate body constantly. Due to the tendency force, the pedal plate body is forced to turned over towards the interior of the pedal plate containing cavity.

Owner:李玉柱

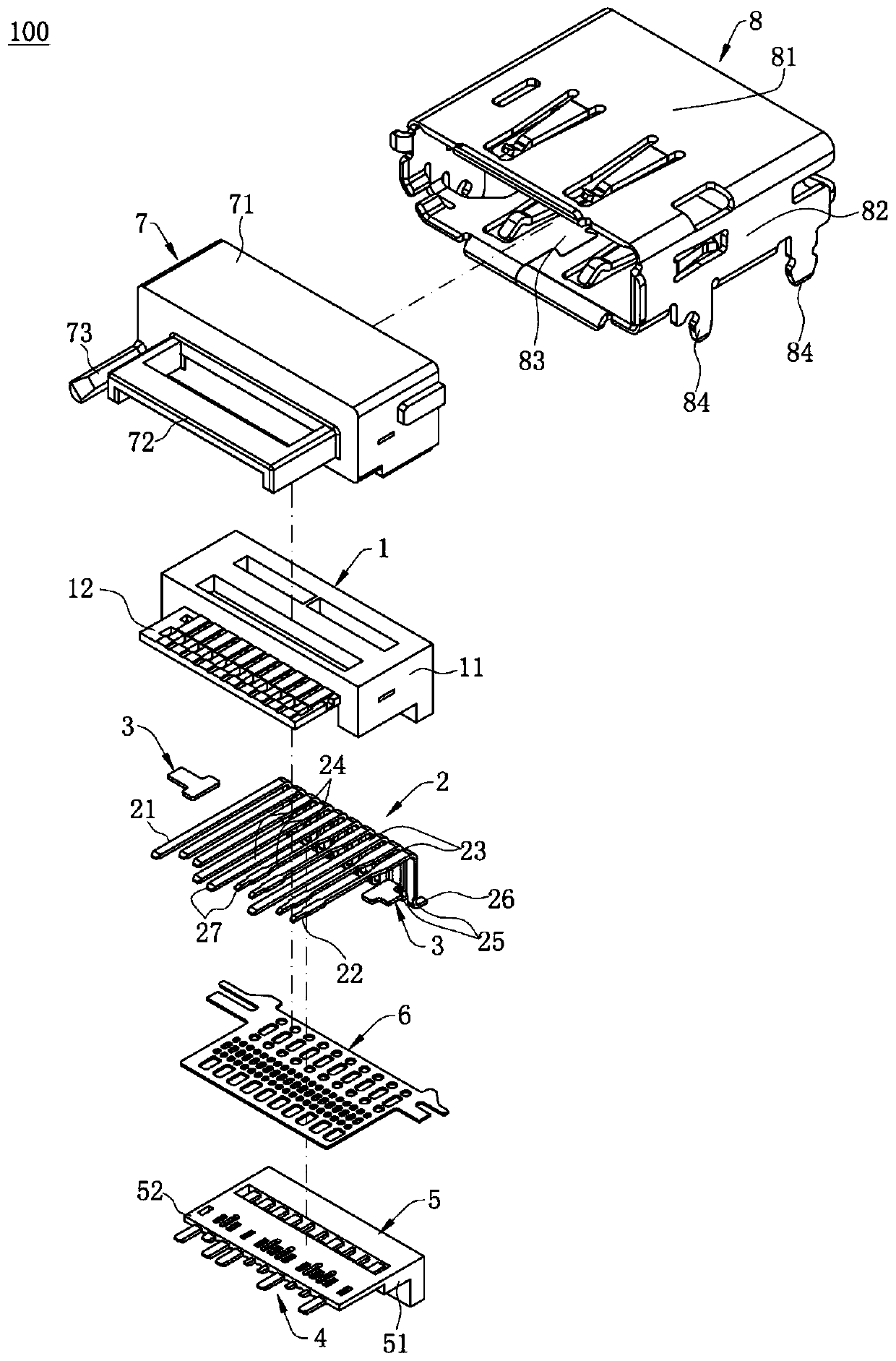

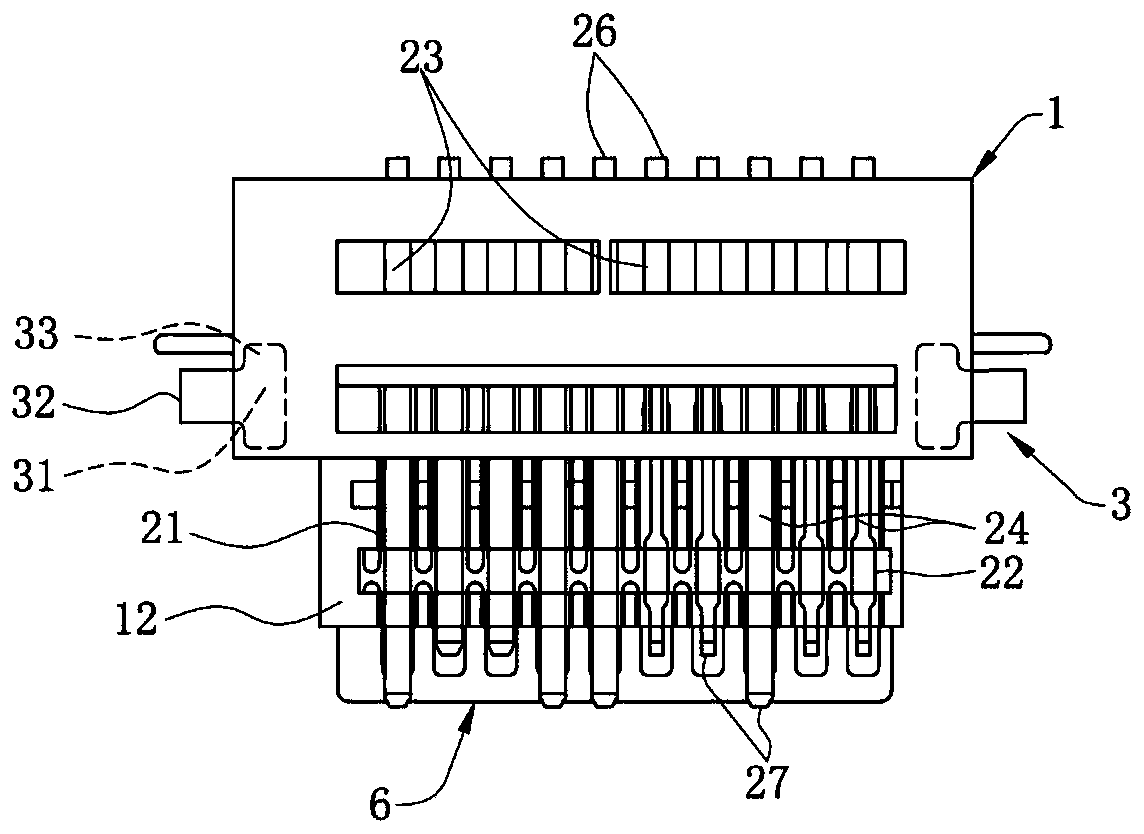

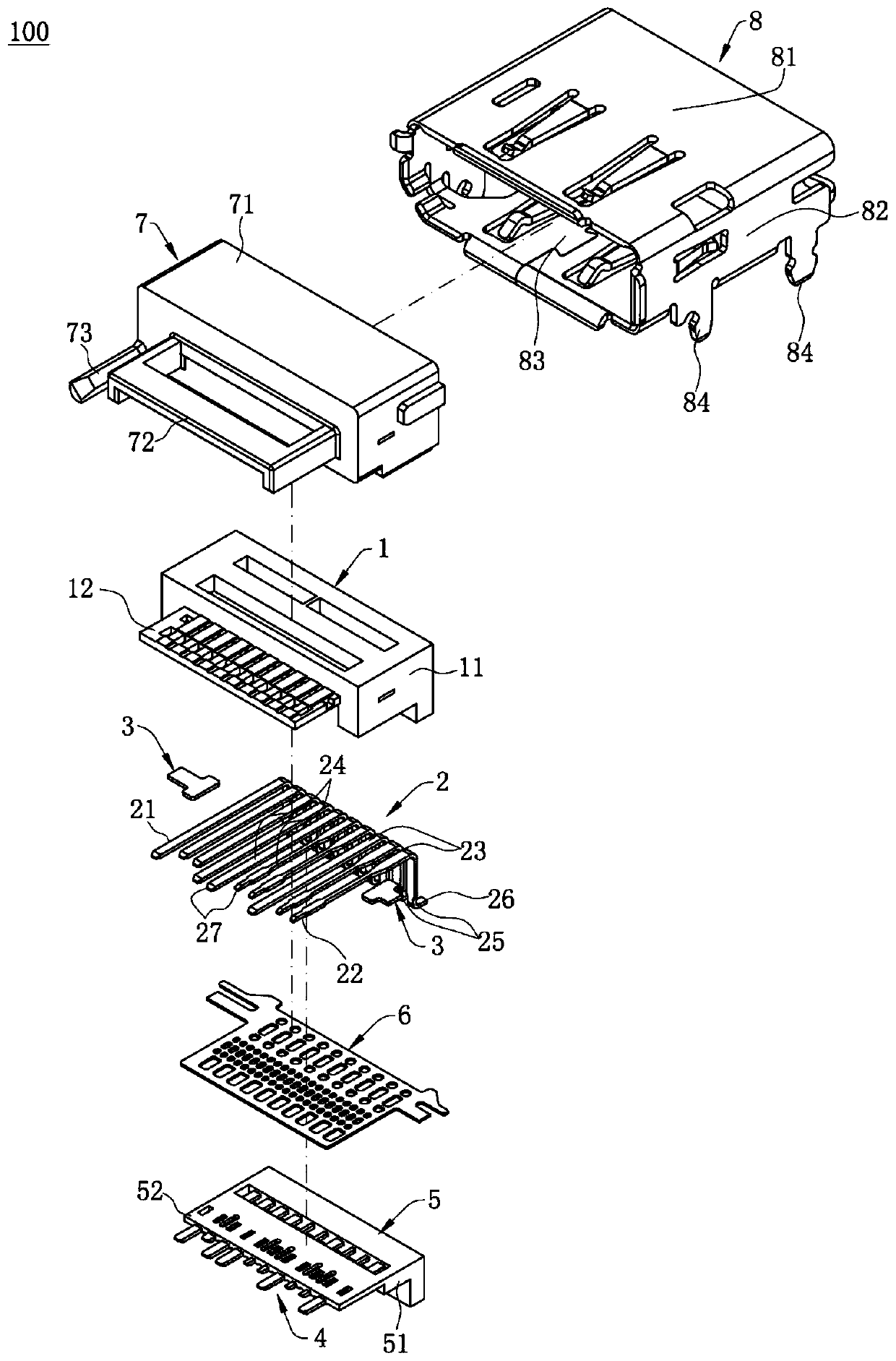

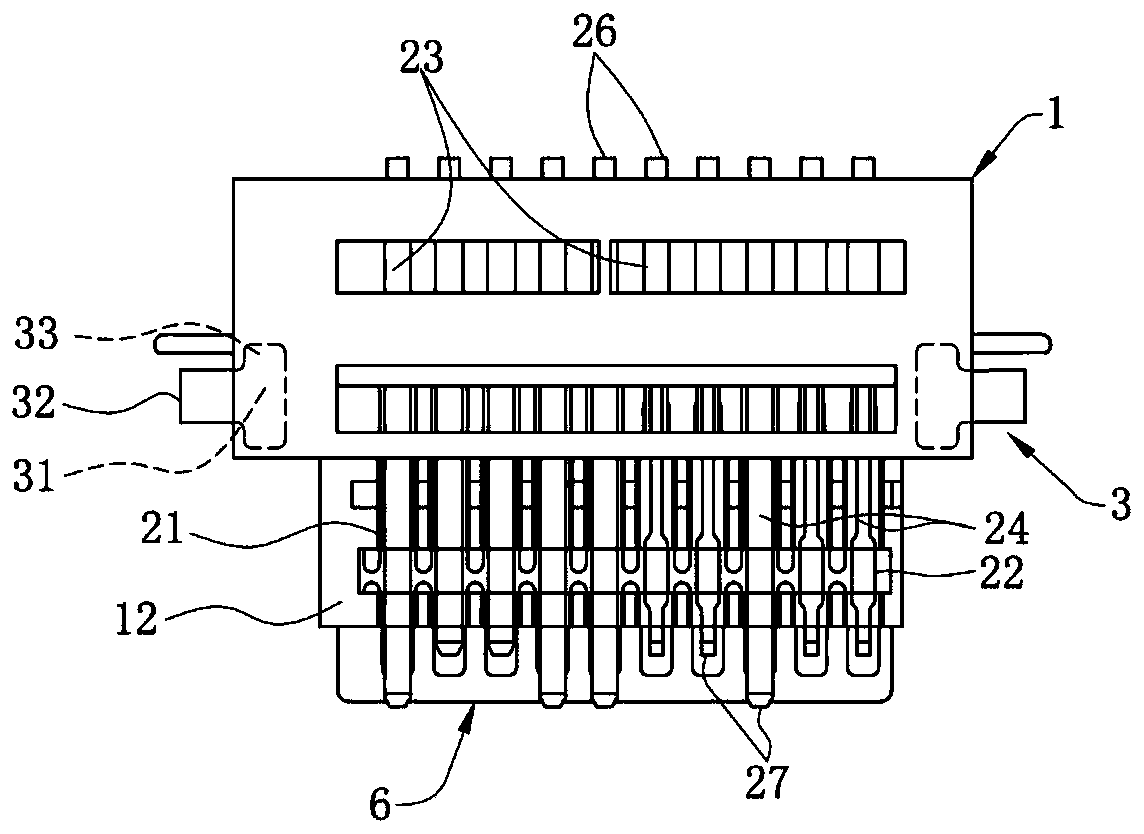

Electric connector and method for manufacturing same

InactiveCN110429414APrecise positioningFacilitates high-frequency transmission ratesContact member manufacturingContact member assembly/disassemblyElectricityEngineering

The invention discloses an electric connector and a method for manufacturing the same. A connecting member is embedded between the side edge of an insulating body and the outer side of the first terminal or last terminal in a first terminal strip, and a gap is arranged between the connecting member and the first terminal or last terminal, namely, the connecting member is not in contact with the adjacent first terminal or last terminal such that the width of the first terminal or last terminal cannot be increased. Therefore, the high-frequency transmission rate of the first terminal strip is ensured so that the electric connector can be formed which cannot affect the transmission quality of the terminals, is easy to machine and stable in structure, and has high-frequency transmission performance.

Owner:DEYI PRECISION ELECTRONIC IND CO LTD PANYU

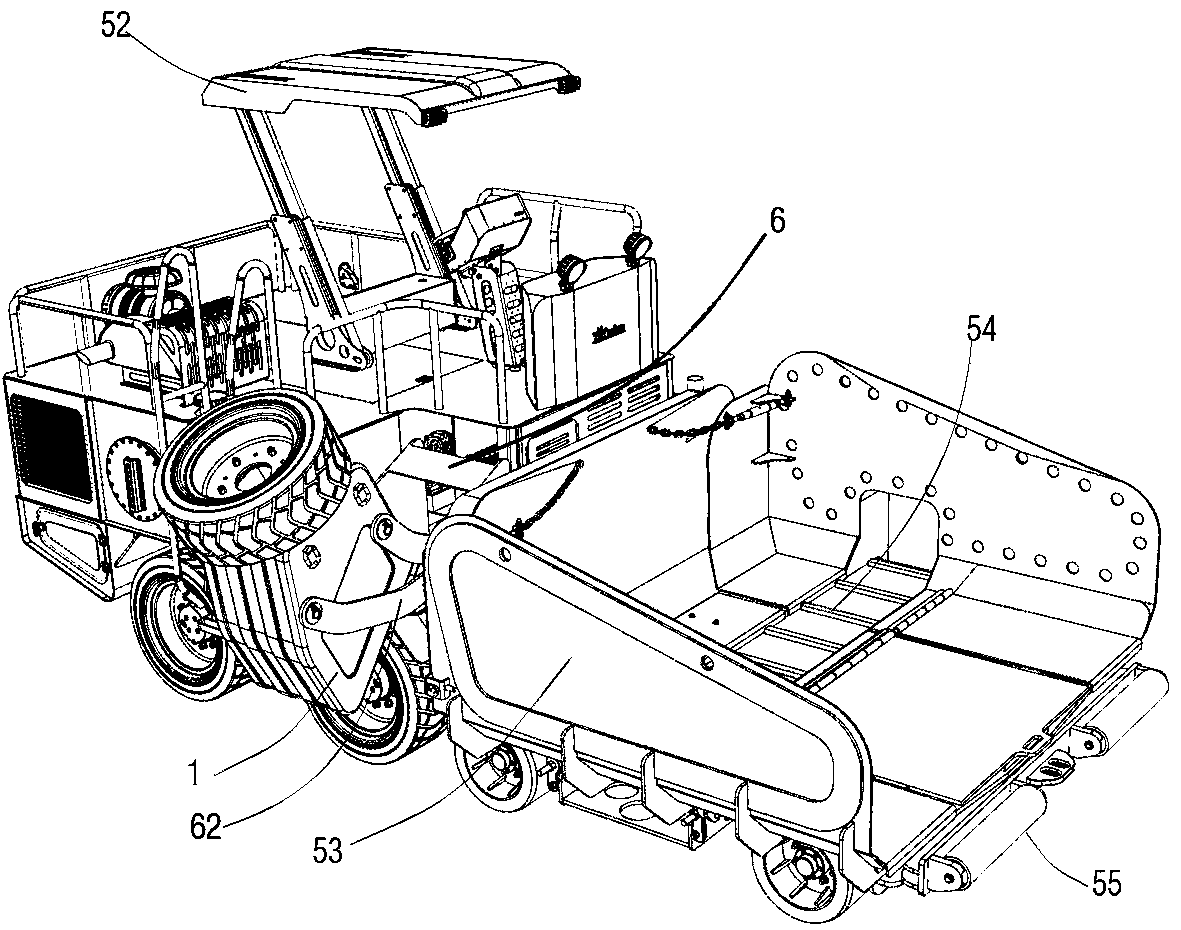

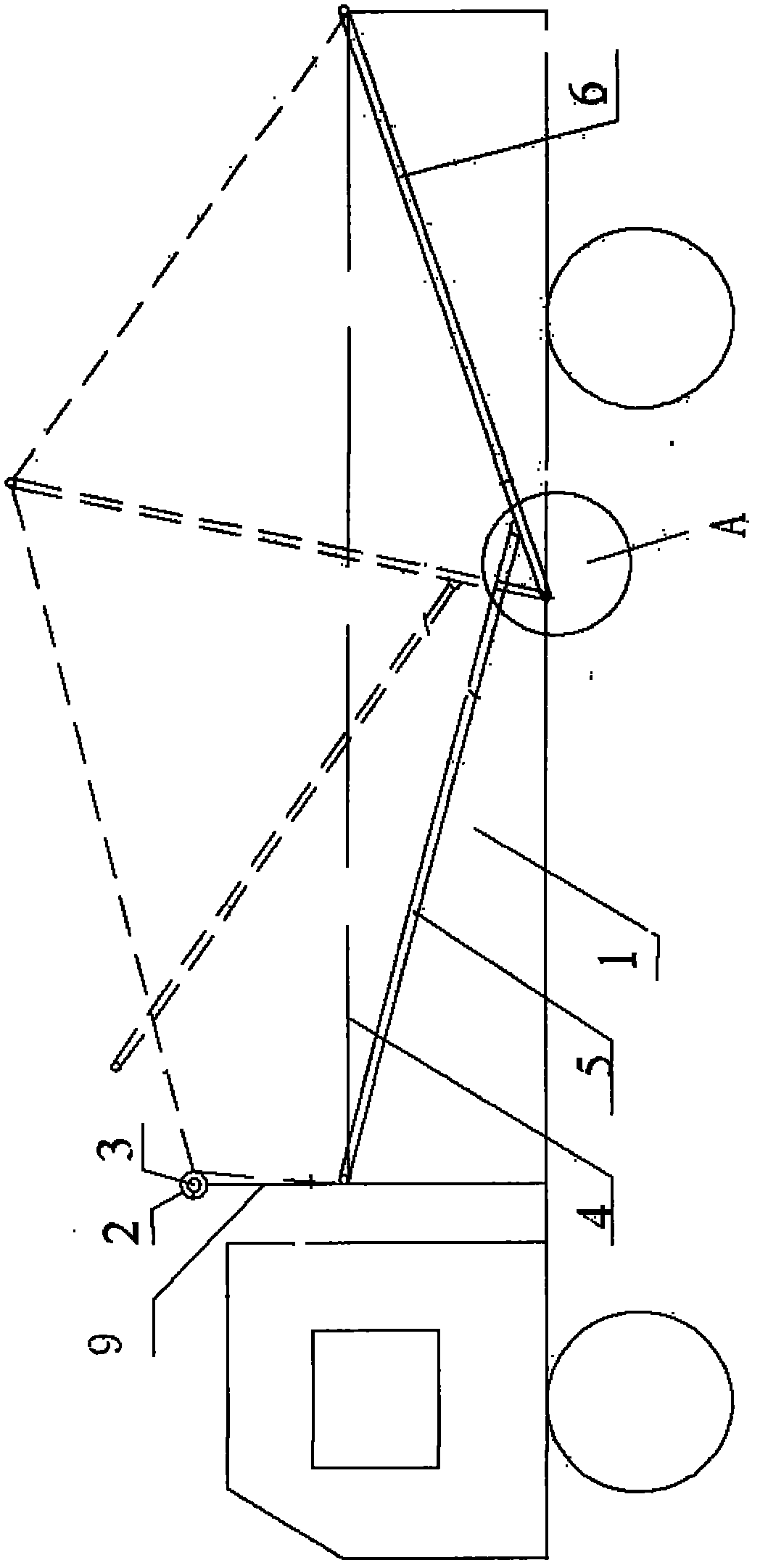

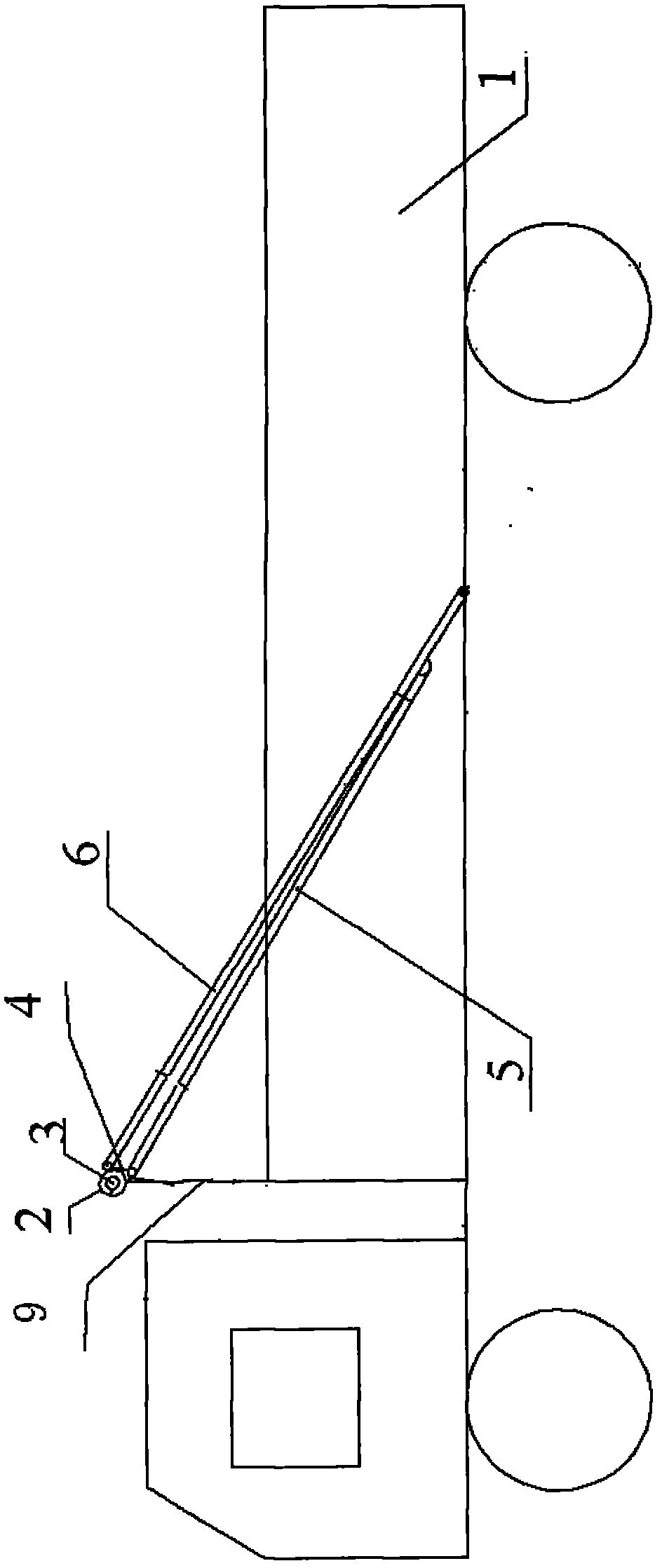

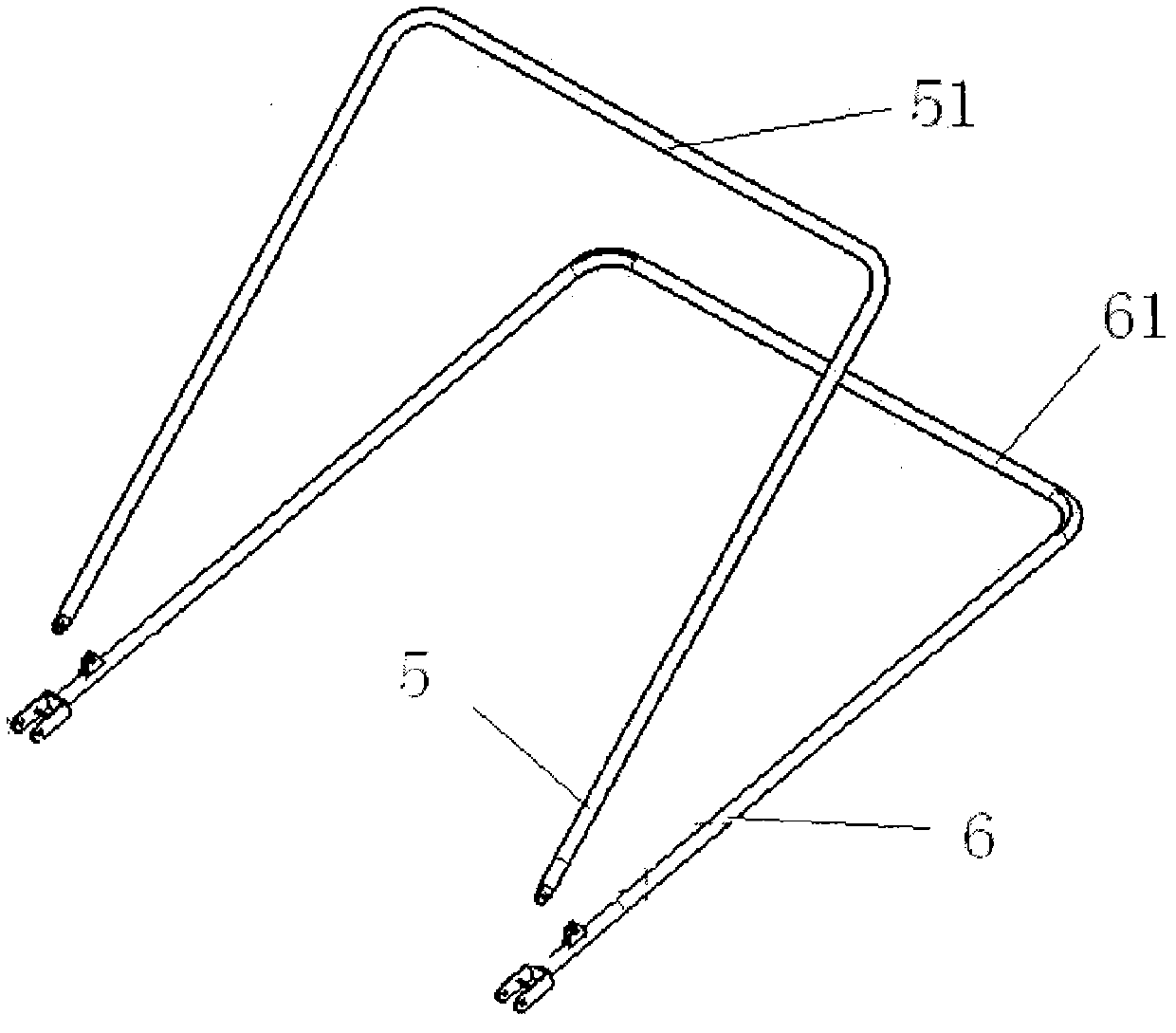

Escalator used for tunnel inspection car

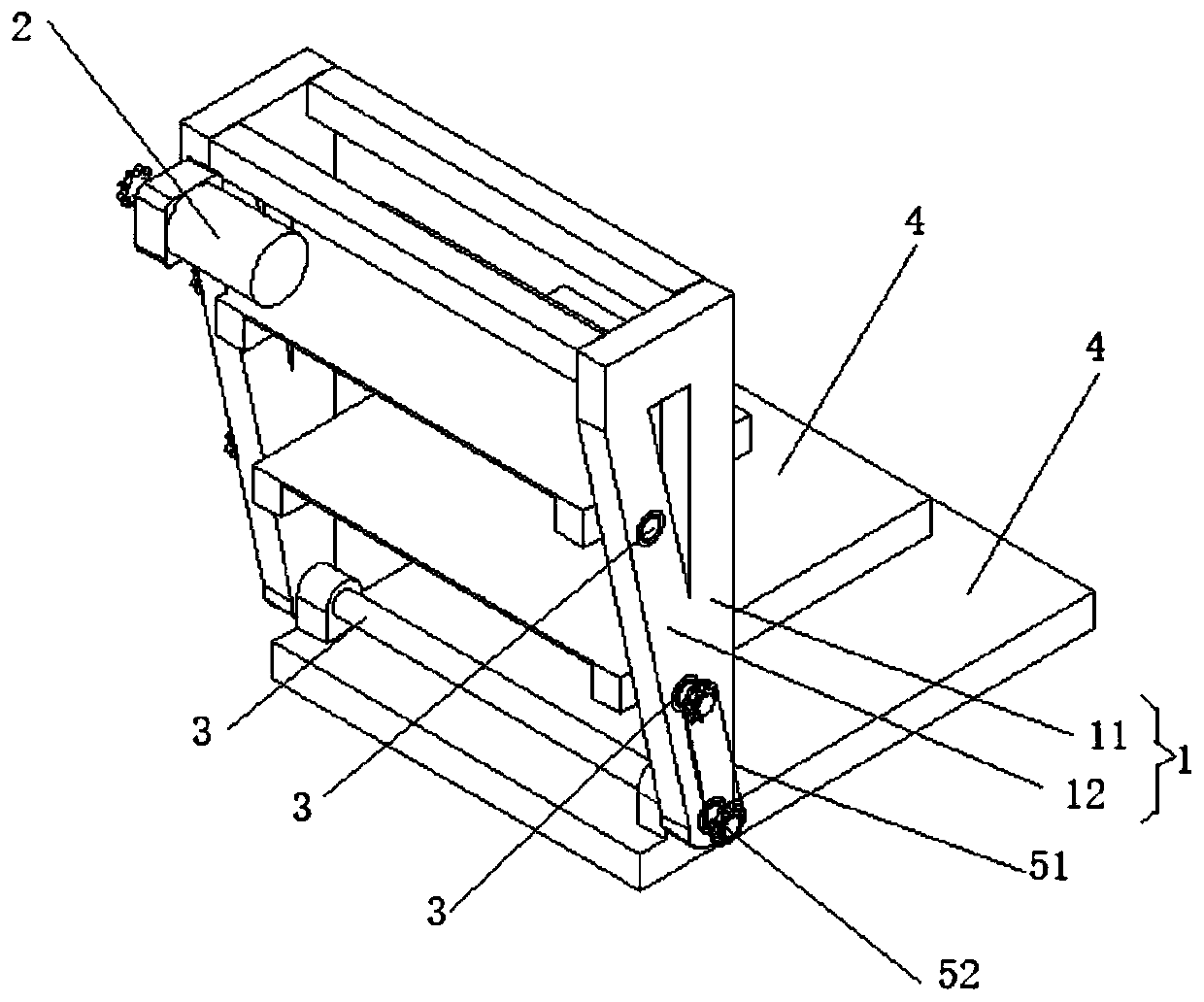

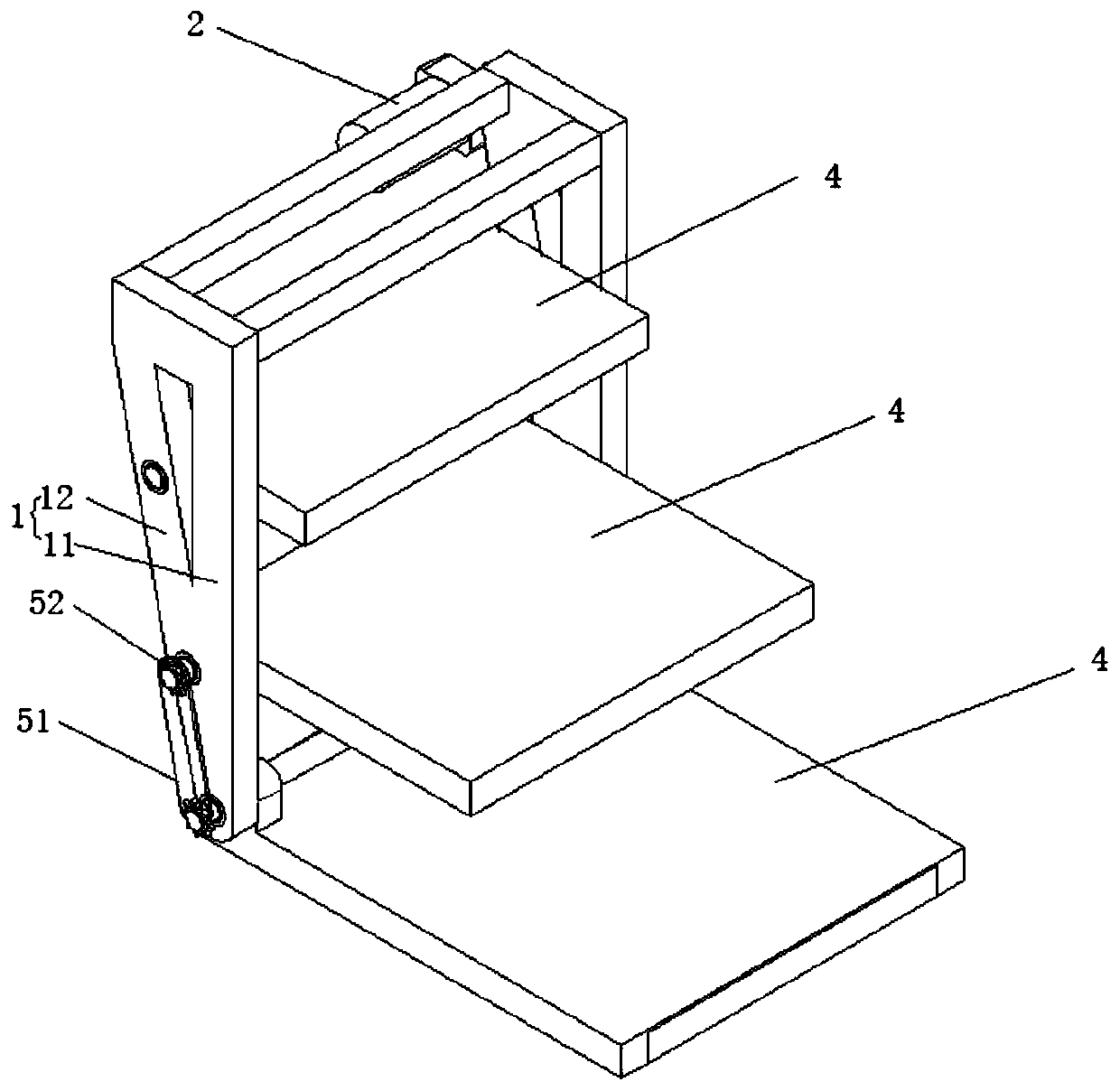

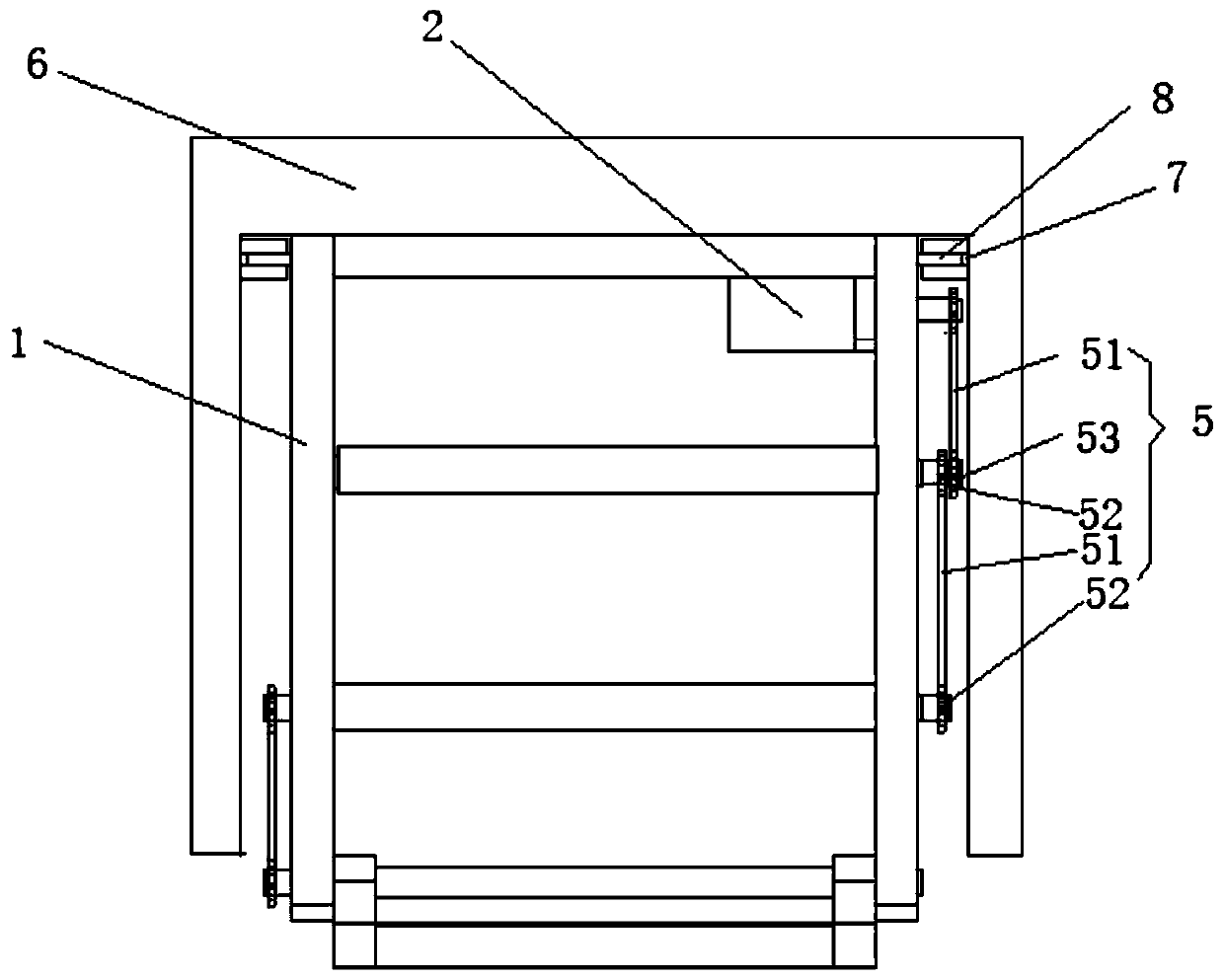

PendingCN110606024AEasy accessWon't increase the widthSteps arrangementItem transportation vehiclesRecovery positionEngineering

The invention discloses an escalator used for a tunnel inspection car. The escalator comprises a bracket and a driving component, wherein the bracket is connected with the base plate of a compartmentdoor; the front end surface of the bracket is level with the front end surface of the base plate of the compartment door; the bracket is provided with at least two pedals from top to bottom; the pedals and the bracket are rotatably connected, and junctions are aslant distributed along a direction near the front end surface of the bracket from top to bottom; a vertical distance between the first end and the second end of each pedal is equal to a vertical distance between the first end of each pedal and the top end of the bracket; and the driving component can enable the pedals to rotate to a use position or a recovery position. When a worker enters and leaves a compartment, the driving component can be used for enabling the pedals to rotate to the use position for the worker to enter and leave the compartment in virtue of the pedals, and safety is improved. After the worker enters and leaves the compartment, the driving component can be used for enabling the pedals to rotate to the recovery position, the pedals are collected, in addition, the pedals can be completely collected to be below the base plate of the compartment door, the width of a car body is not increased, and the normal operation and driving of the car can be guaranteed.

Owner:LIAONING PROVINCIAL TRANSPORTATION PLANNING & DESIGN INST

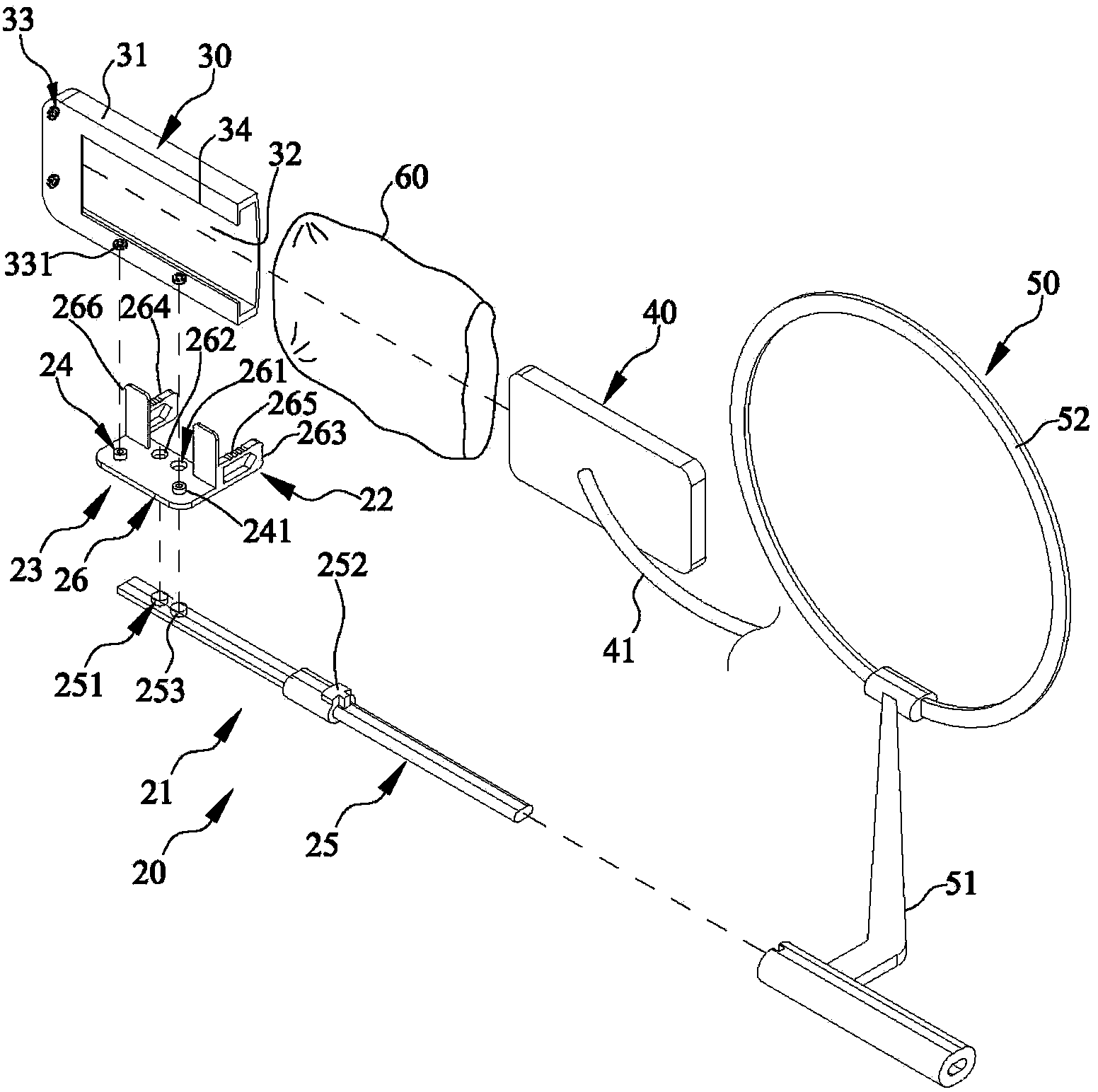

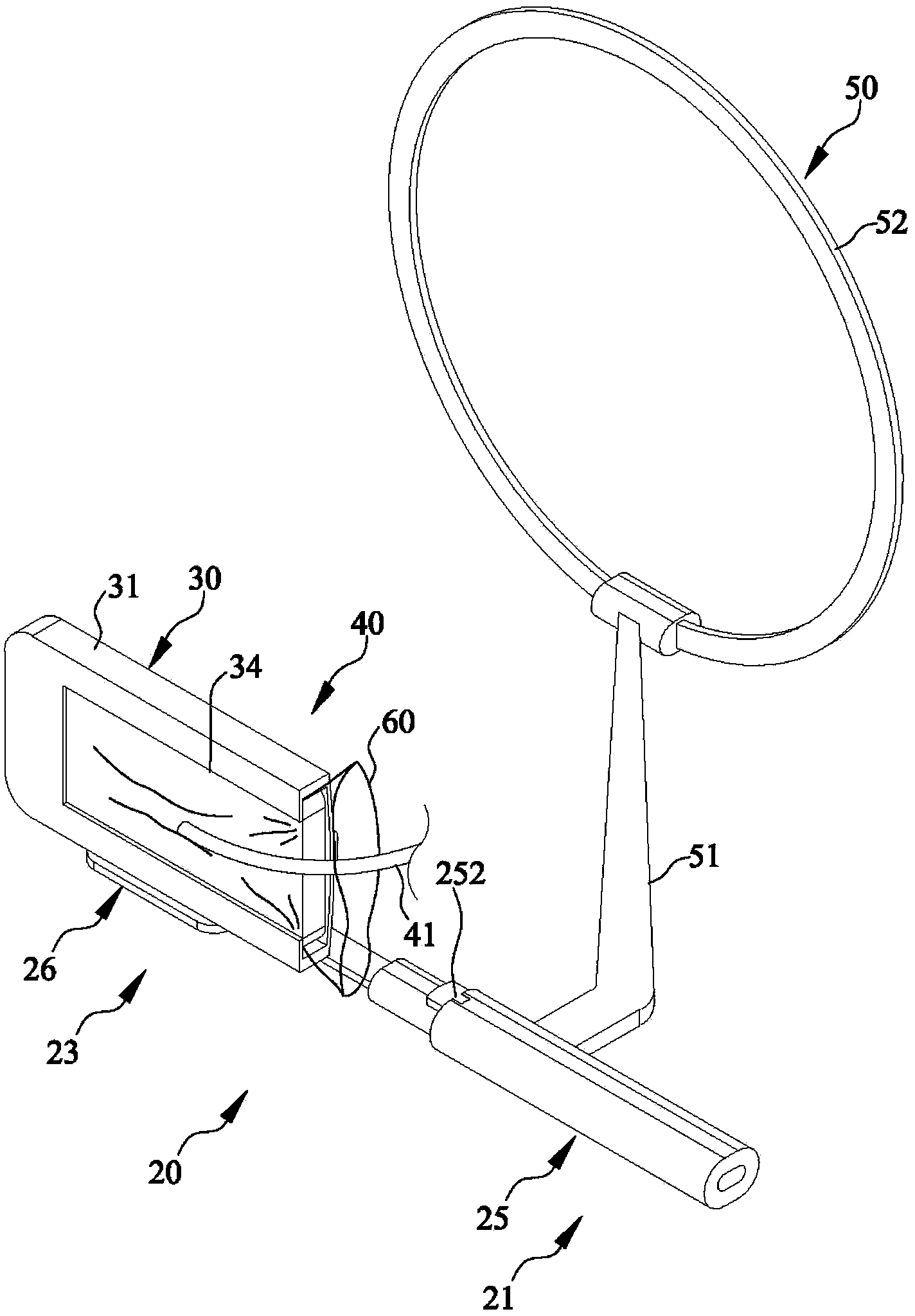

Headphone and headphone microphone pole device

PendingCN109587594AImprove qualityIncrease the lengthEarpiece/earphone manufacture/assemblyEngineeringHeadphones

The invention discloses a headphone microphone pole device, which comprises a microphone pole, a microphone bracket and a microphone, wherein the microphone bracket is fixedly arranged in the head part of the microphone pole; the microphone bracket is provided with a bracket inner cavity; the microphone is arranged in the bracket inner cavity, and the bracket inner cavity is divided to a front voice cavity and a rear voice cavity in a mode of being vertical to the axis; the upper end of the side wall of the microphone bracket is provided with a front voice hole communicated with the front voice cavity and the lower end of the side wall is provided with a rear voice hole communicated with the rear voice cavity; and the places, corresponding to the front voice hole and the rear voice hole, on the side wall of the microphone pole are provided with through holes respectively. The invention also provides a headphone comprising the headphone microphone pole device. When the headphone and theheadphone microphone pole device are applied, the length of the bracket inner cavity can be increased according to needs, the space of the front voice cavity and the rear voice cavity is thus increased, and as the front voice cavity and the rear voice cavity are distributed in a front-back mode along the axis of the microphone pole, the width of the microphone pole is not increased along with increasing of the space of the front voice cavity and the rear voice cavity, and the whole appearance size can be controlled conveniently.

Owner:GEER TECH CO LTD

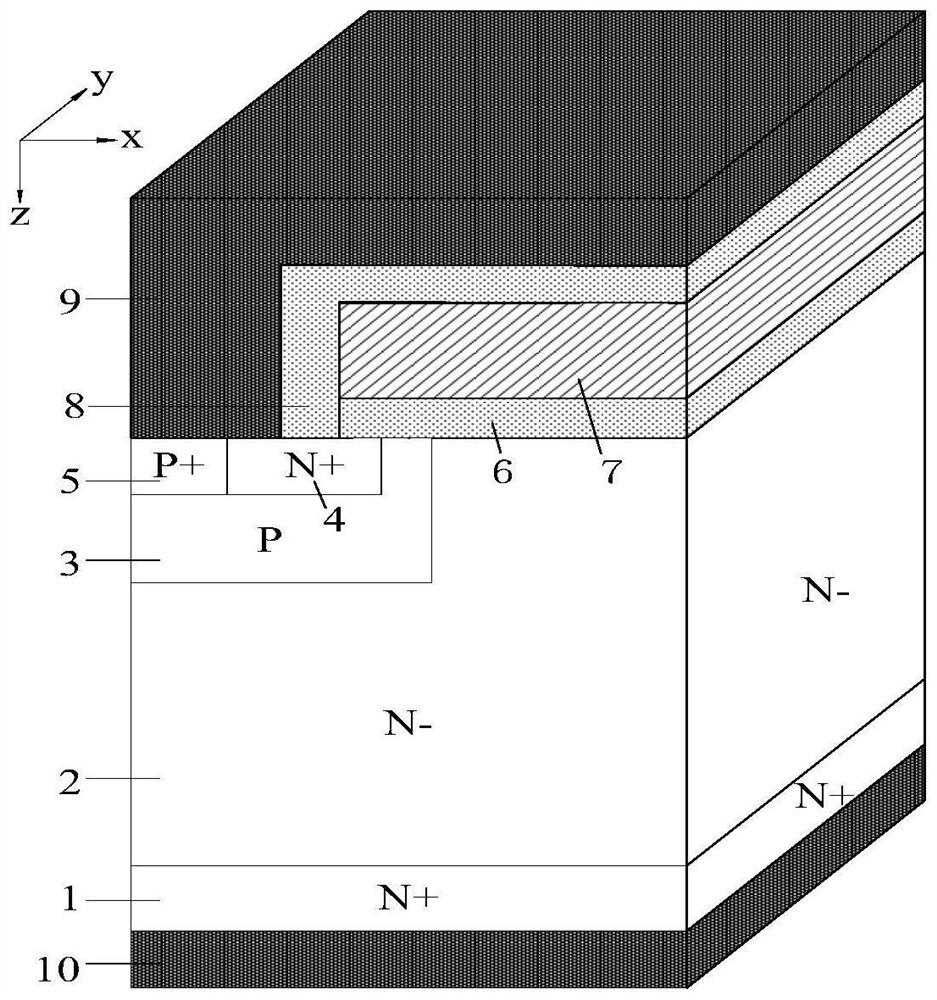

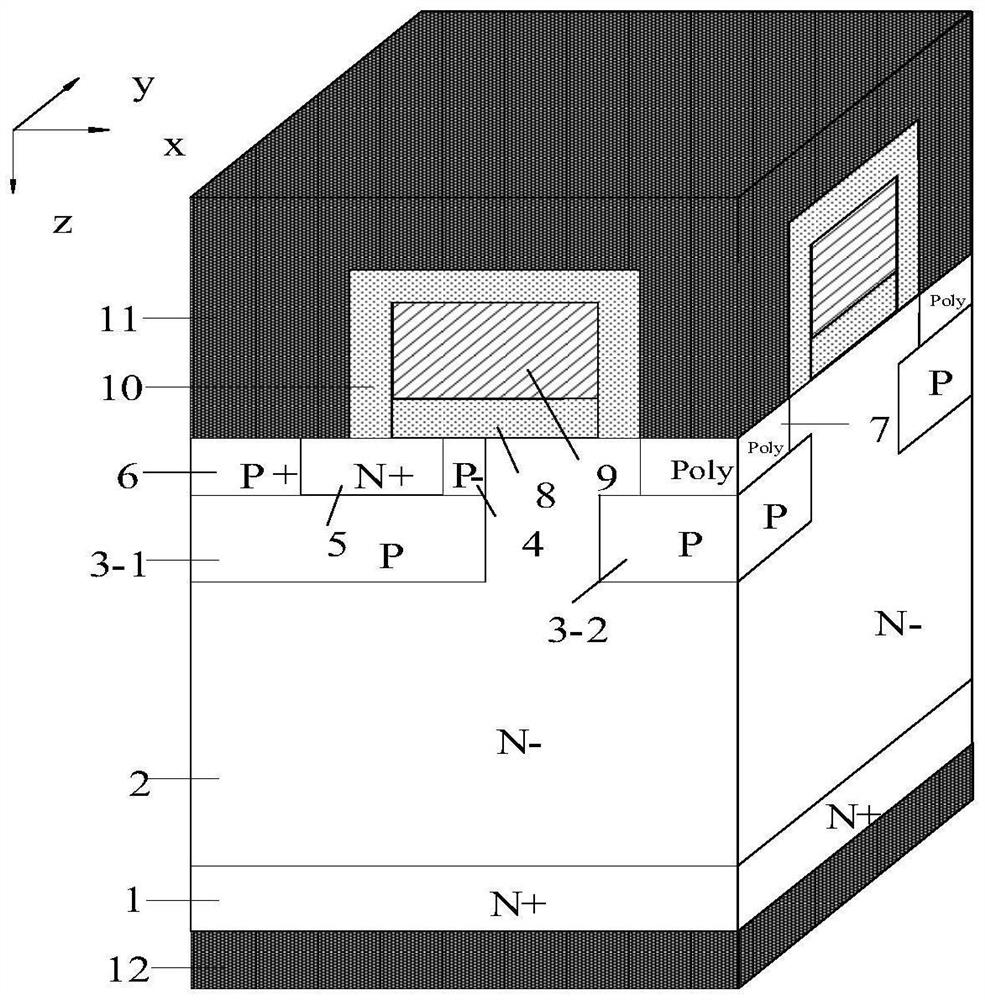

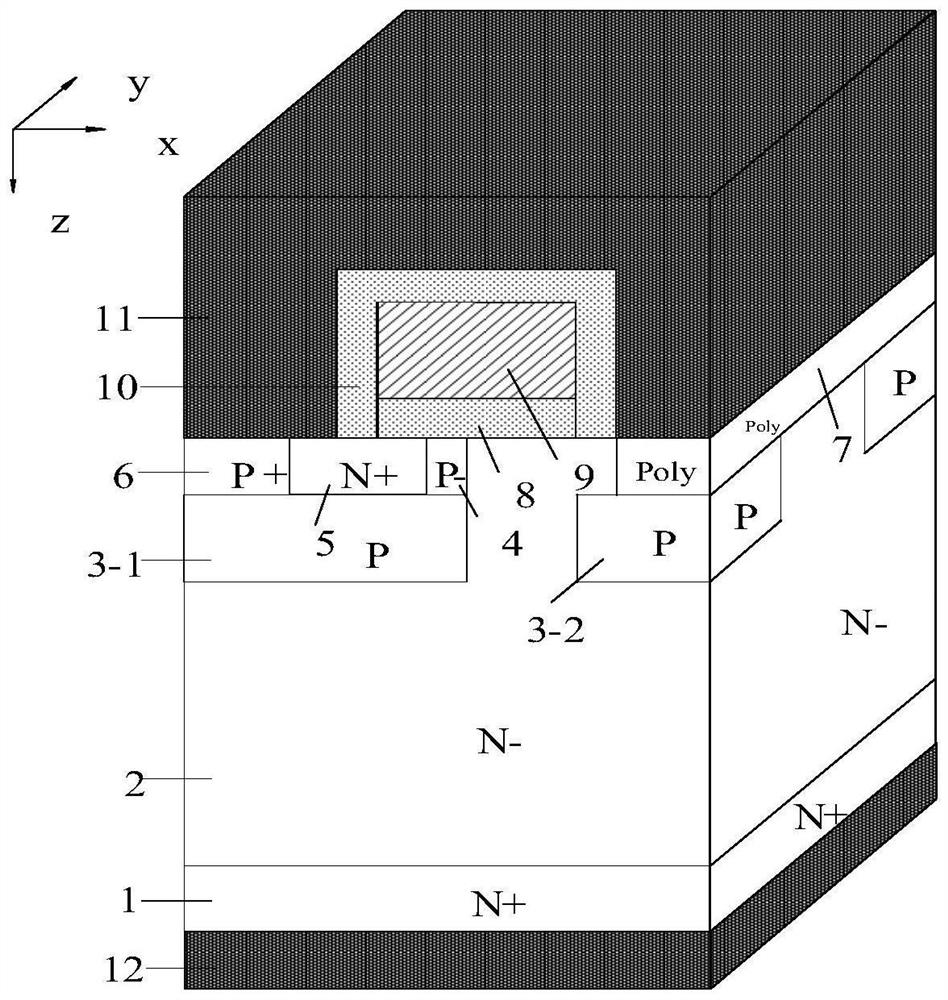

Separation gate SiC MOSFET integrated with heterojunction diode and manufacturing method thereof

ActiveCN114664929APerformance is not affectedConvenient timeEfficient power electronics conversionSemiconductor/solid-state device manufacturingMOSFETHigh concentration

The invention belongs to the technical field of power semiconductor devices, and relates to a separation gate SiCMOSFET of an integrated heterojunction diode and a manufacturing method of the separation gate SiCMOSFET. According to the invention, the heterojunction diode is integrated in the three-dimensional y direction of the SiC MOSFET, so that the cell width of the SiC MOSFET is not increased, the problems of overlarge forward turn-on voltage drop, overlong reverse recovery time and the like of a parasitic diode can be effectively solved, and compared with an internally integrated SBD, the integrated heterojunction diode has smaller forward voltage drop. According to the mode of integrating the heterojunction diode, the area of an active region does not need to be additionally increased, the integration level is higher, and the width of the JFET region is not increased. Meanwhile, the spaced P-type doped regions are introduced in the y direction of the JFET region, so that the electric field distribution of the JFET region of the device and the peak electric field in the oxide layer during blocking work can be improved, a CSL layer with higher concentration can be adopted during design, and the forward conduction characteristic of the device is improved and the resistance of the device during forward conduction is reduced while the reverse blocking characteristic of the device is not reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

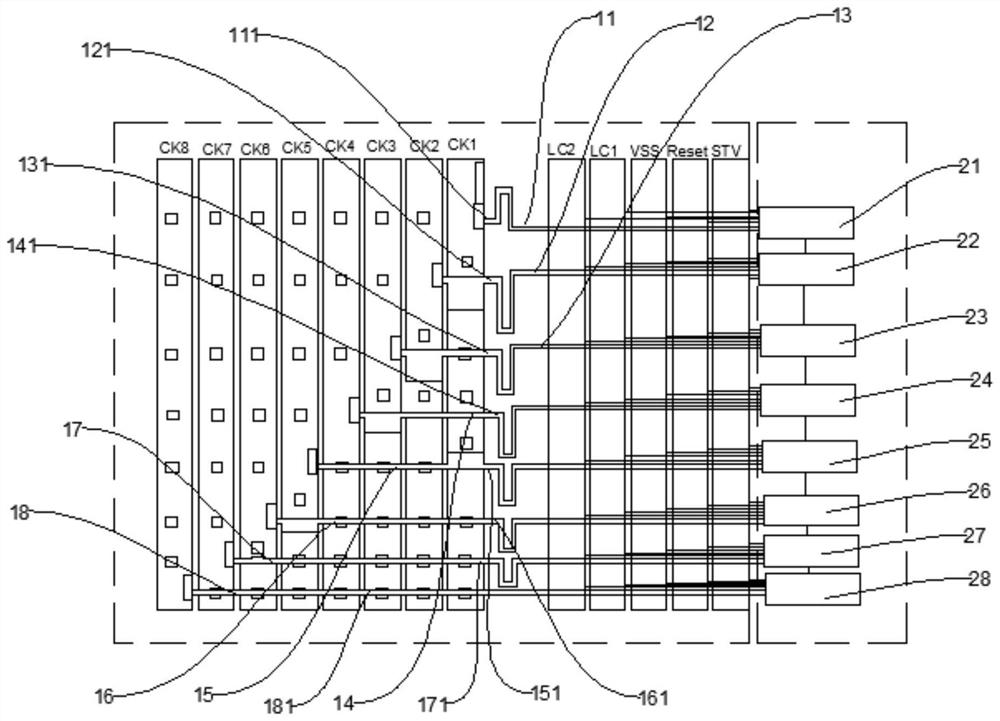

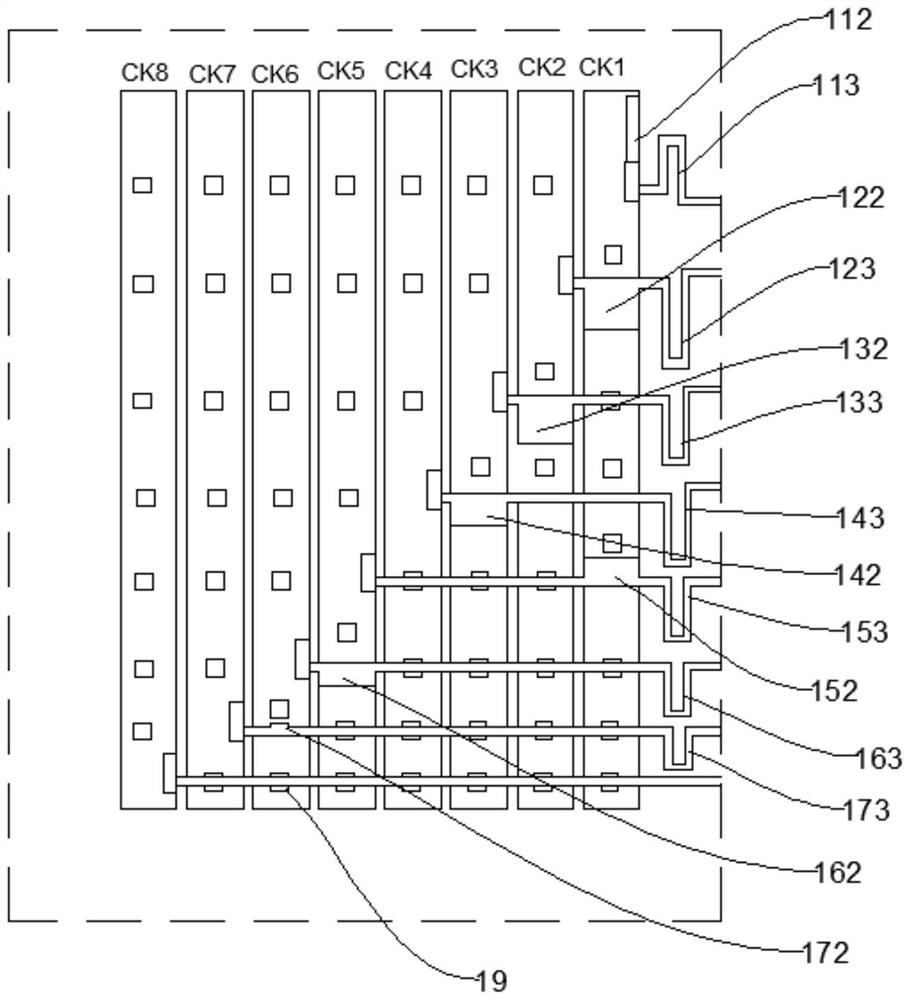

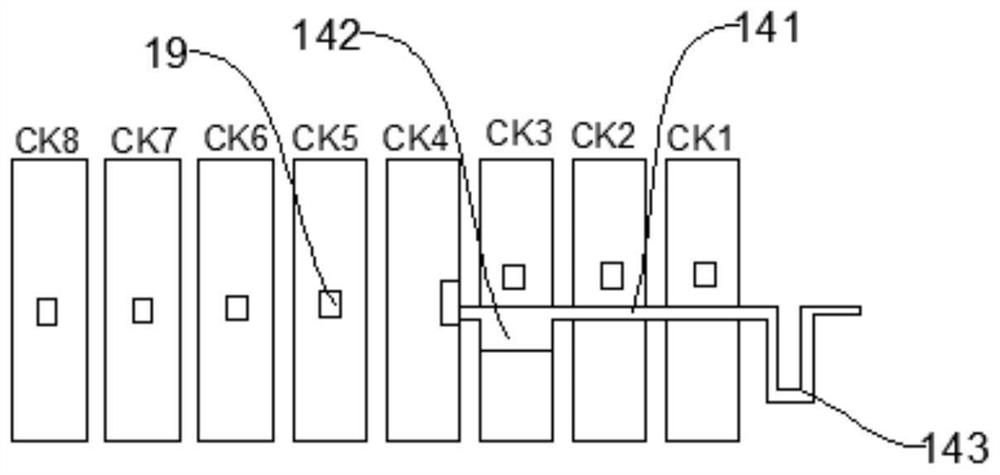

Gate drive circuit and display panel

PendingCN114664270AIncrease border widthConducive to designStatic indicating devicesCapacitanceHemt circuits

The invention relates to a gate drive circuit and a display panel. The gate drive circuit comprises a plurality of cascaded shift register units, a plurality of gate drive units and a control circuit, wherein the shift register units are provided with clock signal ends; n clock signal lines, each shift register unit is correspondingly connected to one clock signal line through a connecting line, and the connecting line comprises a conduction section; the at least one connecting line further comprises a capacitance adjusting section which is electrically connected with the conduction section, the capacitance adjusting section is used for adjusting coupling capacitance between the corresponding clock signal line and the conduction section, and the capacitance adjusting section is stacked on the at least one clock signal line opposite to the conduction section connected with the capacitance adjusting section; the resistance adjusting section is electrically connected with the conduction section, and the resistance adjusting section is used for adjusting the impedance between the corresponding clock signal line and the clock signal end of the shifting register unit. According to the invention, the load difference of different clock signals can be effectively reduced, so that the display effect of the display interface is improved.

Owner:CHANGSHA HKC OPTOELECTRONICS CO LTD +1

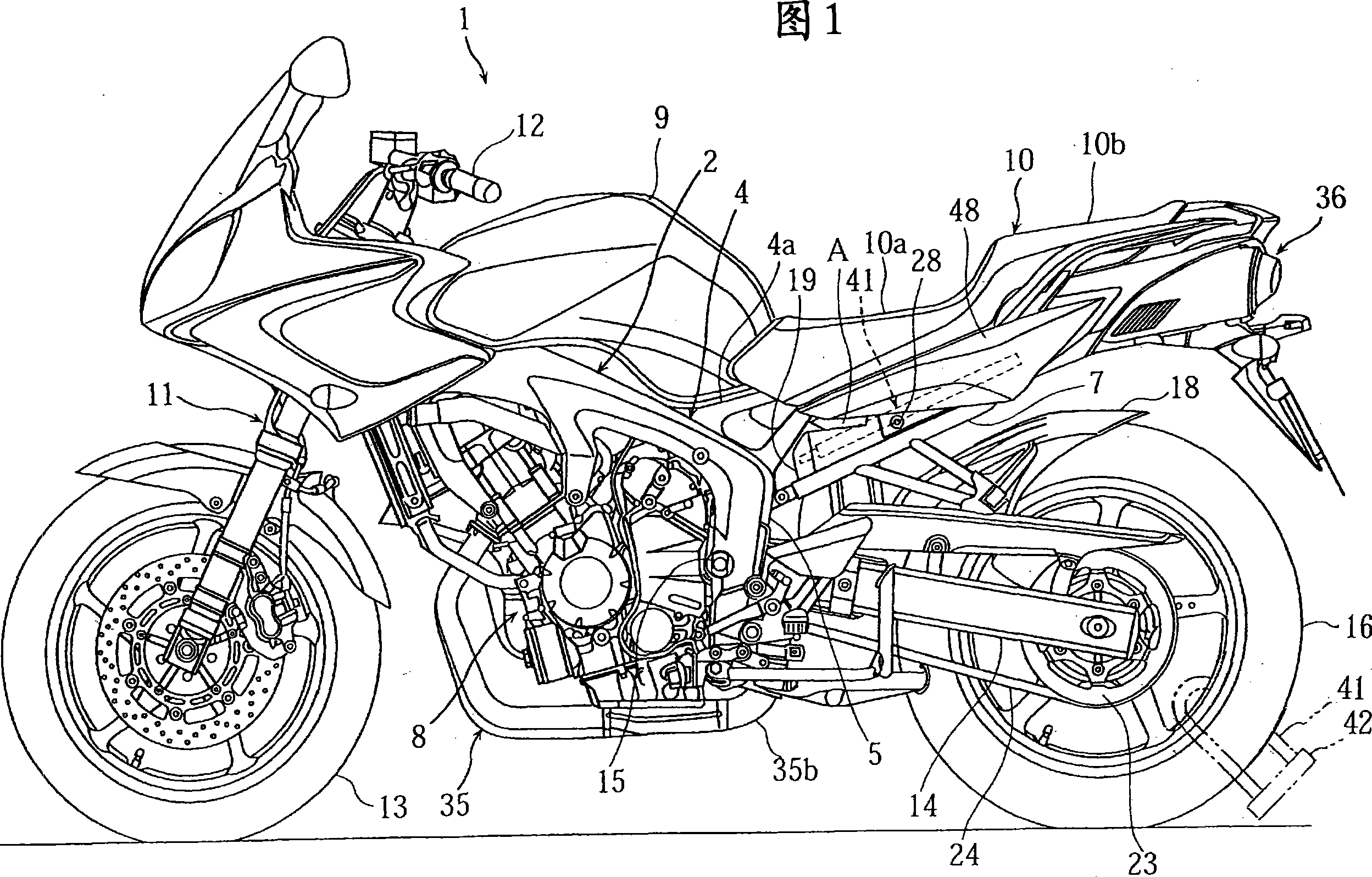

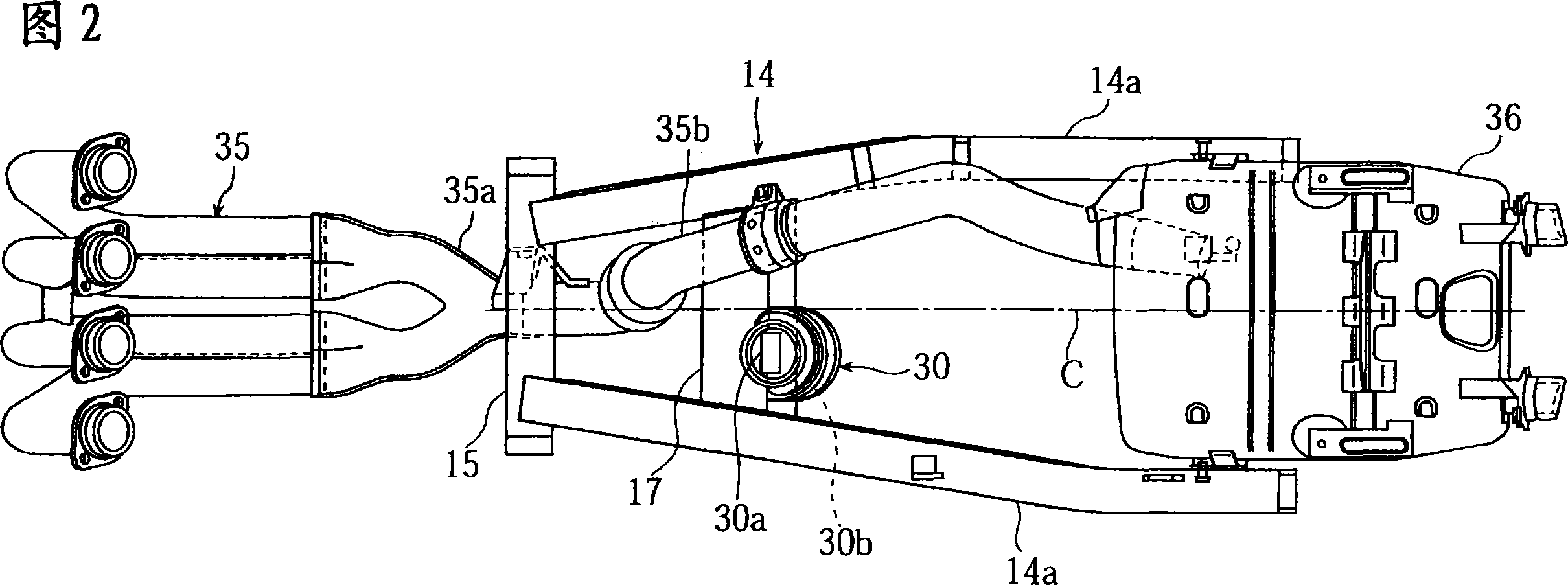

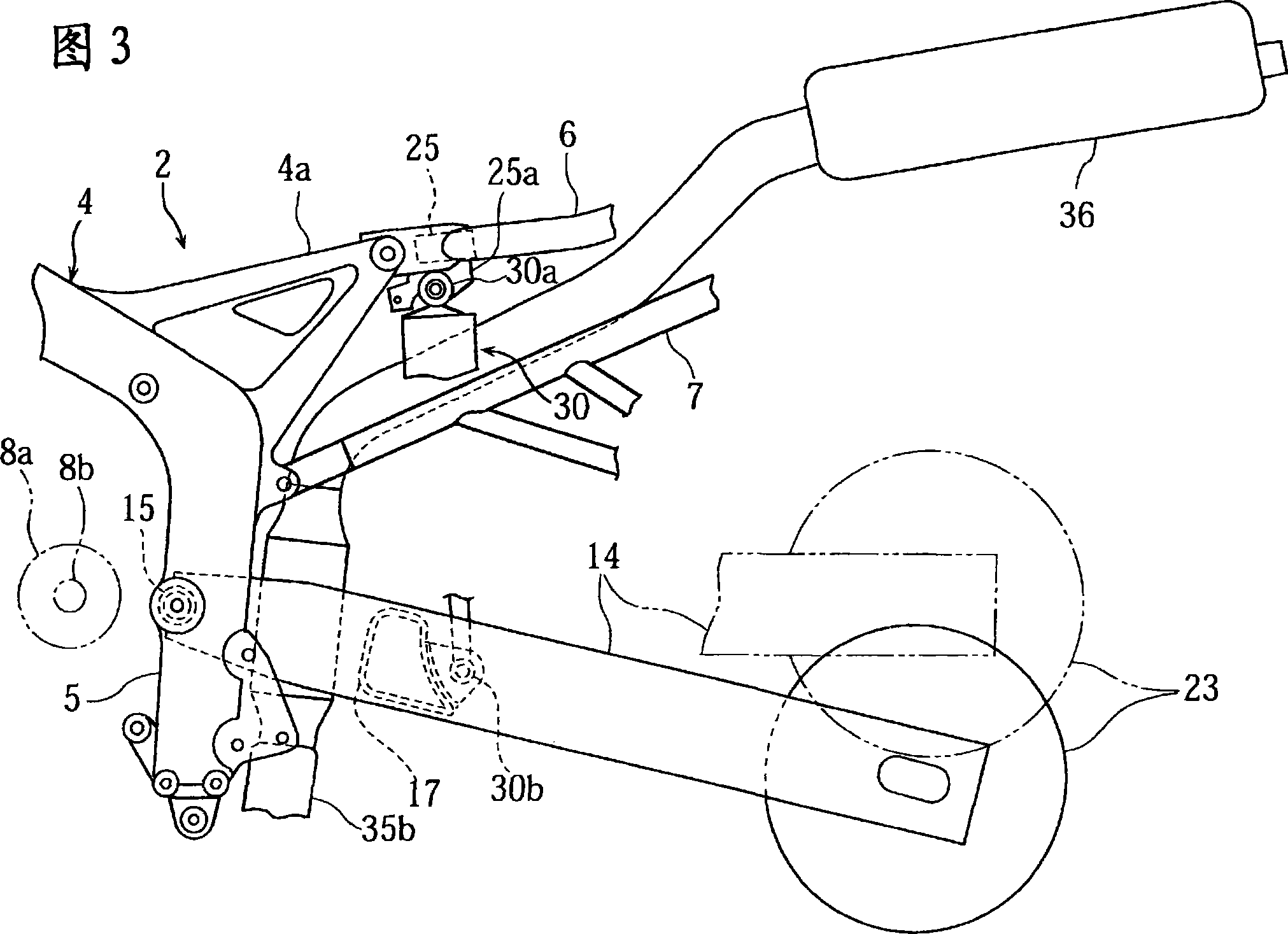

Motorcycle

InactiveCN101181918ALower the altitudeReduce thicknessAnti-theft cycle devicesMotorcyclesMufflerExhaust pipe

Owner:YAMAHA MOTOR CO LTD

Electric connector and manufacturing method thereof

ActiveCN111048935APrecise positioningFacilitates high-frequency transmission ratesContact member manufacturingContact member assembly/disassemblyElectrical connectionStructural engineering

The invention discloses an electric connector and a manufacturing method of the electric connector. A connecting piece is embedded between the side edge of an insulating body and the outer side of a row head terminal or a row tail terminal in a first terminal row; a gap is formed between the connecting piece and the row head terminal or the row tail terminal, that is to say, the connecting piece does not contact with the adjacent row head terminal or row tail terminal. Therefore, the width of the row head terminal or the row tail terminal is not increased. The high-frequency transmission rateof the first terminal row is ensured. The electric connector which does not influence terminal transmission quality, is convenient to process and stable in structure and has high-frequency transmission performance can be formed.

Owner:DEYI PRECISION ELECTRONIC IND CO LTD PANYU

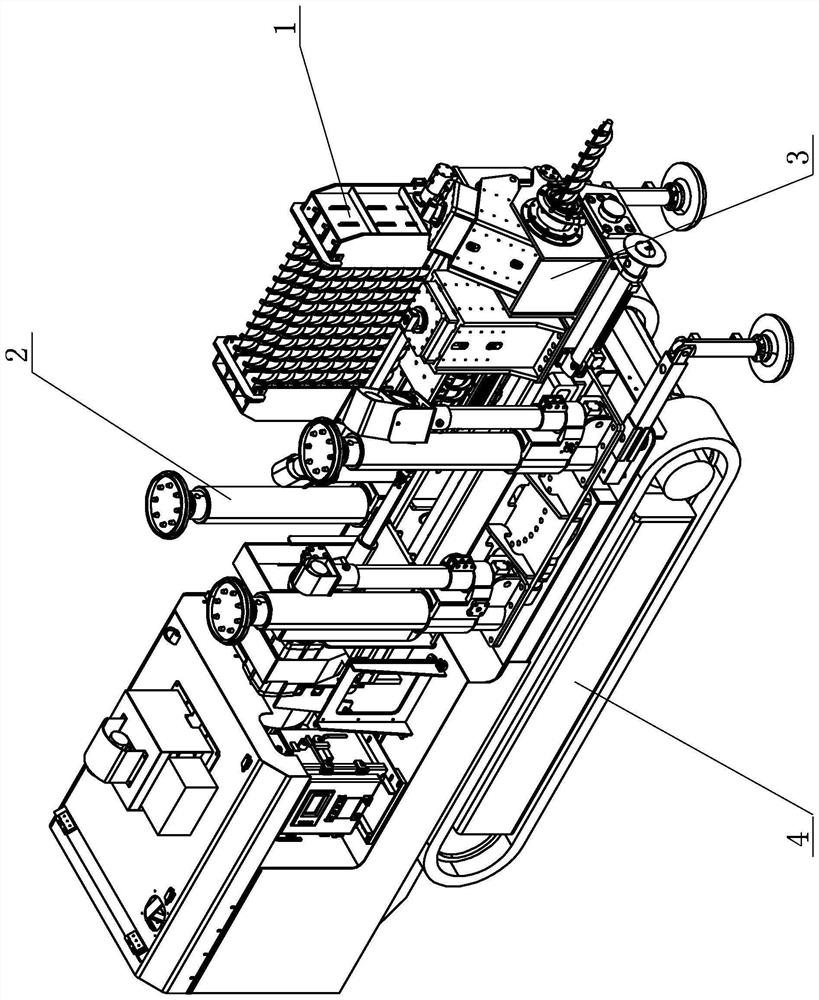

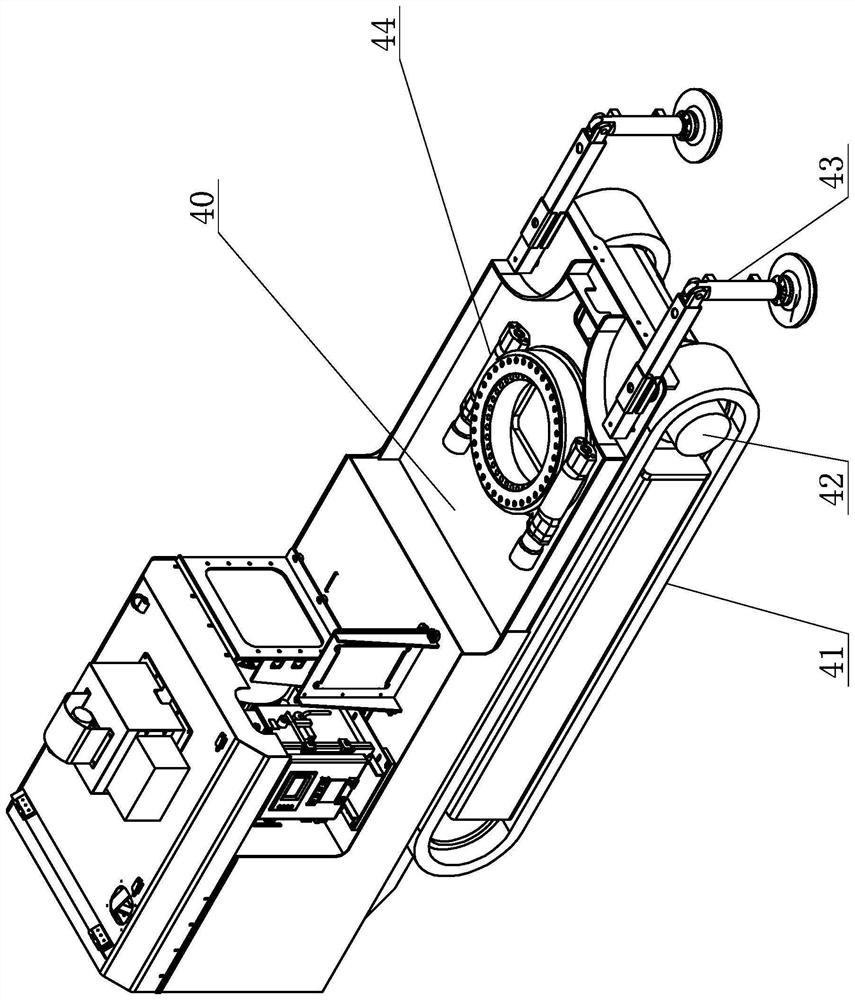

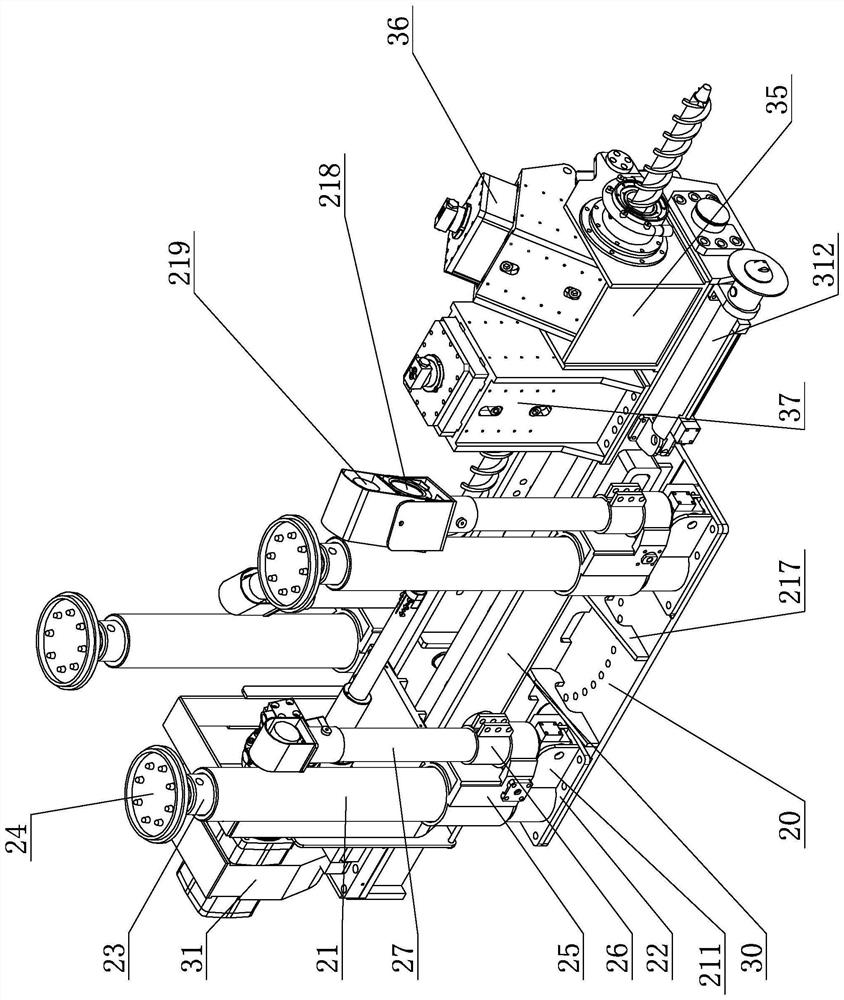

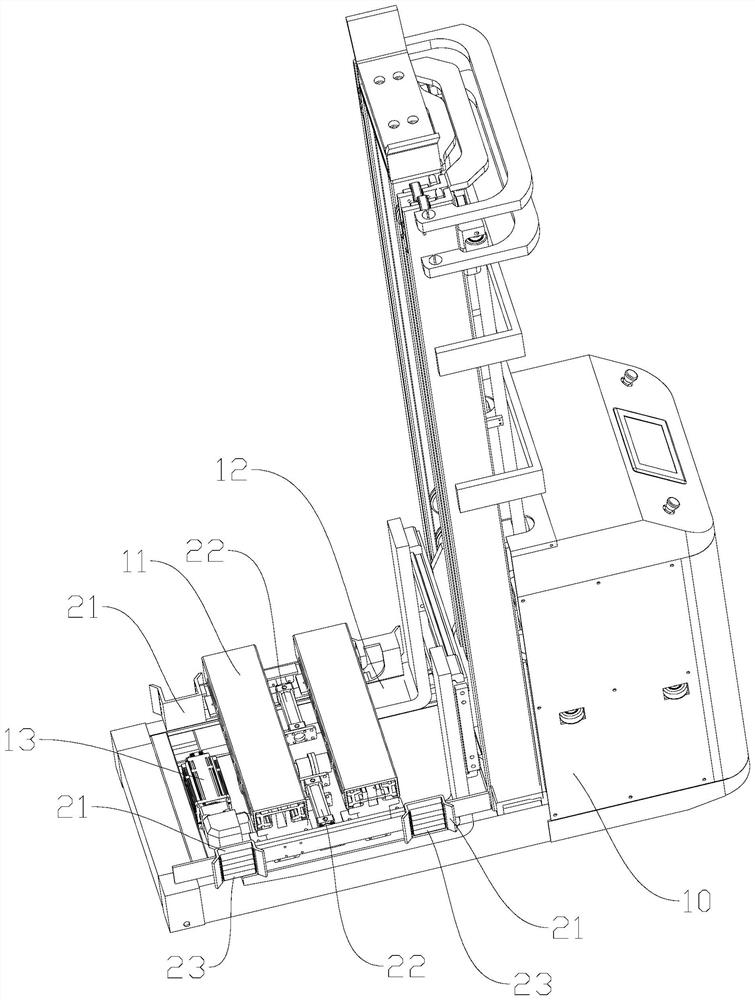

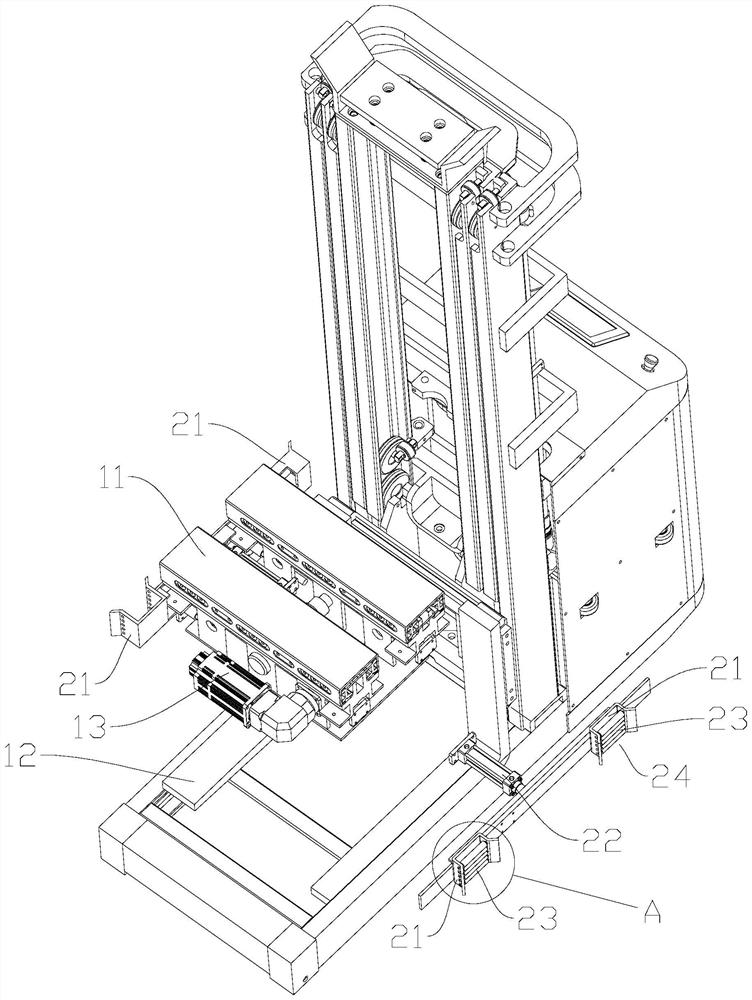

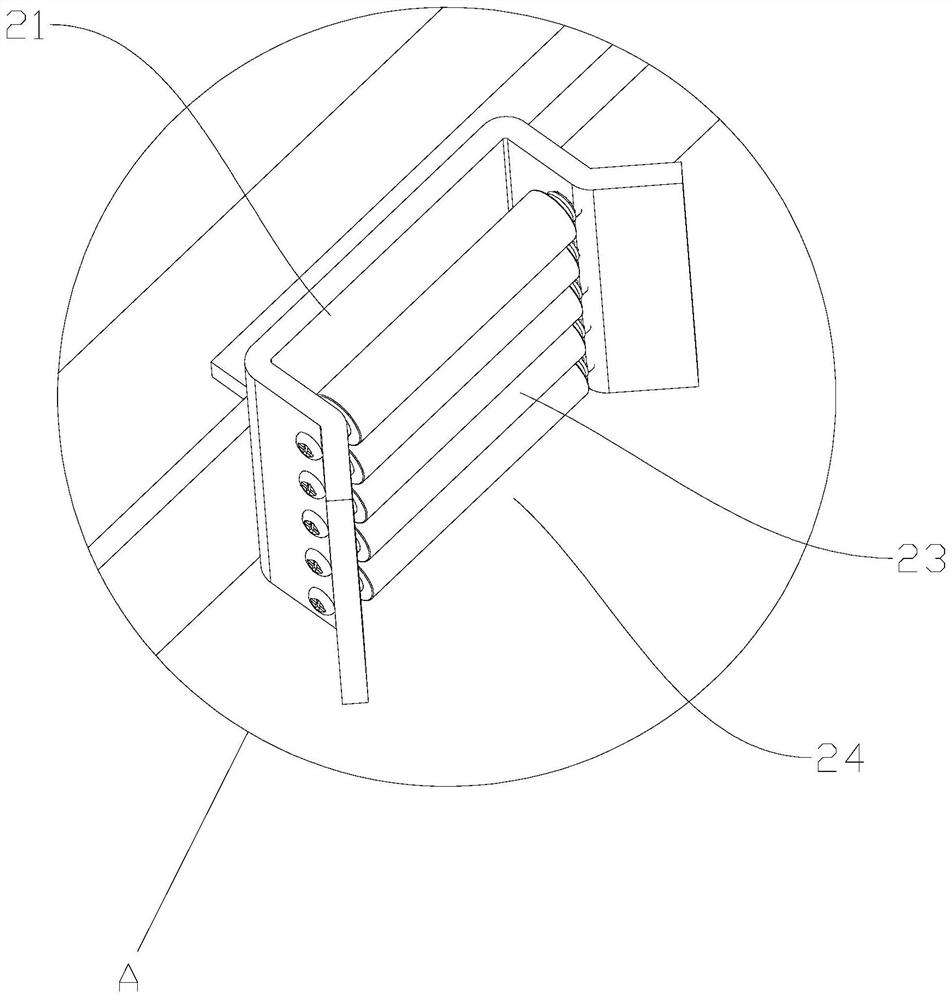

Drilling machine capable of automatically ascending and descending drill rod and automatic control method

PendingCN113605838ASimple structureReliable actionDrilling rodsConstructionsAutomatic controlEngineering

The invention discloses a drilling machine capable of automatically ascending and descending a drill rod and an automatic control method. The drilling machine comprises a chassis walking unit, a supporting device, a drill rod feeding device and an automatic drill rod box device, the supporting device is installed on the chassis walking unit, the drill rod feeding device is installed on the supporting device, the automatic drill rod box device is installed on the drill rod feeding device, wherein the supporting device can rotate relative to the chassis walking unit, the drill rod feeding device can vertically move on the supporting device, drill rods in the automatic drill rod box device can automatically go up and down in the drill rod feeding device, the drill rod feeding device can achieve one-by-one drilling and one-by-one retreating of the drill rods, the chassis walking unit comprises a vehicle body, a crawler belt and a walking motor are installed at the bottom of the vehicle body, a walking motor is started to drive the crawler belt to rotate and walk, the automatic drill rod box device comprises a supporting seat, and a drill rod box body is installed on the supporting seat.

Owner:ZOUCHENG TIANHE SCI & TECH

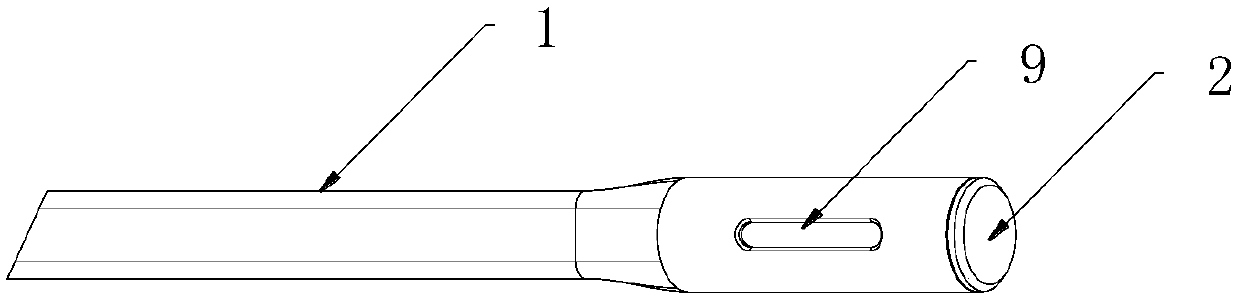

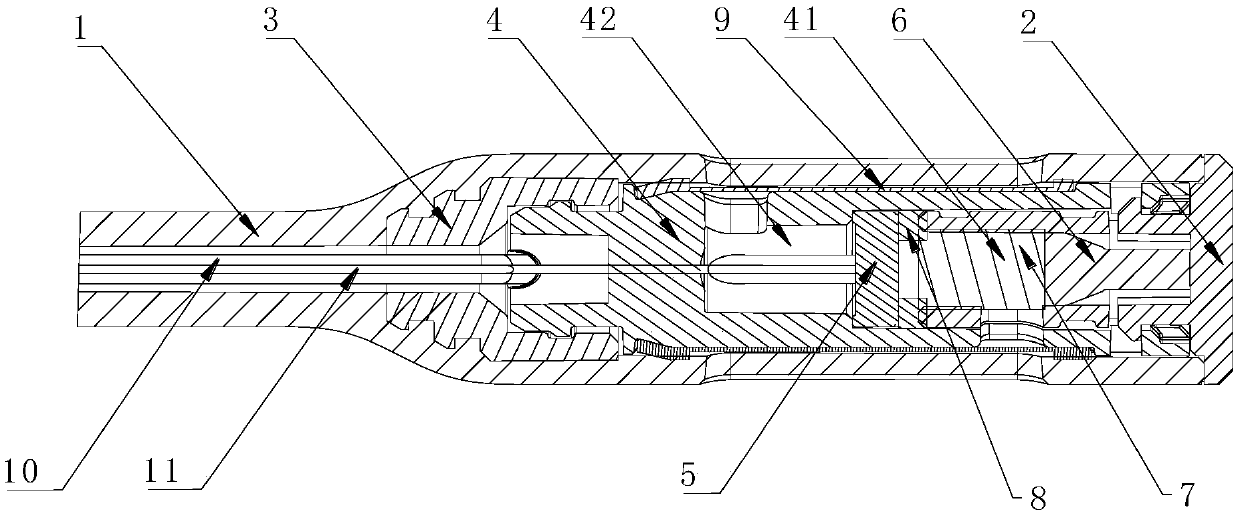

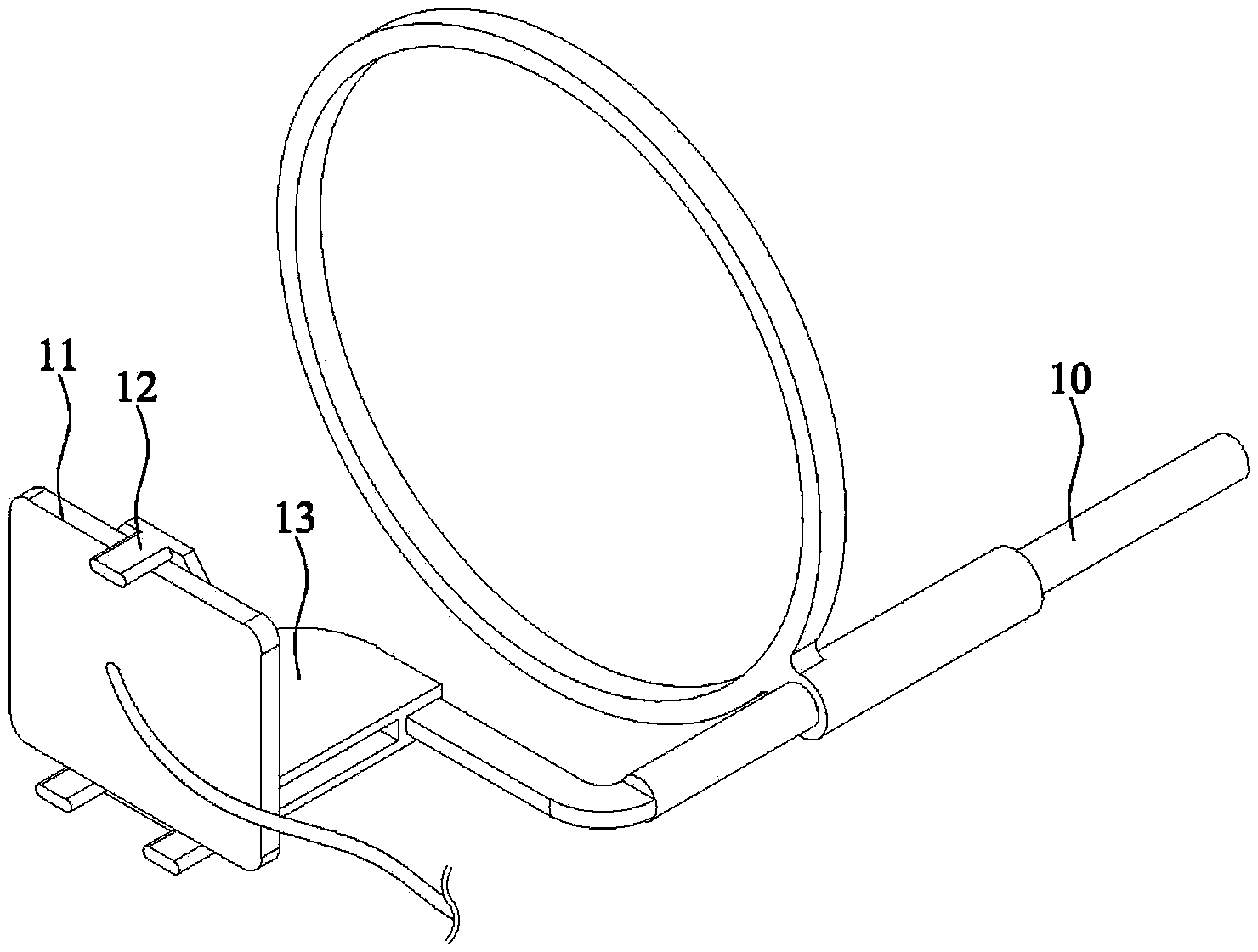

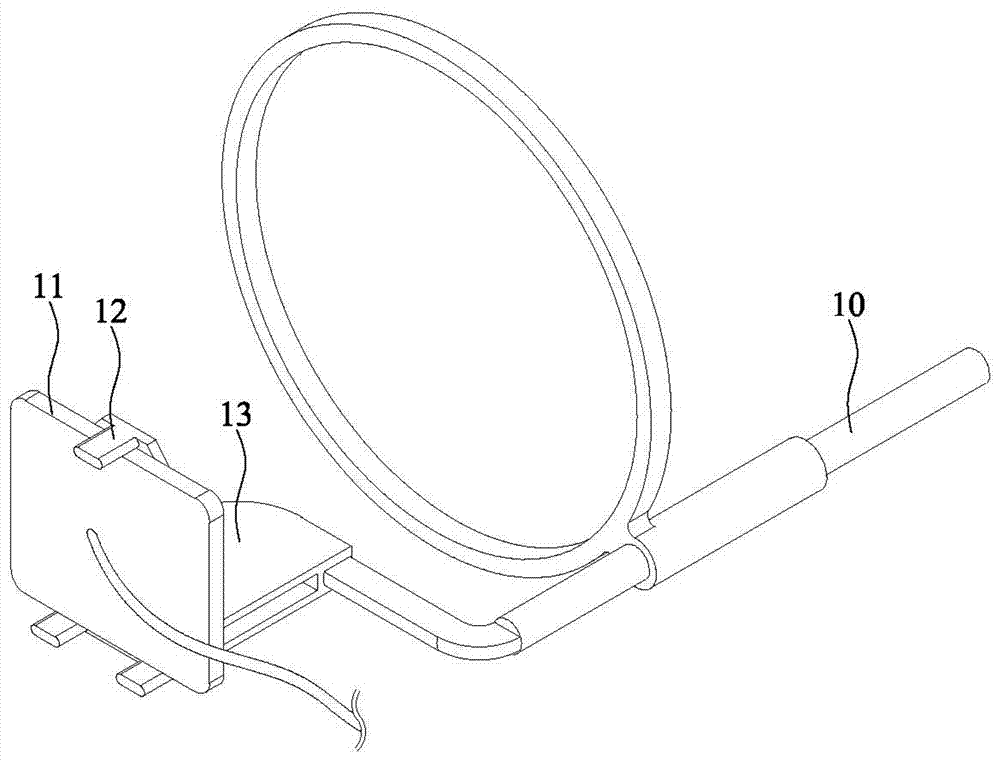

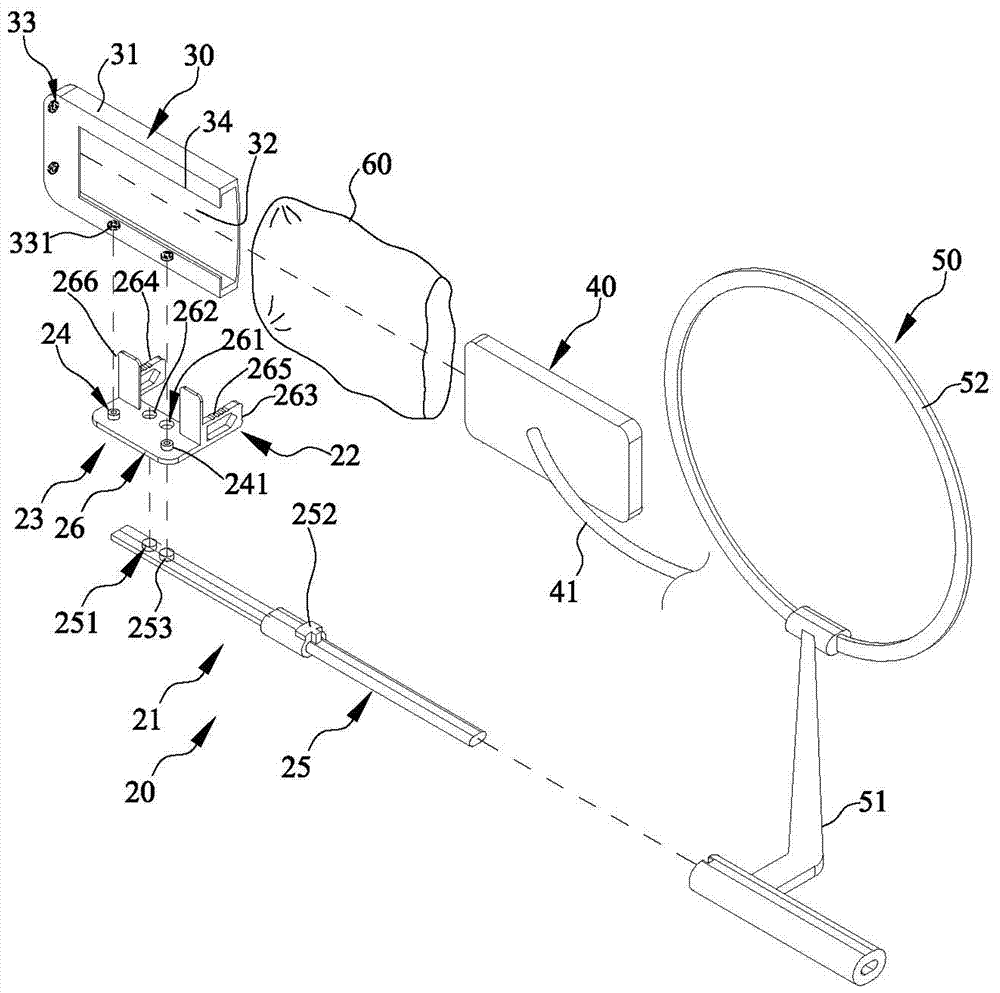

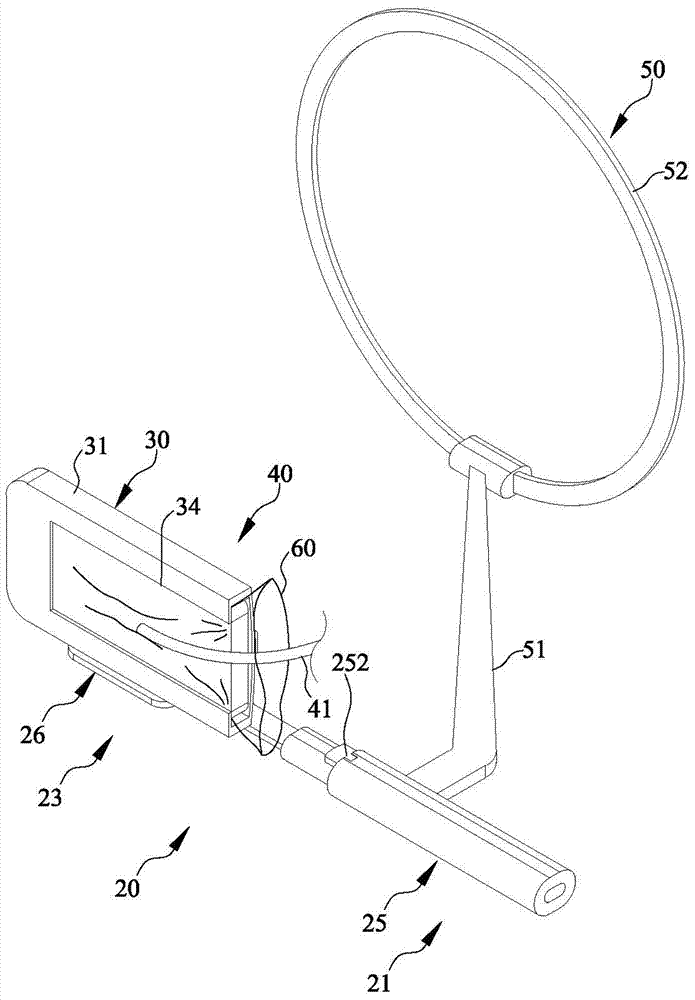

Handheld direct digital imaging sensing device with sheath

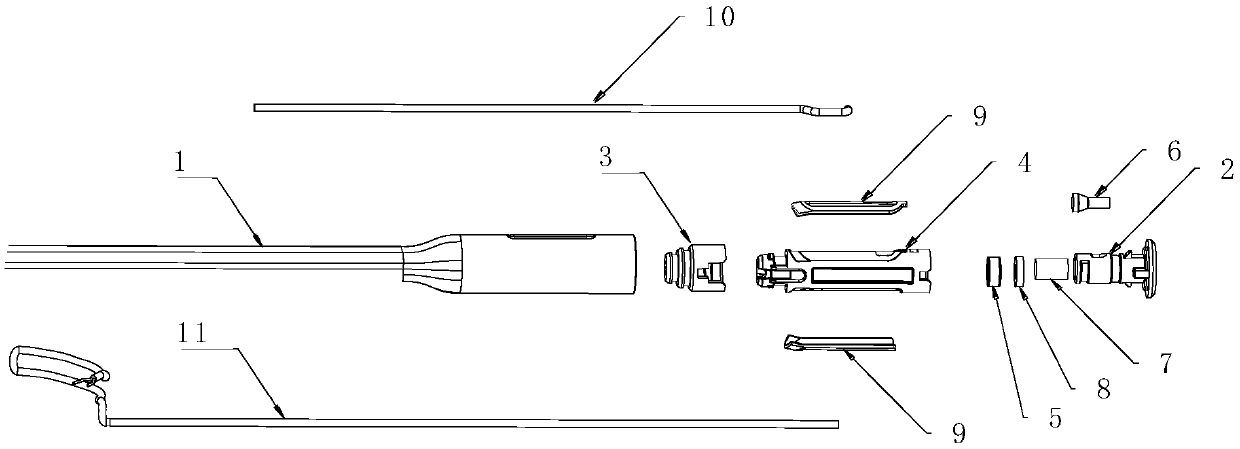

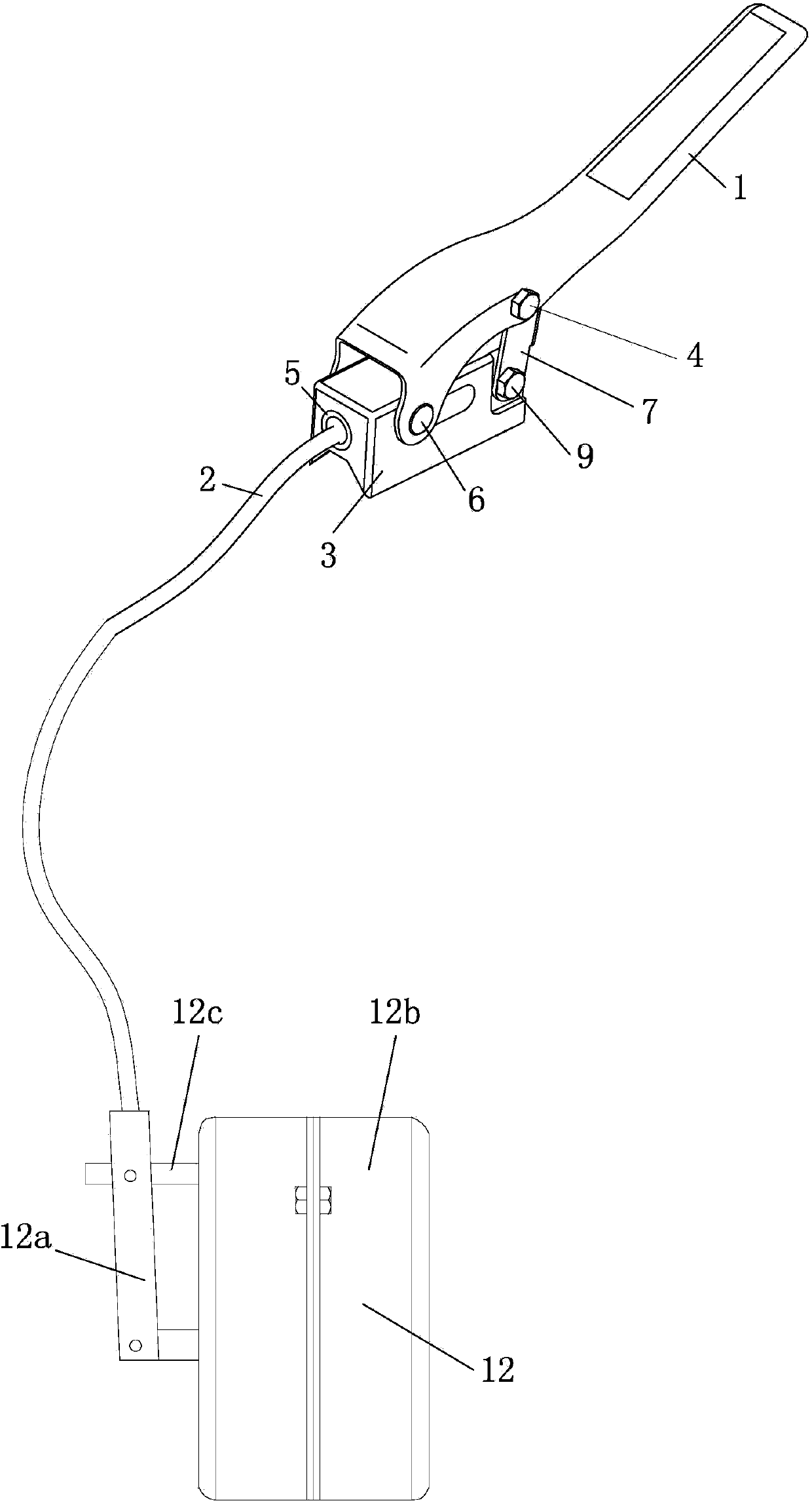

ActiveCN104224224ALess discomfortWon't increase the widthRadiation diagnostics for dentistryDigital imagingSoft materials

The invention relates to a handheld direct digital imaging sensing device with a sheath. The device comprises a connection bearing handle provided with a holding portion, a meshing portion and a bearing portion. At least one male connection assembly is arranged on the surface of the bearing portion. The sheath with a containing cavity is connected onto the male connection assembly in an assembly mode, a direct digital imaging sensor is arranged in the containing cavity, and a female connection assembly corresponding to the male connection assembly is arranged on the outer surface of the sheath. By means of the embedded connection assemblies, the sheath can be assembled at the tail end of the connection bearing handle, then the direct digital imaging sensor is sleeved by the sheath made of a soft material to reduce discomfort of a patient caused by the fact that the sensor is located in the mouth of the patient, the sheath or a sterilization sheath can be directly thrown after used, and the aim of achieving medical sanitation and safety is achieved.

Owner:DENSMART DENTAL CO LTD

Counterweight device and engineering vehicle provided with counterweight device

The invention belongs to the technical field of counterweight for engineering vehicles, and specifically relates to a counterweight device and an engineering vehicle provided with the counterweight device. The counterweight device comprises a counterweight box, and the counterweight box is rotatable and telescopic relative to the mounting position thereof. The counterweight value is adjustable, and the counterweight device can be compactly connected with a main engine of the engineering vehicle, so that the diversified demands are met and the overall width of the engineering vehicle cannot beincreased.

Owner:陈建军

Handheld direct digital imaging sensing device with sheath

ActiveCN104224224BLess discomfortWon't increase the widthRadiation diagnostics for dentistryDigital imagingSoft materials

The invention relates to a hand-held direct digital imaging sensing device with a sheath, which comprises an engaging handle, which is provided with a gripping portion, an occlusal portion and a bearing portion, and at least one male engaging component is arranged on the surface of the bearing portion; A sheath with a receiving cavity is assembled on the male joint component, a direct digital imaging sensor is arranged in the said storage cavity, and a female joint component corresponding to the male joint component is arranged on the outer surface of the sheath. The present invention utilizes a fitting joint assembly, so that the sheath can be assembled at the end of the joint handle, and then the direct digital imaging sensor is sheathed in the sheath of soft material, so as to slow down the pain of the patient in putting the sensor in the mouth. Uncomfortable, and the sheath or disinfection sheath can be discarded directly after use to achieve the purpose of medical and health safety.

Owner:DENSMART DENTAL CO LTD

A server chassis and server capable of reducing radiation

ActiveCN107635389BAvoid interferenceWon't increase the widthMagnetic/electric field screeningSupport structure mountingUSBMechanical engineering

The present invention relates to a server chassis capable of decreasing radiation and a server. The server chassis is characterized in that the server chassis includes a chassis, a small board and a main board; the small board is provided with a VGA connector and USB connectors; the chassis comprises a metal case and a front plastic case; a VGA opening for matching the VGA connector on the small board, USB openings for matching the USB connectors on the small board, and mounting holes are formed in the front plastic case; conductive fixing components can be plugged into the mounting holes in amatched manner, so that the small board can be installed on the front plastic case; fixing holes corresponding to the mounting holes of the front plastic case are formed in the small board; the conductive fixing components are plugged into the mounting holes and the fixing holes, so that the small board can be installed on the front plastic case; the front plastic case is subjected to conductivespraying treatment; and the metal case is fixedly connected with the front plastic case.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

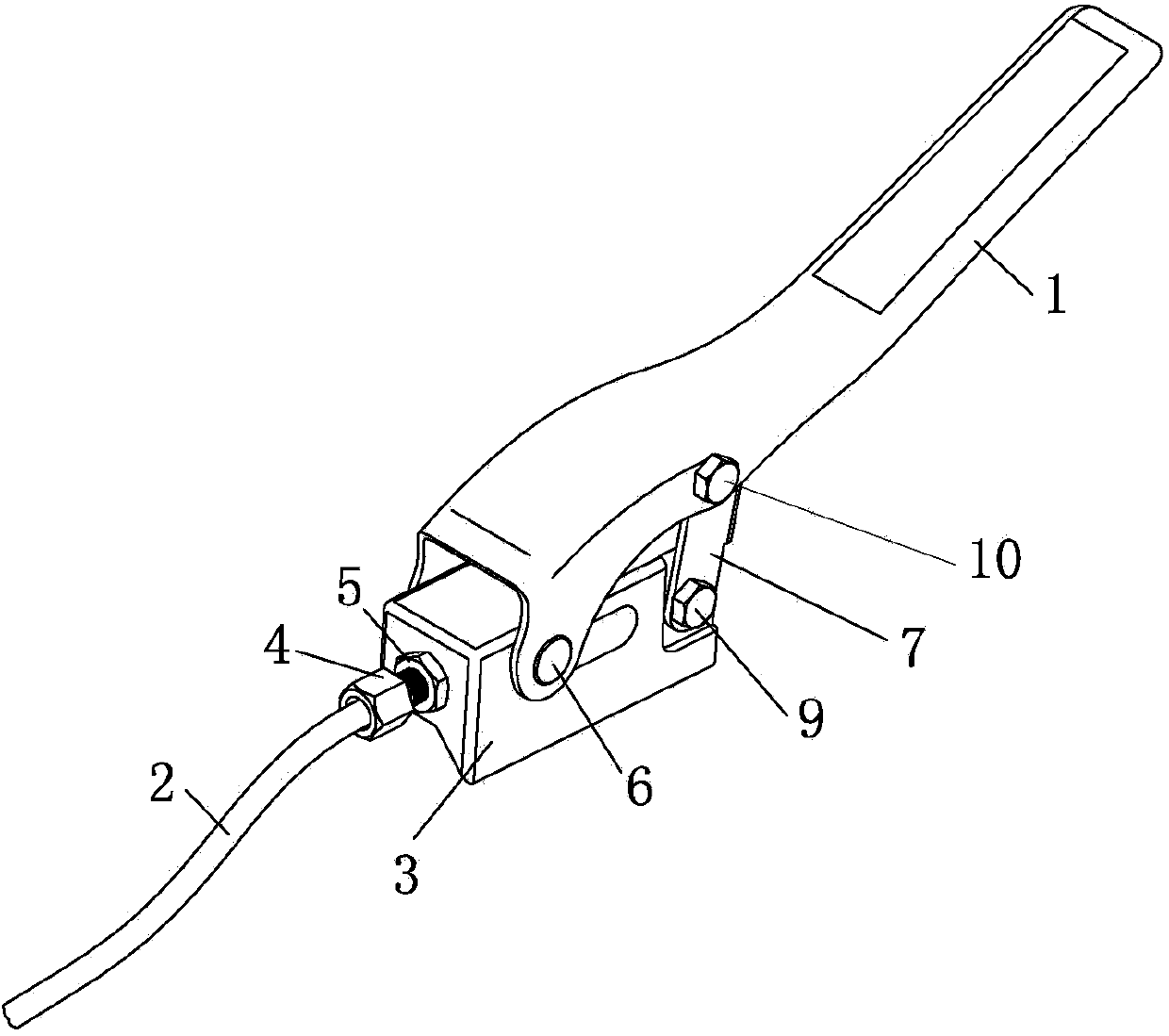

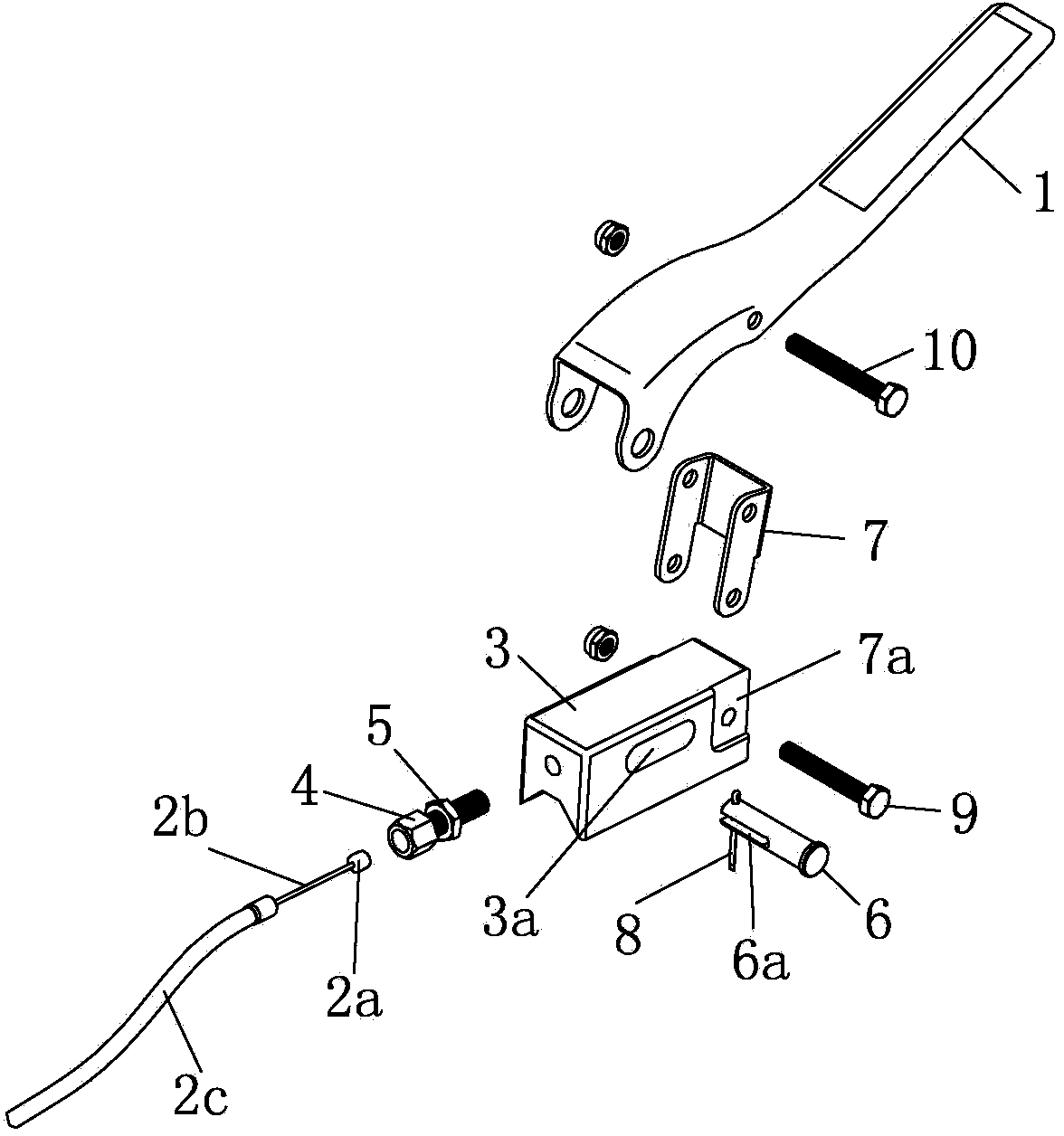

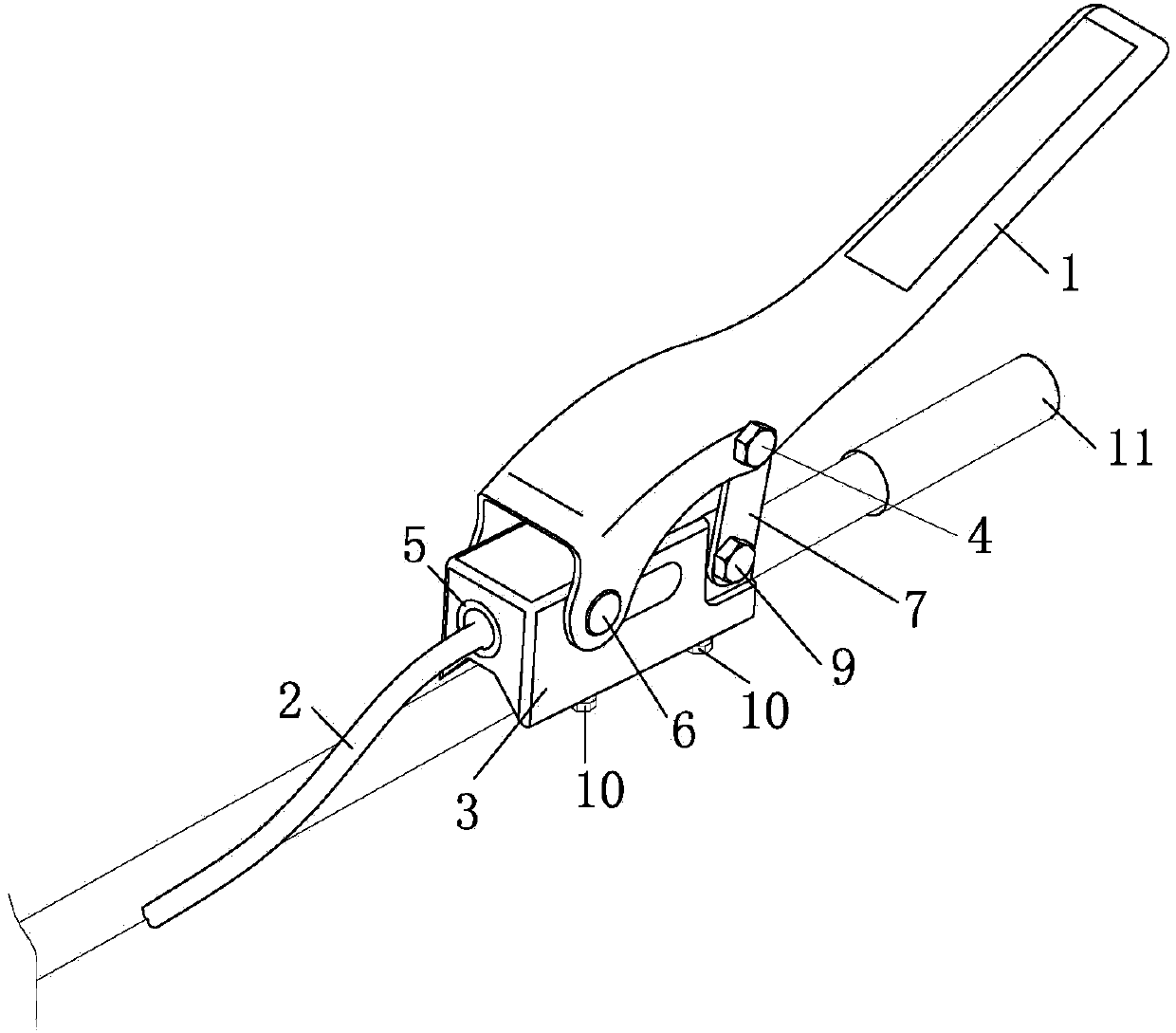

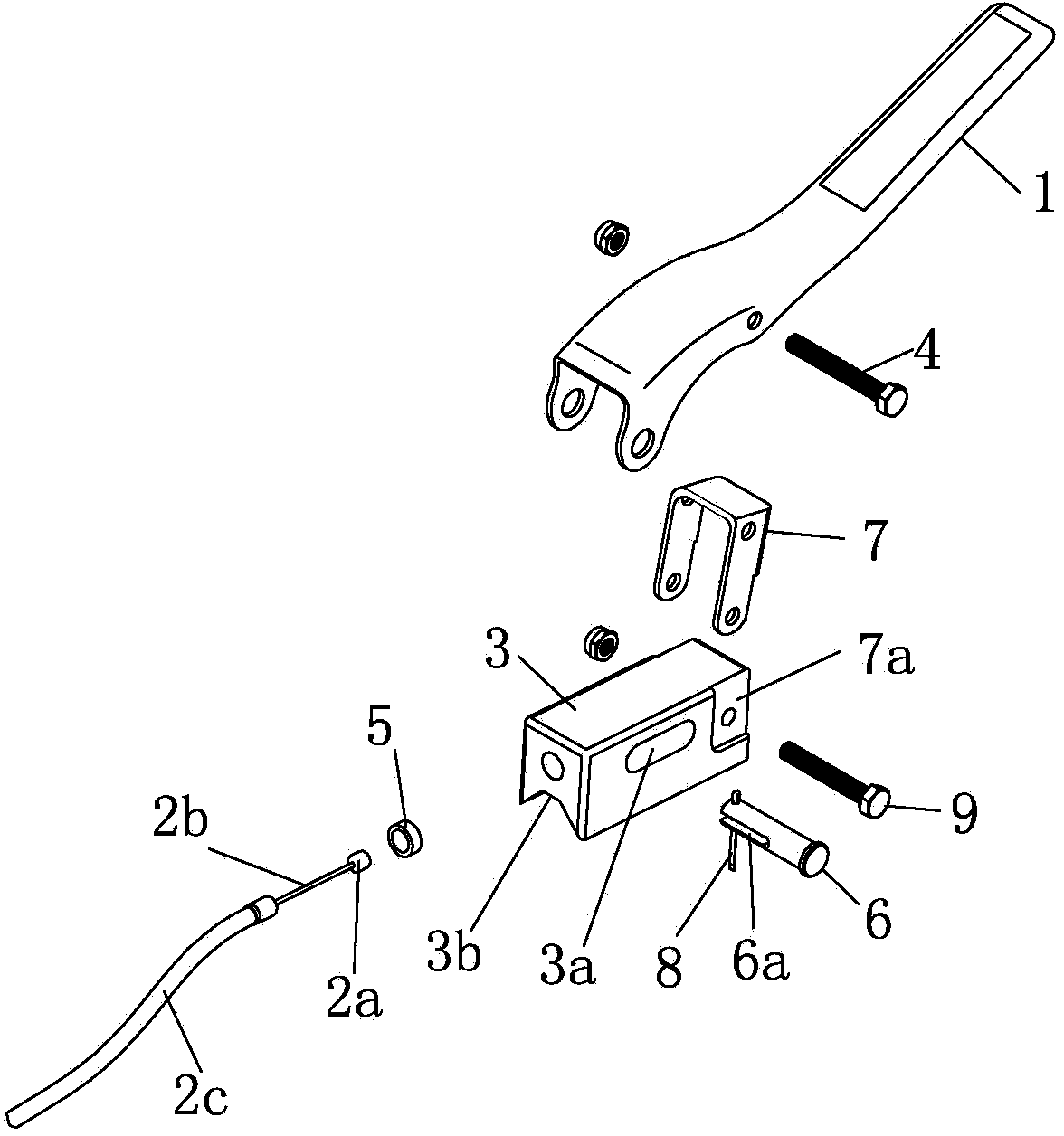

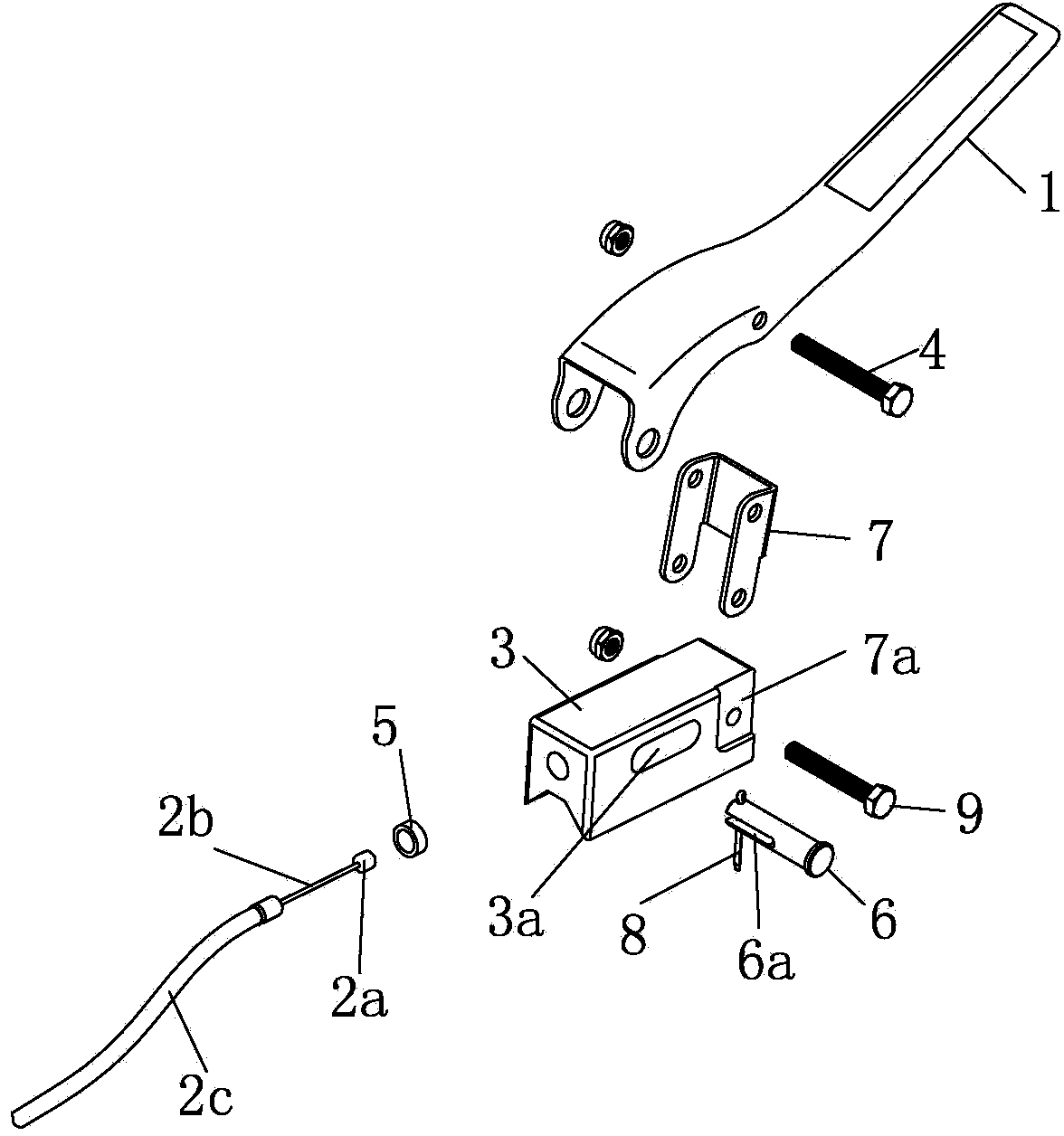

Handle assembly for controlling clutch of farming machine

The invention discloses a handle assembly for controlling the clutch of a farming machine. A fixed seat adopts a rectangular box body structure; a strip-shaped groove is formed in the fixed seat; a notch is formed in the rod part of a zipper fixing pin; the zipper fixing pin penetrates through the strip-shaped groove and then is prevented from falling off through a cotter pin inserted into the tail part of the zipper fixing pin; a zipper fixing bolt is mounted in a threaded hole formed in the front side wall of the fixed seat; the tail end of a clutch zipper penetrates through the zipper fixing bolt and is fixed in the notch of the zipper fixing pin through an anti-pulling-falling round head arranged at the tail end of the clutch zipper; a mounting bracket is formed by forwards bending the left end and the right end of a steel plate and covers the tail part of the fixed seat; the two side walls of the mounting bracket are positioned in corresponding notch grooves; the lower end of the mounting bracket is hinged to the fixed seat through a first bolt and nut assembly; the front end of a handle is hinged to the zipper fixing pin; the middle part of the handle is hinged to the upper end of the mounting bracket through a second bolt and nut assembly; the rear end of the handle gradually upwarps. The handle assembly is simple in structure, rapid in mounting, long in service life and high in reliability.

Owner:CHONGQING ZHONGHUA MACHINERY

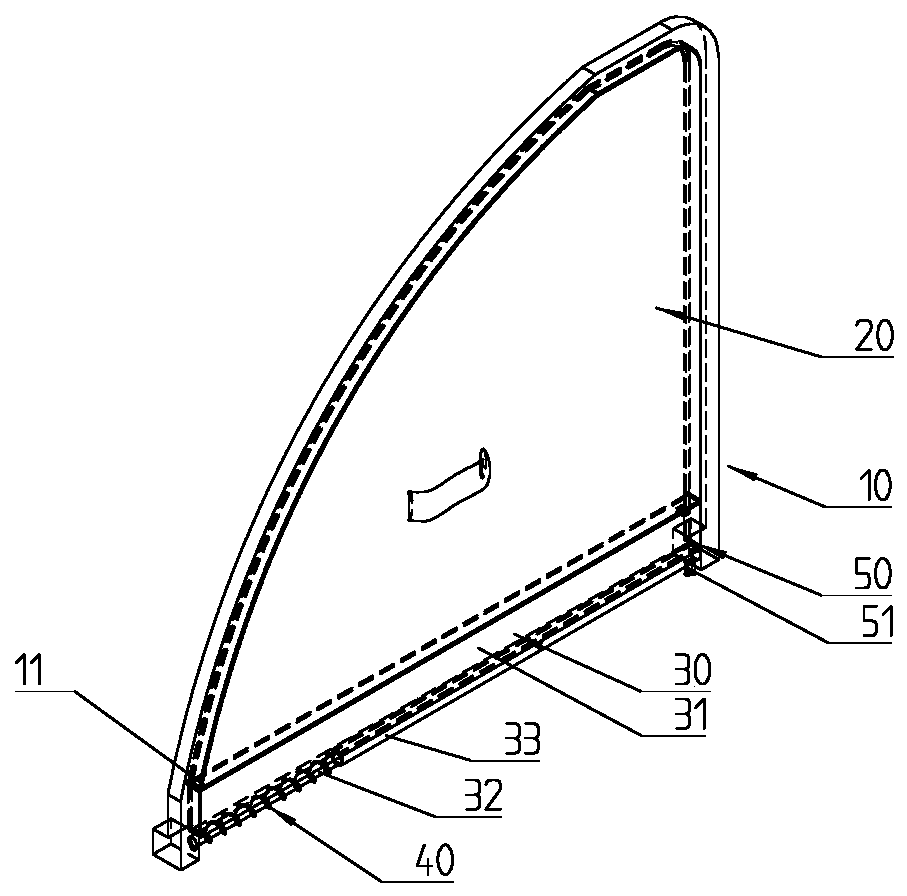

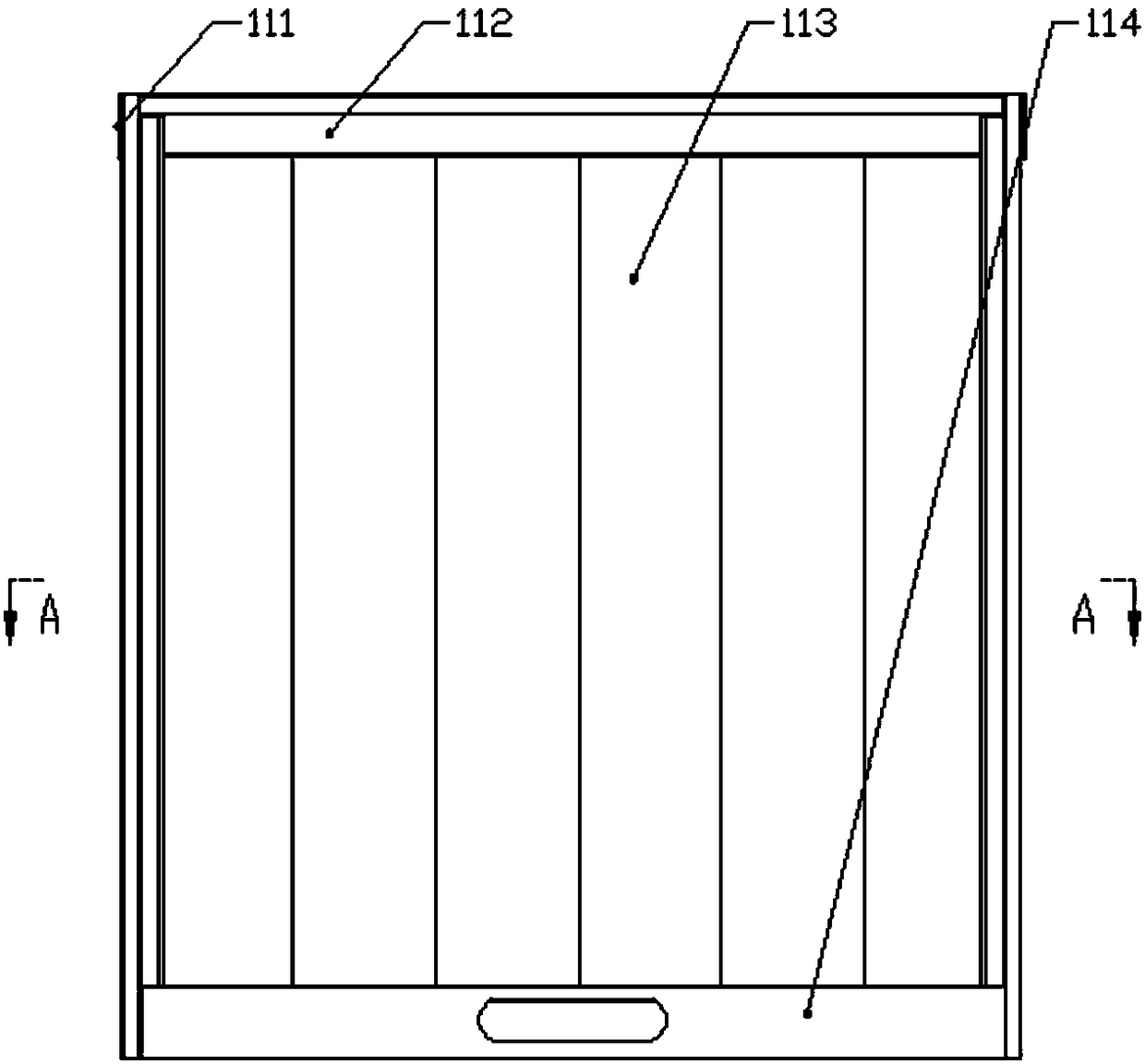

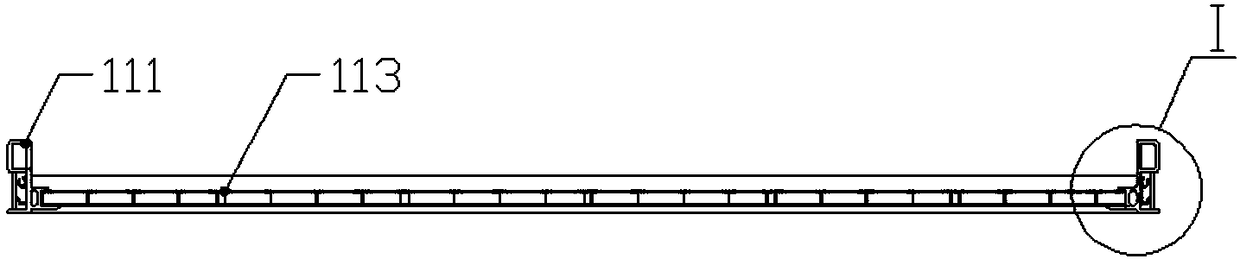

Backlight frame, backlight structure and liquid crystal display device

ActiveCN103869527BWon't increase the widthEasy to operateLighting support devicesNon-linear opticsLiquid-crystal displayEngineering

The invention discloses a backlight source frame, a backlight source structure and a liquid crystal display device. The backlight source frame includes a frame body and a plurality of limit structures arranged outside the frame body. One end of the limit structures is connected to the frame body. In the peelable connection, the other end is provided with a limiting portion, and the limiting surface of the limiting portion is coplanar with the side surface of the frame body and is located above the side surface of the frame body. In the present invention, a peelable limit structure is provided on the frame body of the backlight source frame, and the limit structure is used to limit the position of the display elements that need to be formed on the frame body when assembling. It can bring convenience of operation to the staff; the peelable setting of the limit structure does not increase the width of the frame body, and can meet the needs of narrow frame design.

Owner:BOE TECH GRP CO LTD +1

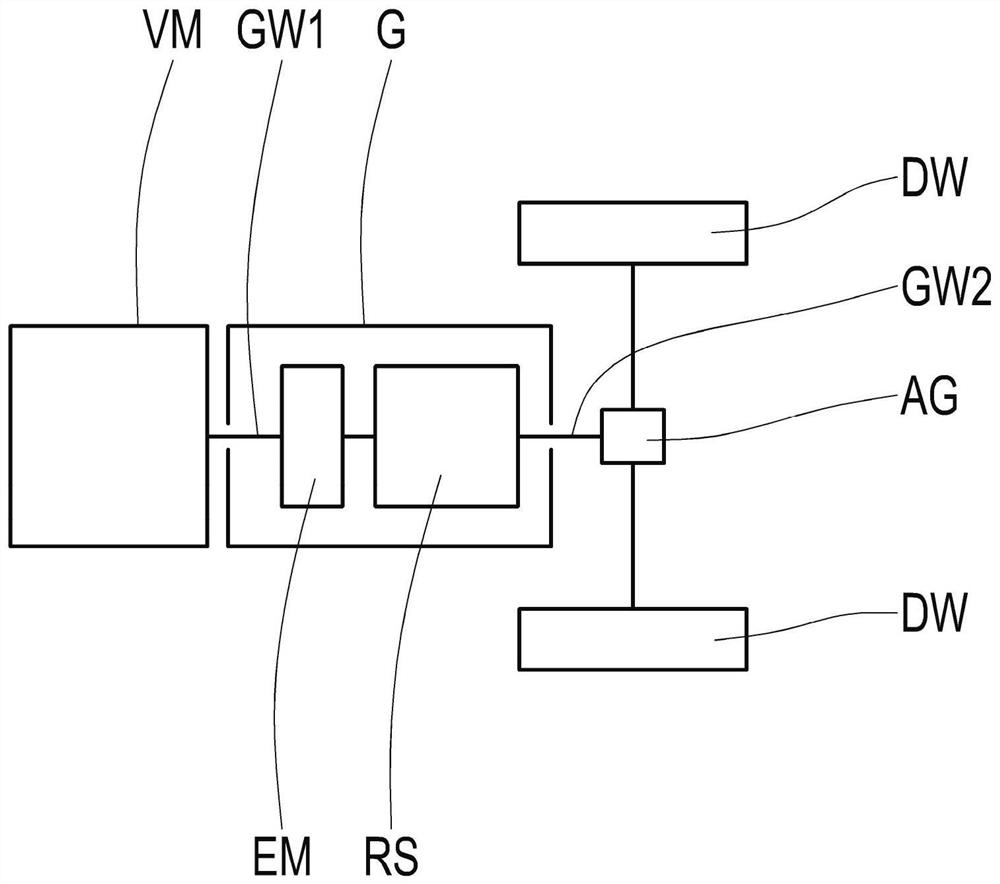

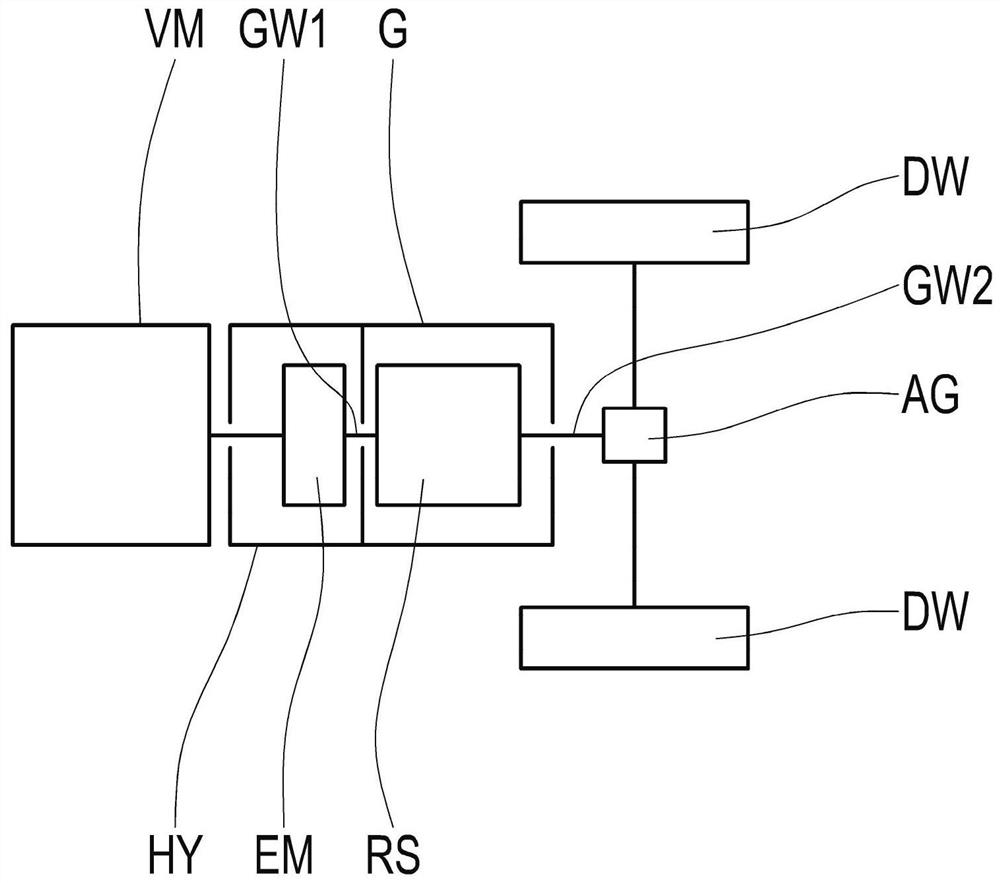

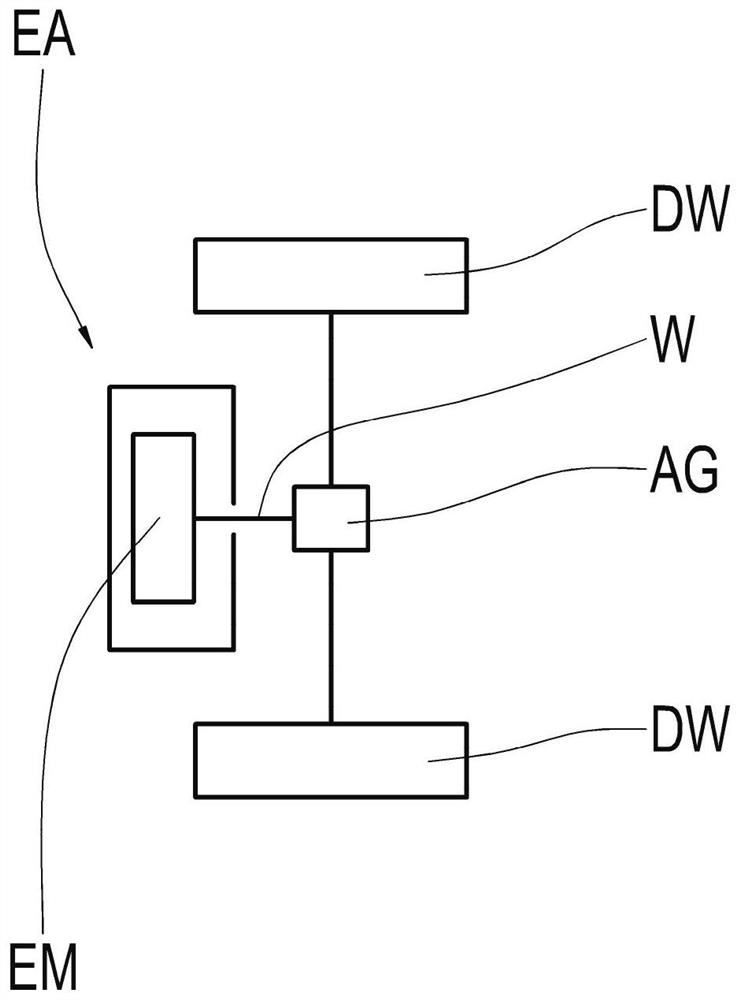

Arrangement for the liquid cooling of electric machine

PendingCN111799951AHigh thermal efficiencyWon't increase the widthHybrid vehiclesElectric propulsion mountingRotational axisElectric machine

The invention relates to a device for the liquid cooling of an electric machine (EM) having a stator (S) and a rotor (R), wherein the electric machine (EM) is surrounded by a cooling jacket (M) on theouter circumference thereof, wherein the cooling jacket has an inlet (M1) and an outlet (M2), the inlet (M1) being arranged spatially below the axis of rotation (RA) of the rotor (R) and the outlet (M2) being arranged spatially above the axis of rotation (RA) in the installed position of the electric machine (EM); the invention also relates to an electric machine (EM) having such a device. The invention also relates to a drive unit for a motor vehicle having the aforementioned electric machine (EM).

Owner:ZF FIEDRICHSHAFEN AG

Combination electric appliance with port connector

ActiveCN111146695BGuaranteed installationIncrease heightBus-bar/wiring layoutsSubstation/switching arrangement casingsControl theoryCircuit breaker

The invention relates to a combined electrical appliance with a port connector. The combined electrical appliance with a port connector includes a circuit breaker and a three-position switch on the incoming line side. The three-position switch on the incoming line side is arranged on the incoming line side of the circuit breaker; It also includes the cabinet body and port connector; the circuit breaker and the three-position switch on the incoming line side are all set in the cabinet; the port connector is set on the side of the three-position switch on the incoming line side away from the circuit breaker; the three-position switch on the incoming line side There is a connecting cylinder between the switch and the port connector, and the connecting cylinder is connected to the three-position switch on the incoming line side and the port connector; the three-position switch on the incoming line side is provided with a switch operating mechanism on one side in the horizontal direction. The switch operating mechanism is used to drive the three-position switch on the incoming line side to open, close and ground; at least a part of the switch operating mechanism in the vertical direction is located radially outside the connecting cylinder; the diameter of the connecting cylinder is smaller than that of the port connection The diameter of the barrel of the device is to avoid the part of the switch operating mechanism on the radially outer side of the connecting barrel.

Owner:HENAN PINGGAO GENERAL ELECTRIC CO LTD +2

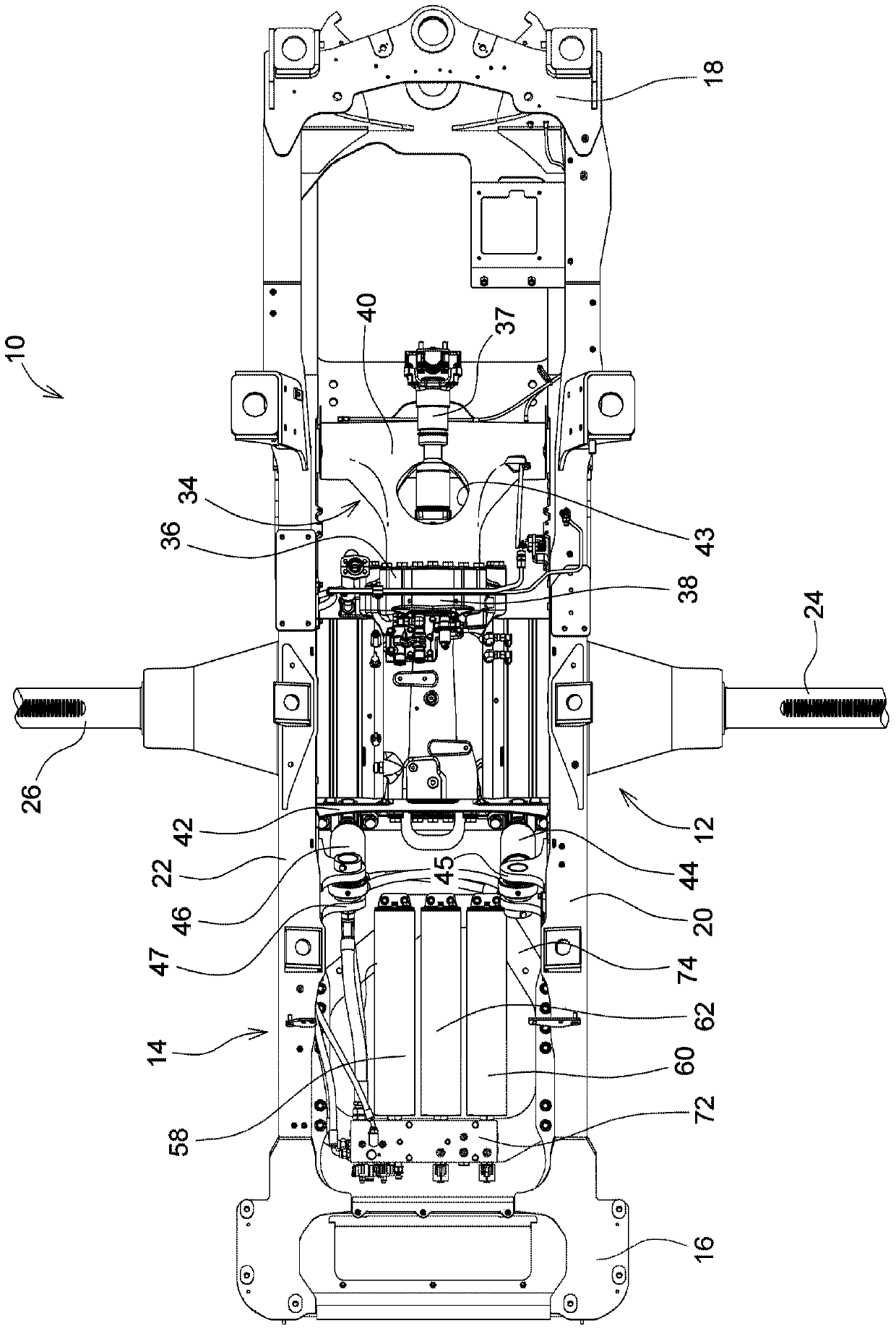

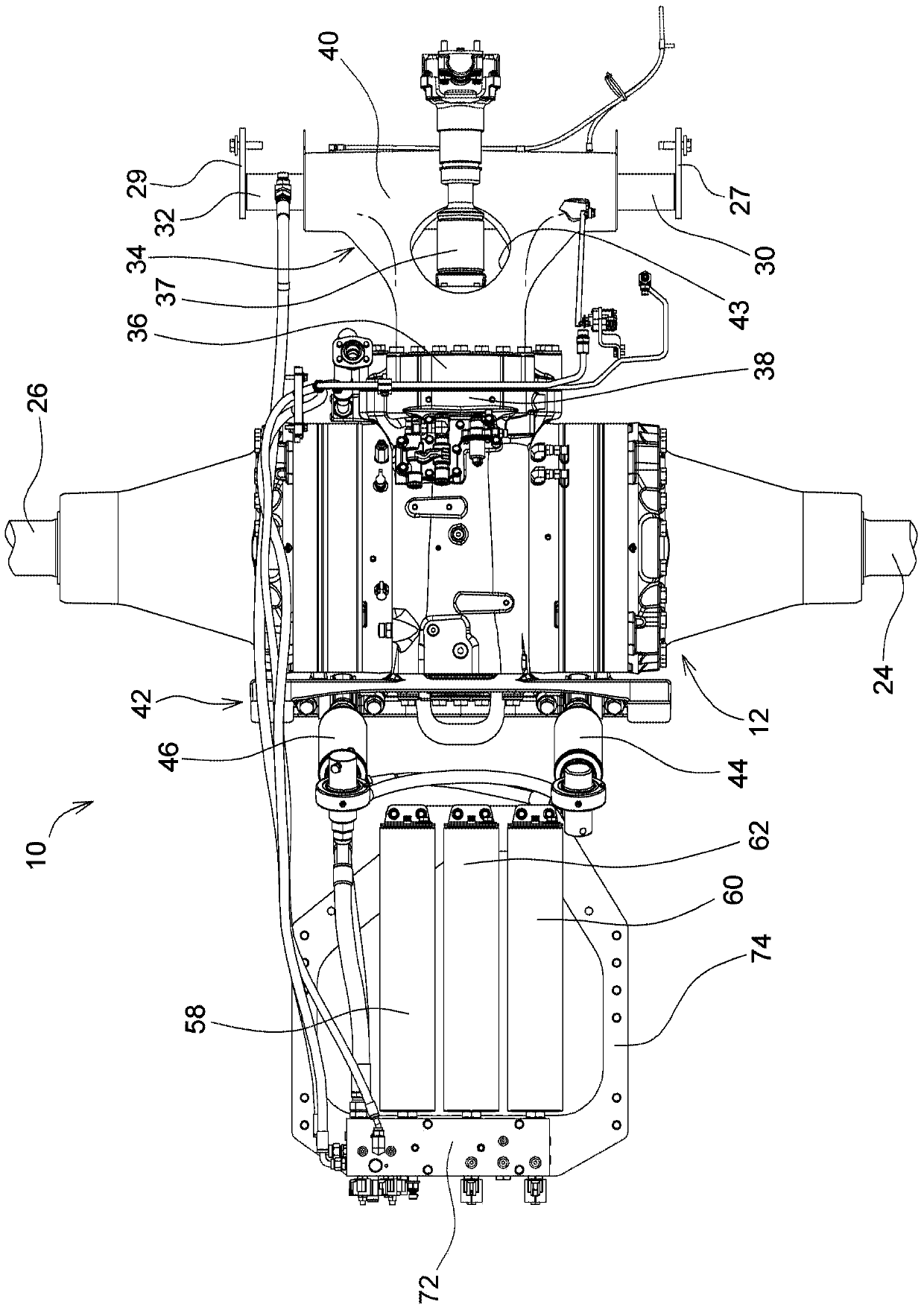

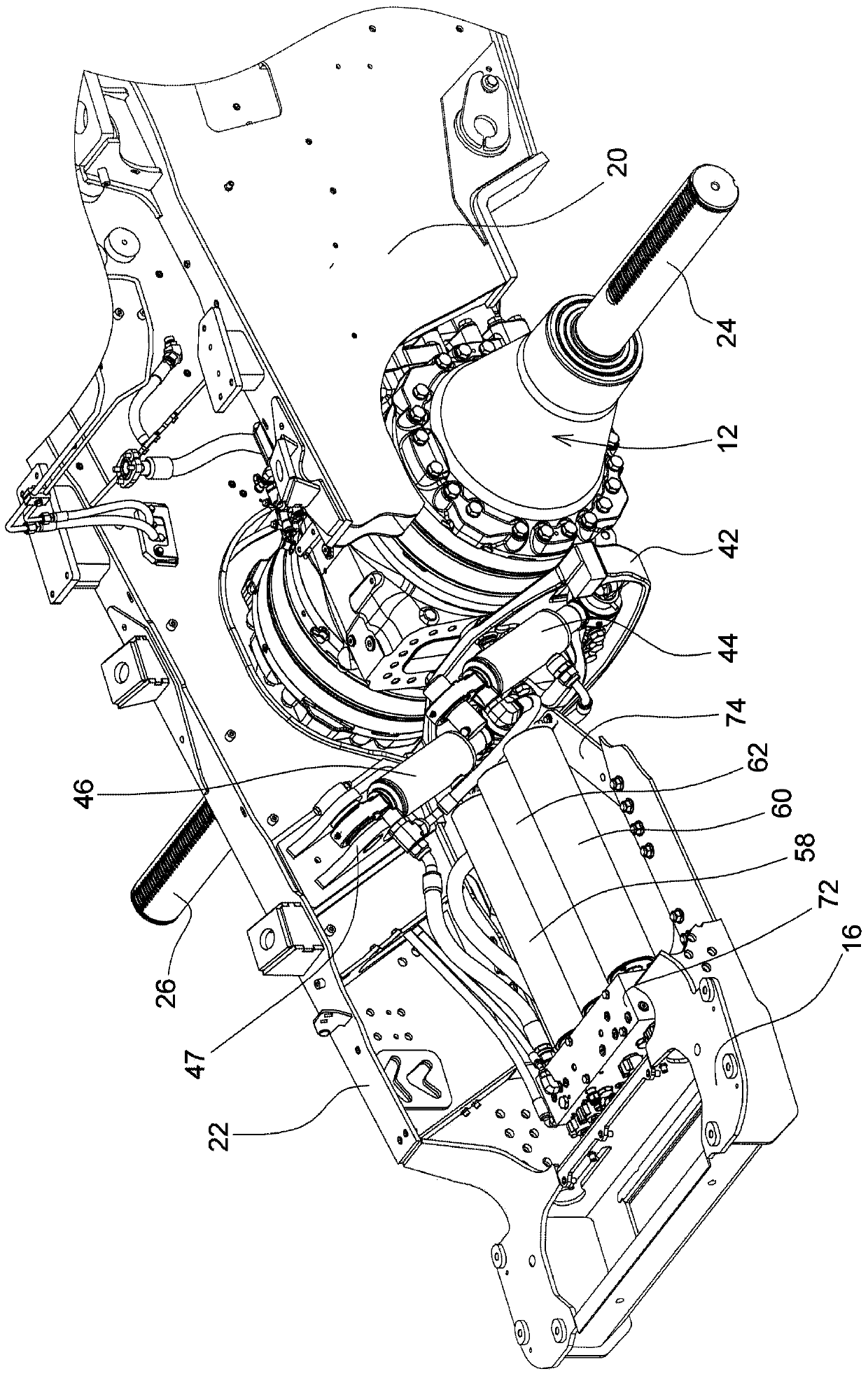

axle suspension

ActiveCN105365511BWon't increase the widthReduce power bounceResilient suspensionsVehicle springsHydraulic cylinderVehicle frame

An axle suspension supports the axle housing on the vehicle frame. The suspension arrangement includes left and right pivot rods attached to left and right frame elements. The suspension arm has a first end fixed to the rear end of the axle housing, and has a second end pivotally coupled to the left and right pivot rods. A variable length left hydraulic cylinder has an upper end pivotally coupled to the left frame member, and has a lower end pivotally coupled to the front end of the axle housing. A variable length right hydraulic cylinder has an upper end pivotally coupled to the right frame member, and has a lower end pivotally coupled to the front end of the axle housing. The left and right hydraulic cylinders are hydraulically connected in parallel.

Owner:DEERE & CO

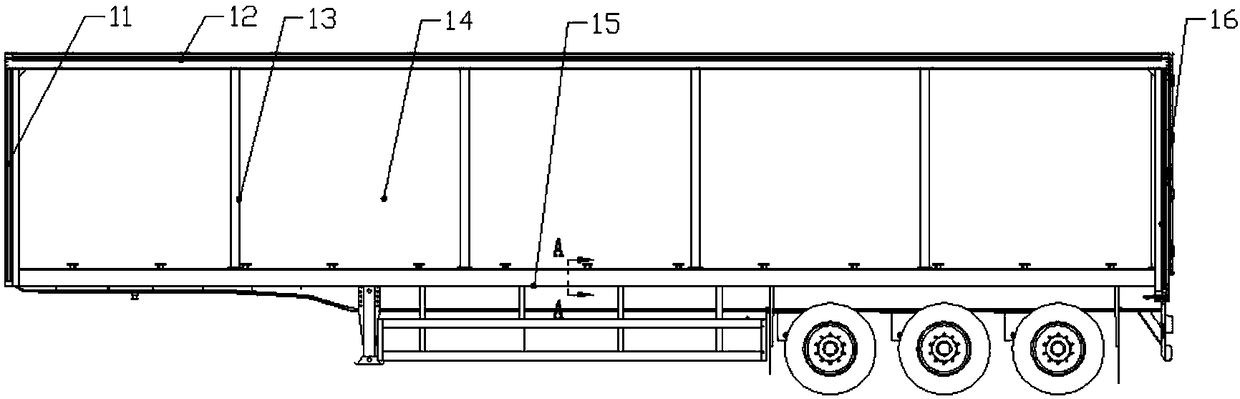

Aluminum-alloy lateral-curtain-semitrailer profile standing column and front box assembly thereof

PendingCN108100051AReduce weightImprove corrosion resistanceTractor-trailer combinationsLoading-carrying vehicle superstructuresAgricultural engineeringWall plate

The invention discloses an aluminum-alloy lateral-curtain-semitrailer profile standing column and a front box assembly thereof, is applicable to the field of trackless land vehicles, and aims to overcome the defects that a lateral-curtain-semitrailer profile standing column is normally of a steel structure, and the standing column is heavy and poor in corrosion resistance. The profile standing column comprises eight aluminum-alloy profile standing column feature faces, front box assembly profile standing columns, a front upper crossbeam, front wall plates, a front lower crossbeam, limit platesand curtain cloth tightening tubes. The aluminum-alloy lateral-curtain-semitrailer profile standing column and the front box assembly thereof can reduce the weight of the standing column and the front box assembly and increase corrosion resistance.

Owner:LIAONING ZHONGWANG SPECIAL VEHICLE MFG

Mounting structure of clutch handle mechanism and grab bar for farming machine

The invention discloses a mounting structure of a clutch handle mechanism and a grab bar for a farming machine. The clutch handle mechanism comprises a handle, a clutch stay wire, a mounting seat, a stay wire fixing pin and a mounting bracket, wherein the mounting seat adopts an aluminium rectangular box body structure; the stay wire fixing pin penetrates through a strip-shaped groove and then is prevented from falling off through a cotter pin inserted into the tail part of the stay wire fixing pin; the tail end of the clutch stay wire penetrates through the front wall of the mounting seat, stretches into the inner cavity of the mounting seat, and is fixed in the notch of the stay wire fixing pin through an anti-pulling-falling round head arranged at the tail end of the clutch stay wire; the mounting bracket is formed by downwards bending the left end and the right end of a steel plate, is integrally door-shaped and covers the tail part of the mounting seat; the two side walls of the mounting bracket are positioned in corresponding notch grooves; the lower end of the mounting bracket is hinged to the mounting seat; the front end of the handle is hinged to the stay wire fixing pin; the middle part of the handle is hinged to the upper end of the mounting bracket; the bottom of the mounting seat arches upwards to form an isosceles trapezoid cavity for accommodating the grab bar. The mounting structure is simple in structure, rapid in mounting, long in service life and high in reliability.

Owner:CHONGQING ZHONGHUA MACHINERY

Anti-rollover transportation forklift

PendingCN114249279AWon't increase the widthStable supportVehicle fittings for liftingLifting devicesControl theorySupport surface

The anti-rollover transportation forklift comprises a forklift body, the forklift body is provided with an abutting piece and a first driving device used for driving the abutting piece to stretch out and retract in the lateral direction, and the head of the abutting piece is used for being connected with an external vertical supporting face in an abutting mode after stretching out in the lateral direction. According to the transportation forklift, when a carried object needs to be lifted or laterally moved, the first driving device can drive the abutting piece to laterally stretch out to abut against external vertical supporting faces such as a wall face and a goods shelf, so that stable supporting can be formed for the transportation forklift, the transportation forklift is effectively prevented from inclining and turning over, and the transportation forklift is safer and more reliable; and the transportation forklift can adapt to a narrow moving road and a higher storage position, so that the storage density can be improved, the structure of a storage system can be simplified, and the storage cost can be reduced.

Owner:DONGGUAN LISHENG MACHINERY EQUIP

Mobile terminal, circuit board assembly and preparation method of circuit board assembly

ActiveCN108925039BWon't increase the widthSmall footprintPrinted circuit assemblingPrinted circuit aspectsElectrical connectionHot melt

The invention discloses a circuit board assembly. The circuit board assembly comprises a touch switch, a hot melting rubber ring and a circuit board, wherein the touch switch comprises a first pin anda second pin, the hot melting rubber ring is arranged on the touch switch, the first pin and the second pin are arranged in a region encircled by the hot melting rubber ring, a first connection groove and a second connection groove are formed in the circuit board, the first connection groove is opposite to the first pin, the second connection groove is opposite to the second pin, a surface, facing the circuit board, of the touch switch and a panel of the circuit board are pasted and fixed by the hot melting rubber ring, an external connection end of the first pin props against a bottom wall of the first connection groove and is electrically connected with a bottom wall of the first connection groove, and an external connection end of the second pin props against a bottom wall of the second connection groove and is electrically connected with the bottom wall of the second connection groove. With the circuit board assembly disclosed by the scheme, the problems of relatively high construction cost of the touch switch arranged on the circuit board by a surface-mounting process and relatively large width of the formed circuit board assembly can be solved. The invention also discloses amobile terminal and a fabrication method of the circuit board assembly.

Owner:VIVO MOBILE COMM CO LTD

High-performance handle type clutch assembly

InactiveCN104179825ASimple structureWon't increase the widthMechanical actuated clutchesClutch controlEngineering

The invention discloses a high-performance handle type clutch assembly. The high-performance handle type clutch assembly comprises a clutch and a clutch control handle mechanism, wherein the clutch control handle mechanism comprises a handle, a clutch stay wire, a mounting seat, a stay wire fixing pin and a mounting frame; a strip-shaped groove is formed in the mounting seat; after penetrating through the strip-shaped groove, the stay wire fixing pin passes through a cotter pin that is inserted at the tail part of the stay wire fixing pin, so as to prevent falling off ; the front end of the clutch stay wire is connected onto a clutch arm of the clutch; the tail end of the clutch stay wire penetrates through the front wall of the mounting base, extends to the inner cavity of the mounting base and is fixed inside a notch of the stay wire fixing pin through a pull-off prevention round head arranged at the tail end of the clutch stay wire; the mounting frame is covered at the tail part of the mounting base; two side walls of the mounting frame are positioned in corresponding notch grooves; the lower end of the mounting frame is hinged to the mounting base; the front end of the handle is hinged to the stay wire fixing pin; the middle part of the handle is hinged to the upper end of the mounting frame; a base plate of the mounting base is mounted and fixed with the grab rail; the structure is simple; the installation is fast and convenient; the service life is long and the reliability is high.

Owner:CHONGQING ZHONGHUA MACHINERY

Automatic retractable soft awning for wagon box

The invention discloses an automatic retractable soft awning for a wagon box, which is characterized in that an awning cloth winding component, a soft awning movable support and an automatic opening-closing control device are arranged on an open wagon box body, wherein an awning cloth is wound on the awning cloth winding component; the soft awning movable support comprises a U-shaped short connecting rod and a U-shaped long connecting rod; two end points of the short connecting rod are hinged with the lower parts of two ends of the long connecting rod; two end points of the long connecting rod are hinged with torsion spring components arranged at the left side and the right side of the wagon box body in the automatic opening-closing control device; a cross rod of the short connecting rod is connected with the most front end of the awning cloth in a winding drum; and a cross rod of the long connecting rod is positioned above the awning cloth. The invention has reasonable design and good enclosing effect, can effectively prevent dust and rain, and can prevent the loaded bulk goods from leaking during travelling. The invention adopts the soft awning for covering, and the soft awning has light weight, compact structure and certain elasticity, has relaxed limitation on the volume and shape of loaded goods, can not increase the width of the wagon body and excessively increase the load capacity, and improves the loading efficiency of wagons.

Owner:HEFEI UNIV OF TECH

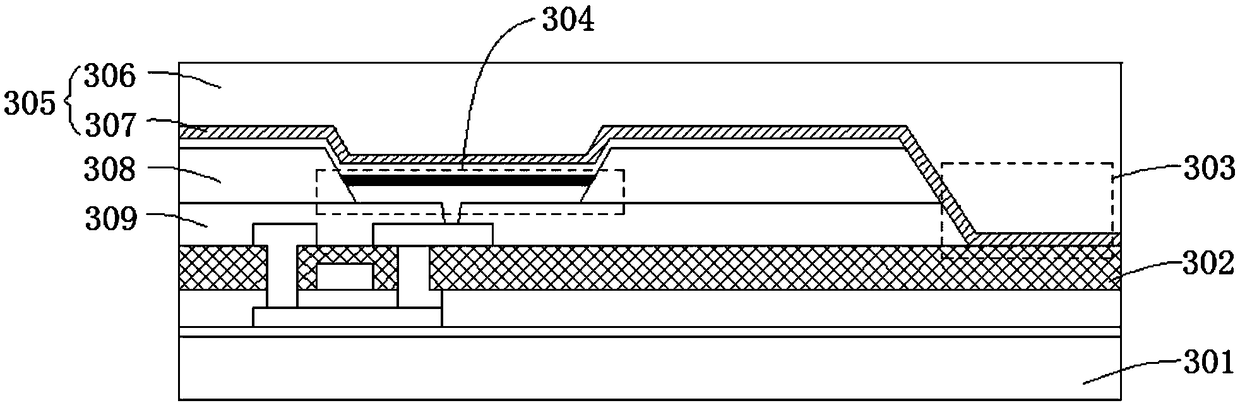

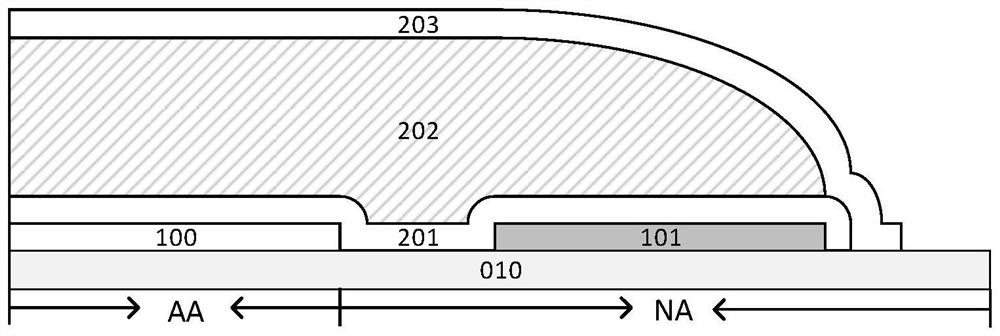

Display panel and manufacturing method thereof

PendingCN113488598AWon't increase the widthPrevent overflowSolid-state devicesSemiconductor/solid-state device manufacturingUltraviolet lightsEngineering

The invention relates to a display panel and a manufacturing method thereof. The display panel comprises a display area and a frame area, and comprises an array substrate, a pixel layer comprising a first pixel located in the display area and a second pixel located in a non-display area and arranged on one side of the array substrate, a first inorganic layer arranged on the side, away from the array substrate, of the pixel layer and covering the pixel layer, an organic layer with the orthographic projection on the array substrate at least covering the orthographic projection of the first pixel on the array substrate and arranged on the side, away from the pixel layer, of the first inorganic layer, and a second inorganic layer arranged on the side, away from the first inorganic layer, of the organic layer and covering the organic layer and the first inorganic layer. The second pixel includes an ultraviolet light emitting layer. By arranging the ultraviolet light emitting layer, the organic layer located on the side, away from the array substrate, of the second pixel in the frame area is preferentially cured, the organic layer is prevented from overflowing in the direction away from the display area, meanwhile, the width of the frame is not increased, and the narrow frame effect is better achieved.

Owner:HEFEI VISIONOX TECH CO LTD