Data processing method, system on chip and electronic equipment

A system-on-chip and data processing technology, applied in the architecture with a single central processing unit, general-purpose stored program computer, internal/peripheral computer component protection, etc., can solve the problem of low switching efficiency and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

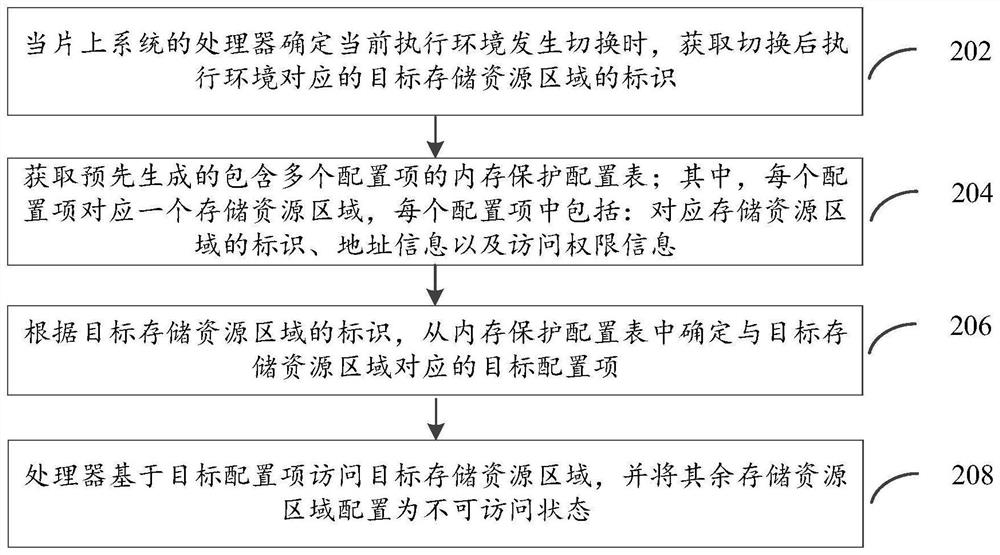

[0034] refer to figure 2 , figure 2 It is a flow chart of the steps of a data processing method according to Embodiment 1 of the present application. The data processing method is applied to a system-on-chip that supports multiple execution environments, and each execution environment corresponds to at least one storage resource area in the system-on-chip. The method include:

[0035] Step 202, when the processor of the system-on-chip determines that the current execution environment is switched, it acquires the identifier of the target storage resource area corresponding to the execution environment after the switch.

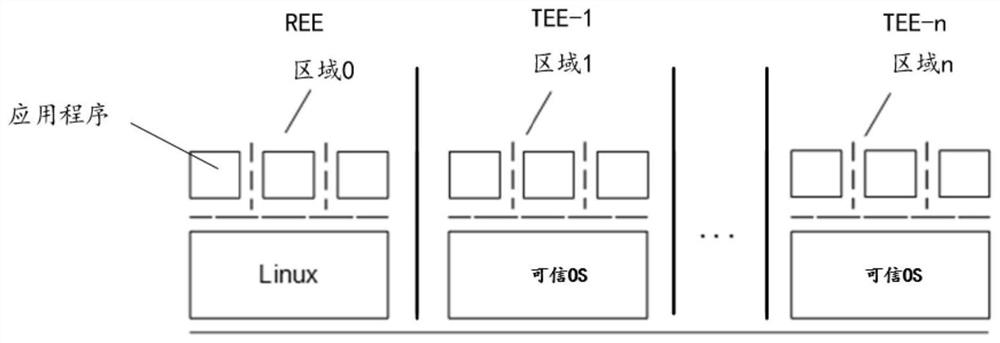

[0036] Specifically, in this embodiment of the present application, the identifiers of each target storage resource area may be preset, for example figure 1 As shown, the identifiers of the storage resource areas corresponding to REE are: area 0, the identifiers of the storage resource areas corresponding to TEE-1 are: area 1, ..., the identifiers of the stor...

Embodiment 2

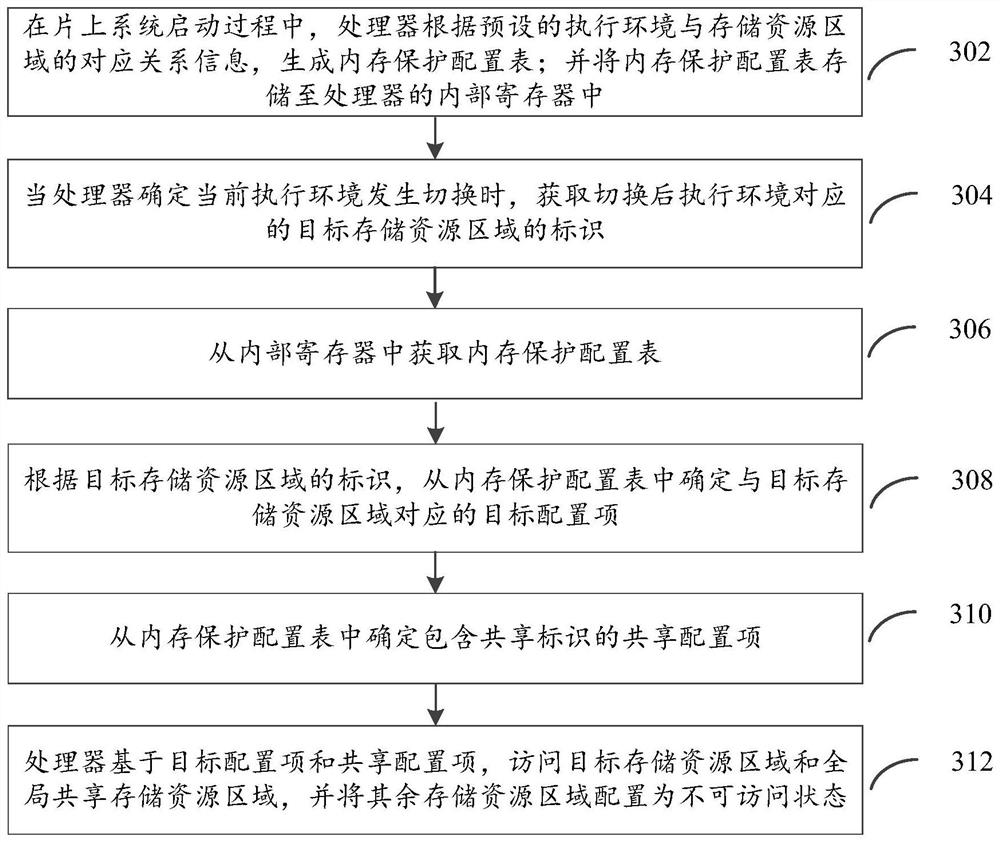

[0048] refer to image 3 , image 3 It is a flowchart of steps of a data processing method according to Embodiment 2 of the present application. Specifically, the data processing method provided in this embodiment is applied to a system-on-chip supporting multiple execution environments, each execution environment corresponding to at least one storage resource area in the system-on-chip, and includes the following steps:

[0049] Step 302: During the system-on-chip startup process, the processor generates a memory protection configuration table according to the preset correspondence information between the execution environment and the storage resource area; and stores the memory protection configuration table in an internal register of the processor.

[0050] Wherein, each configuration item corresponds to a storage resource area, and each configuration item includes: the identifier, address information and access authority information of the corresponding storage resource a...

Embodiment 3

[0075] refer to Figure 5 , shows a schematic structural diagram of a system-on-chip supporting multiple execution environments according to Embodiment 3 of the present application. The specific embodiments of the present application do not limit the specific implementation of the system-on-chip.

[0076] like Figure 5 As shown, the system-on-chip may include: a processor (processor) 502 , a communications interface (Communications Interface) 504 , a memory (memory) 506 , and a communication bus 508 .

[0077] in:

[0078] The processor 502 , the communication interface 504 , and the memory 506 communicate with each other through the communication bus 508 .

[0079] The memory 506 includes a plurality of storage resource areas 510; each execution environment corresponds to at least one storage resource area 510 in the memory 506;

[0080] The communication interface 504 is used to communicate with other devices.

[0081] The processor 502 is configured to execute the prog...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com