Semiconductor device

A technology of semiconductors and transistors, which is applied in the field of semiconductor devices and can solve problems such as wiring conflicts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

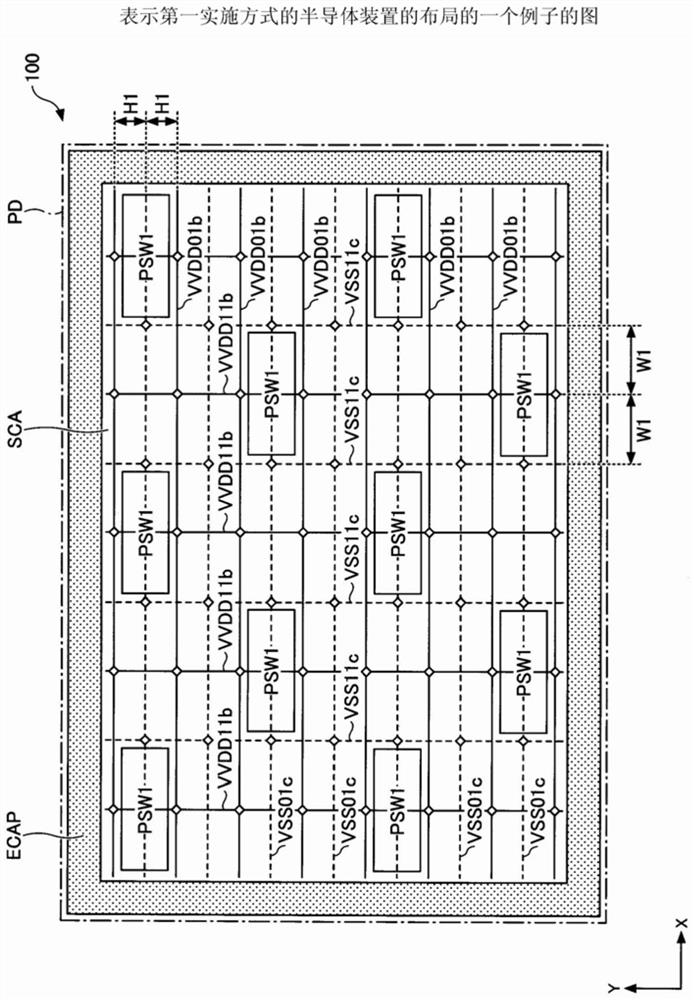

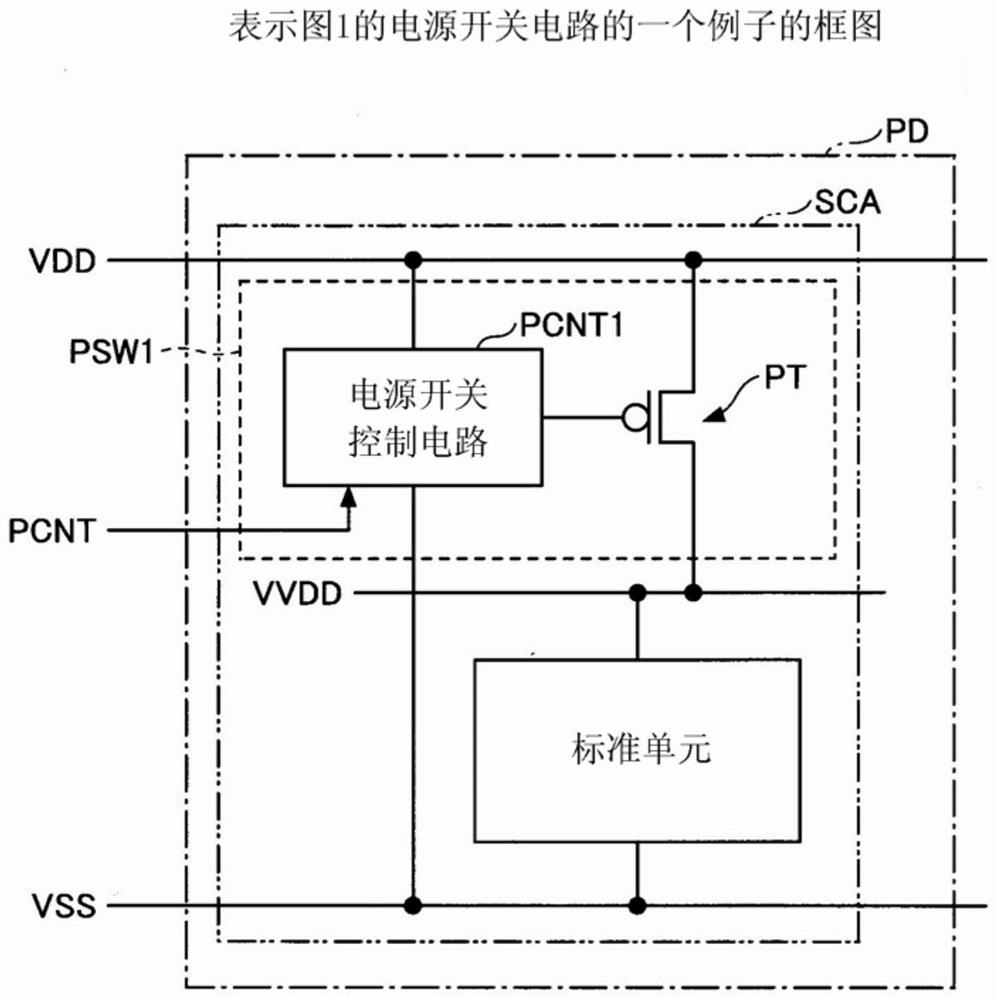

[0029] figure 1 An example of the layout of the semiconductor device in the first embodiment is shown. figure 1 The semiconductor device 100 shown has, for example, at least one power domain PD. A standard cell area SCA in which a plurality of standard cells (not shown) are arranged is provided in the power domain PD. Although not particularly limited, the transistor mounted on the semiconductor device 100 is a finFET. finFET in Figure 5 explained in. The standard cell area SCA is an example of a first area where logic circuits can be configured.

[0030] An end cap ECAP shown in a hatched pattern is arranged around the standard cell area SCA. The end cap ECAP has a dummy gate electrode or a dummy transistor not shown. In addition, in the standard cell area SCA, in figure 1 The longitudinal direction, that is, the Y direction, is alternately arranged with an interval H1. figure 1 The virtual power supply line VVDD01b and the ground line VSS01c extending in the lateral...

no. 2 approach

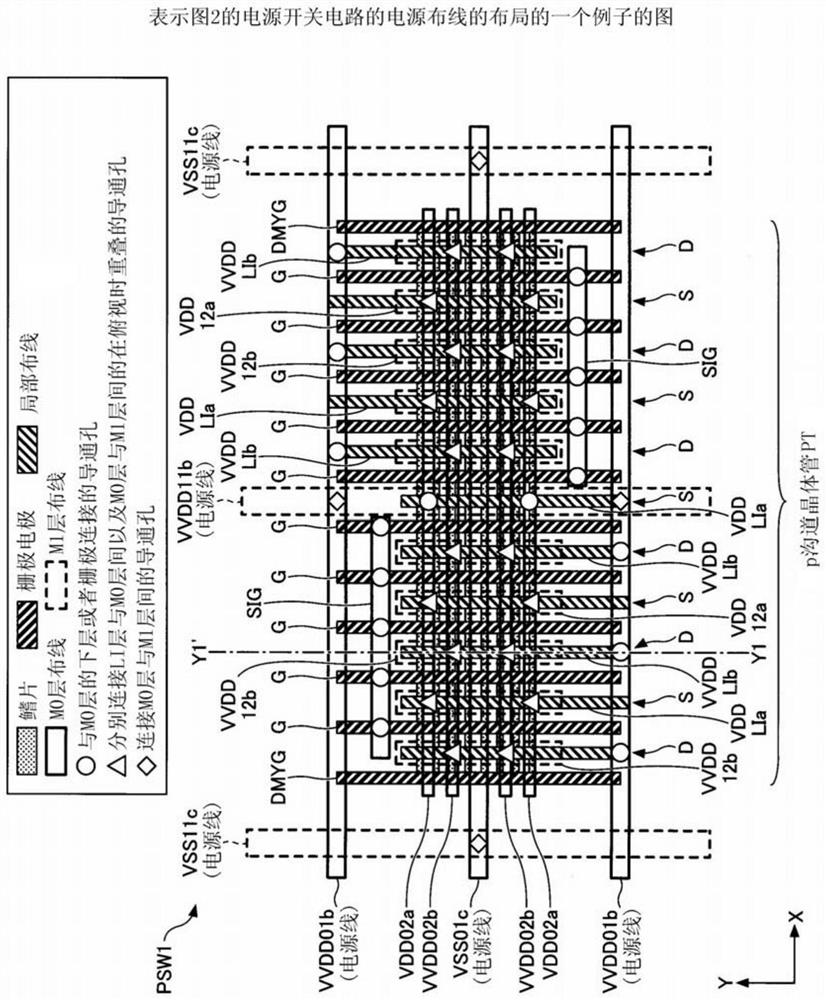

[0072] Figure 7 An example of the layout of the power switch circuit of the semiconductor device in the second embodiment is shown. right and image 3 The same elements are assigned the same reference numerals, and detailed descriptions are omitted. have Figure 7 The layout of the semiconductor device of the power switch circuit PSW1 shown is the same as figure 1 The layout of the semiconductor device 100 is the same. That is, having Figure 7 The semiconductor device of the illustrated power switch circuit PSW1 has a standard cell area SCA in which a plurality of standard cells are arranged in the power domain PD, and the power switch circuit PSW1 is arranged in the standard cell area SCA.

[0073] In this embodiment, the power supply line VVDD11b of the M1 layer arranged along the Y direction at the central portion in the X direction of the power supply switch circuit PSW1 is connected to the M0 layer wiring VVDD02b extending in the X direction through the via hole sh...

no. 3 approach

[0076] Figure 8 An example of the layout of the power switch circuit of the semiconductor device in the third embodiment is shown. right and image 3 as well as Figure 7 The same elements are assigned the same reference numerals, and detailed descriptions are omitted. have Figure 8 The layout of the semiconductor device of the power switch circuit PSW1 shown is the same as figure 1 The layout of the semiconductor device 100 is the same. That is, having Figure 8 The semiconductor device of the illustrated power switch circuit PSW1 has a standard cell area SCA in which a plurality of standard cells are arranged in the power domain PD, and the power switch circuit PSW1 is arranged in the standard cell area SCA.

[0077] In this embodiment, on the power switch circuit PSW1, in addition to the power supply line VVDD11b of the M1 layer extending in the Y direction, the power supply line VSS11c of the M1 layer extending in the Y direction is also wired on the p-channel tran...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More