Chained programmable delay element

A delay element, the technology of the maximum delay, applied in the direction of electrical components, pulse technology, logic circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

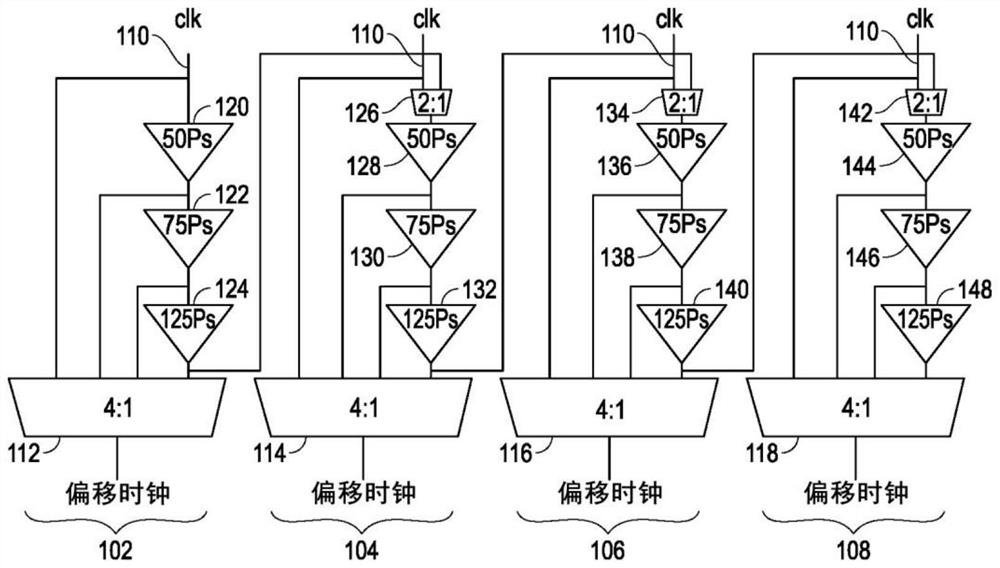

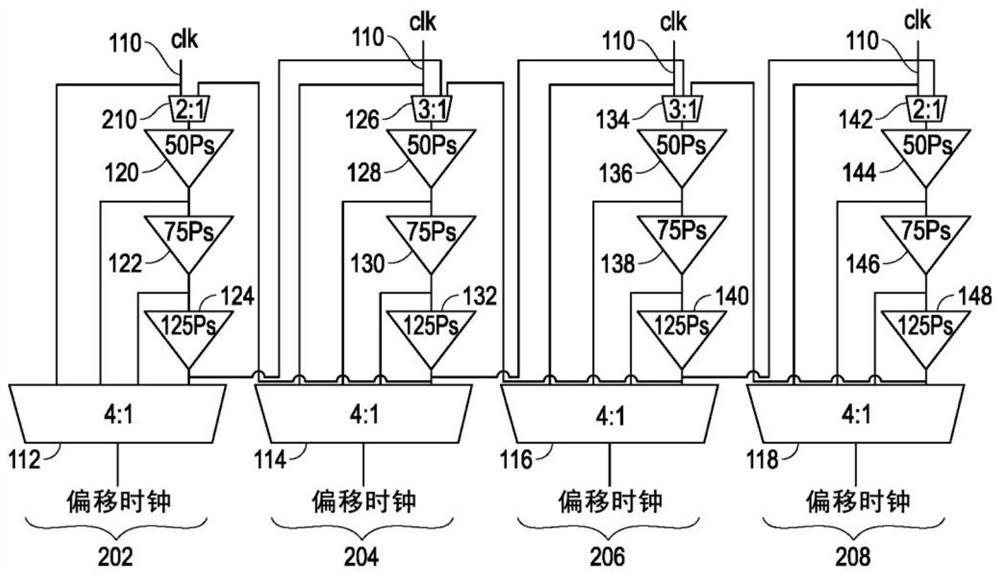

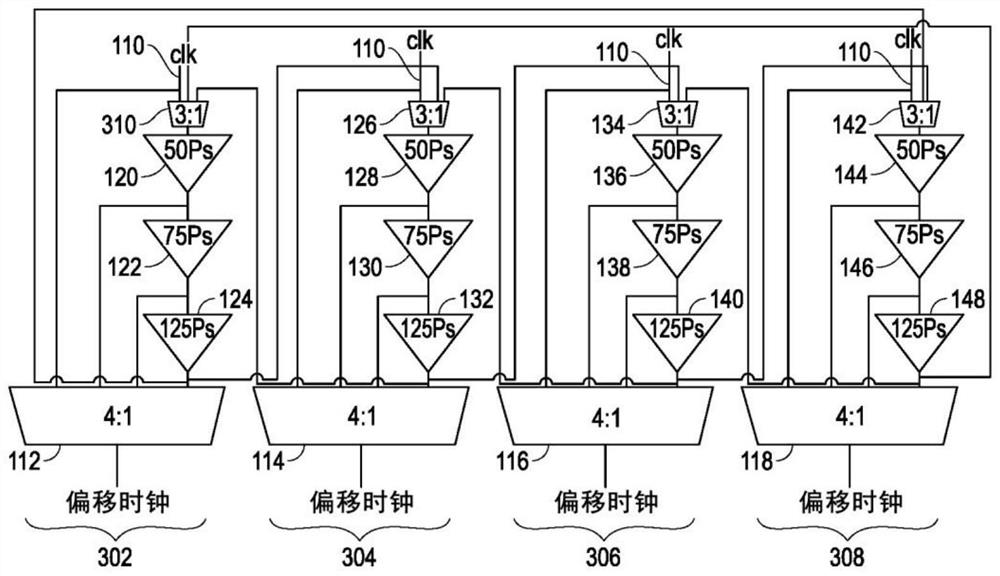

[0017] In the following description, numerous details are set forth in order to provide a more thorough explanation of the present invention. However, it will be apparent to those skilled in the art that the present invention may be practiced without or with modification of these specific details. In other instances, well-known structures and devices are shown in block diagram form, rather than in detail, in order to avoid obscuring the present invention.

[0018] The terms "multiplexer" and "mux" are used interchangeably herein for a circuit that selects from a plurality of inputs and drives an output according to the selection. In various embodiments, the multiplexer or the output driver of the multiplexer-based circuit may be integrated with the multiplexer or separate from the multiplexer. The term "clock" is used herein as applied to a clock signal, a single clock, a pair of clocks (eg, commonly referred to as clock, clk) in a symbolic representation of an electronic cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More