Rear shallow groove isolating process

A process method, shallow trench isolation technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of abnormal electrical performance of semiconductor components, reduce the electrical isolation effect of shallow trench isolation, and poor double ridges, etc. Achieve the effect of shortening production time and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

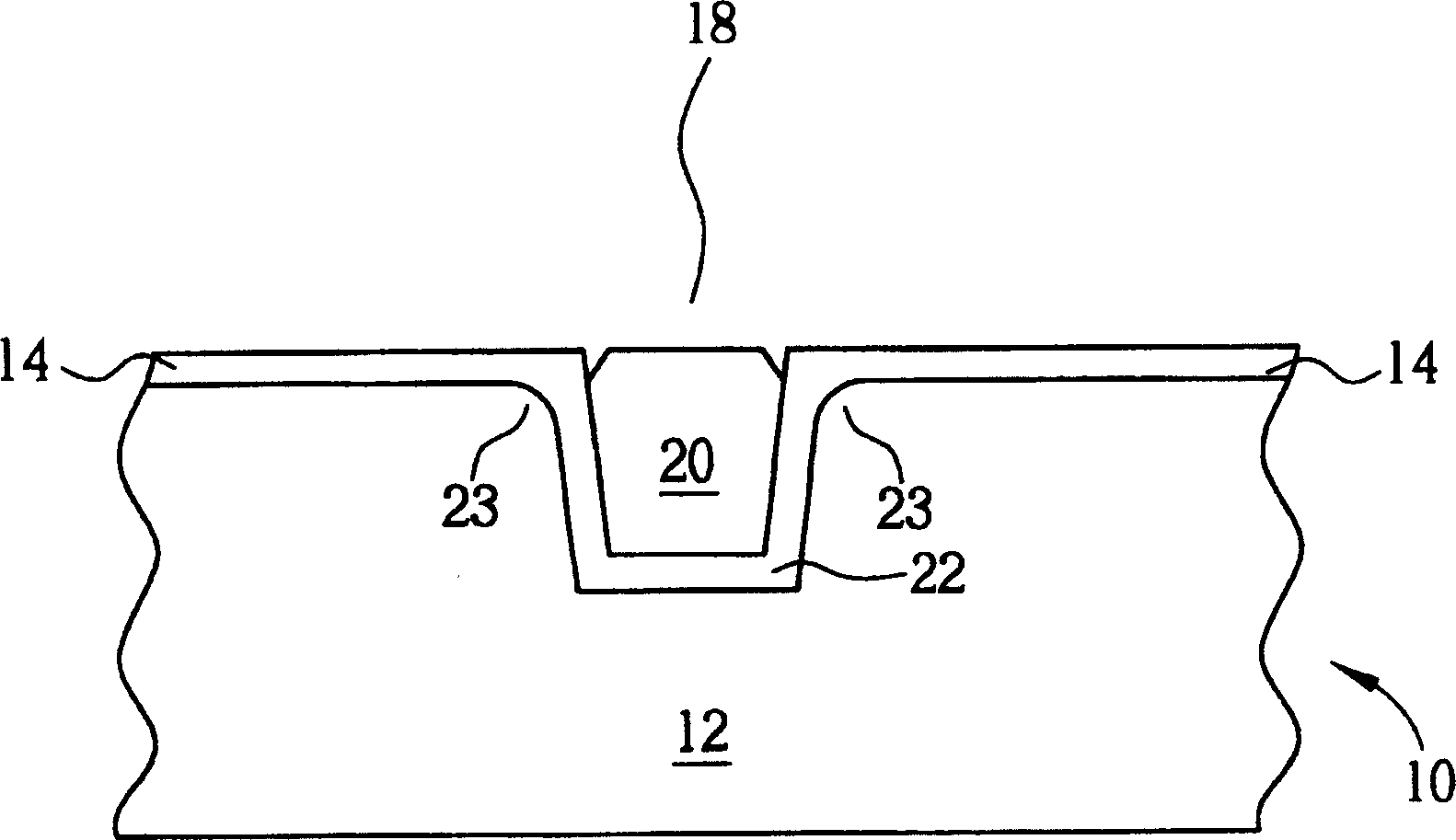

[0031] A post shallow trench isolation (post-STI) process method of the present invention is to fabricate semiconductor elements, such as gates and MOS transistors, on a substrate first, and then perform the shallow trench isolation process. The inventive method mainly has the following steps:

[0032] 1). Provide a substrate, the substrate has an upper surface;

[0033] 2). Carrying out a first ion implantation process to form a doped well region on the upper surface of the substrate;

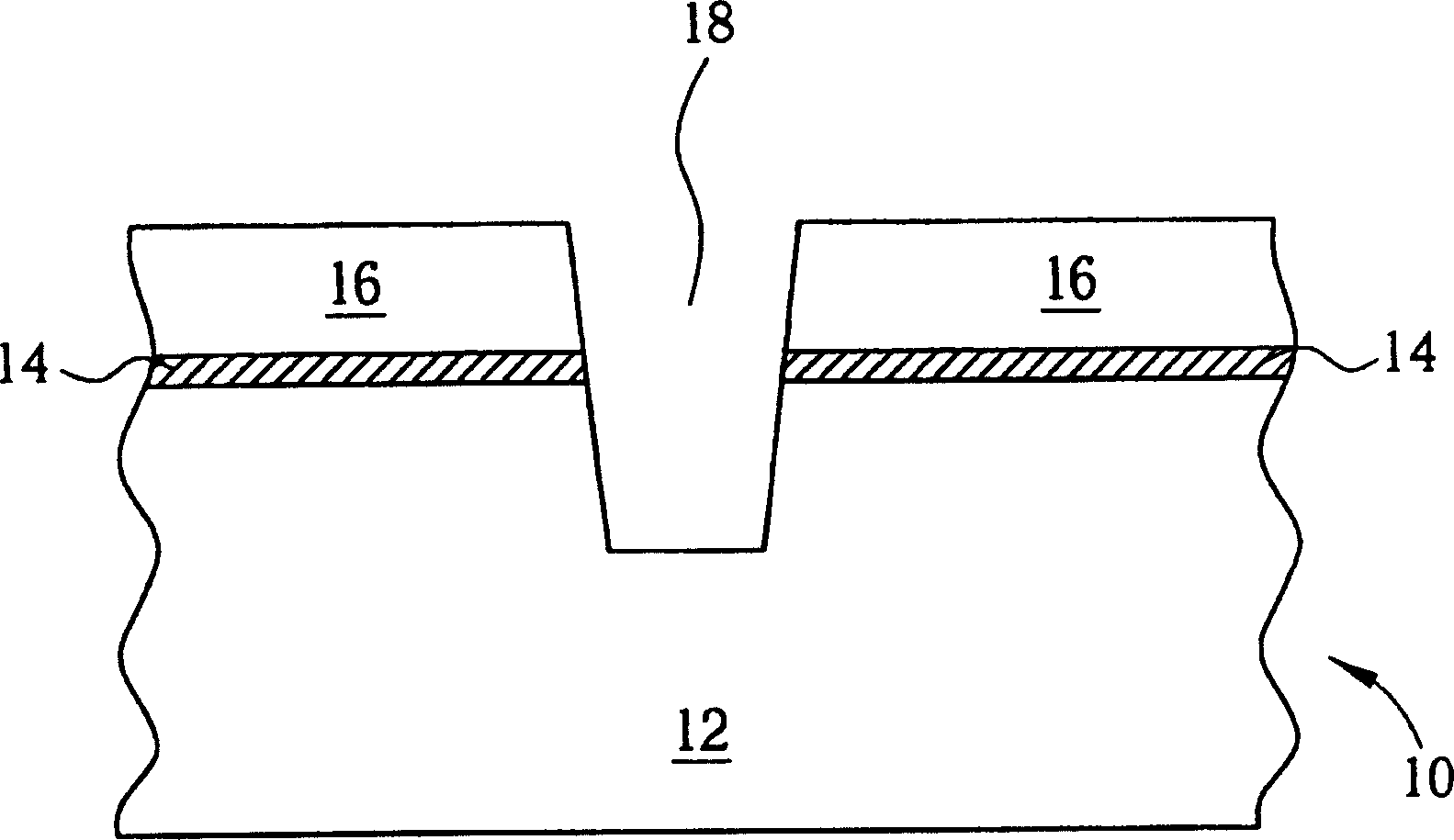

[0034] 3). Forming an oxide layer on the upper surface of the substrate;

[0035] 4). Depositing a polysilicon layer on the oxide layer;

[0036] 5). Etching the polysilicon layer to form a gate in the doped well region;

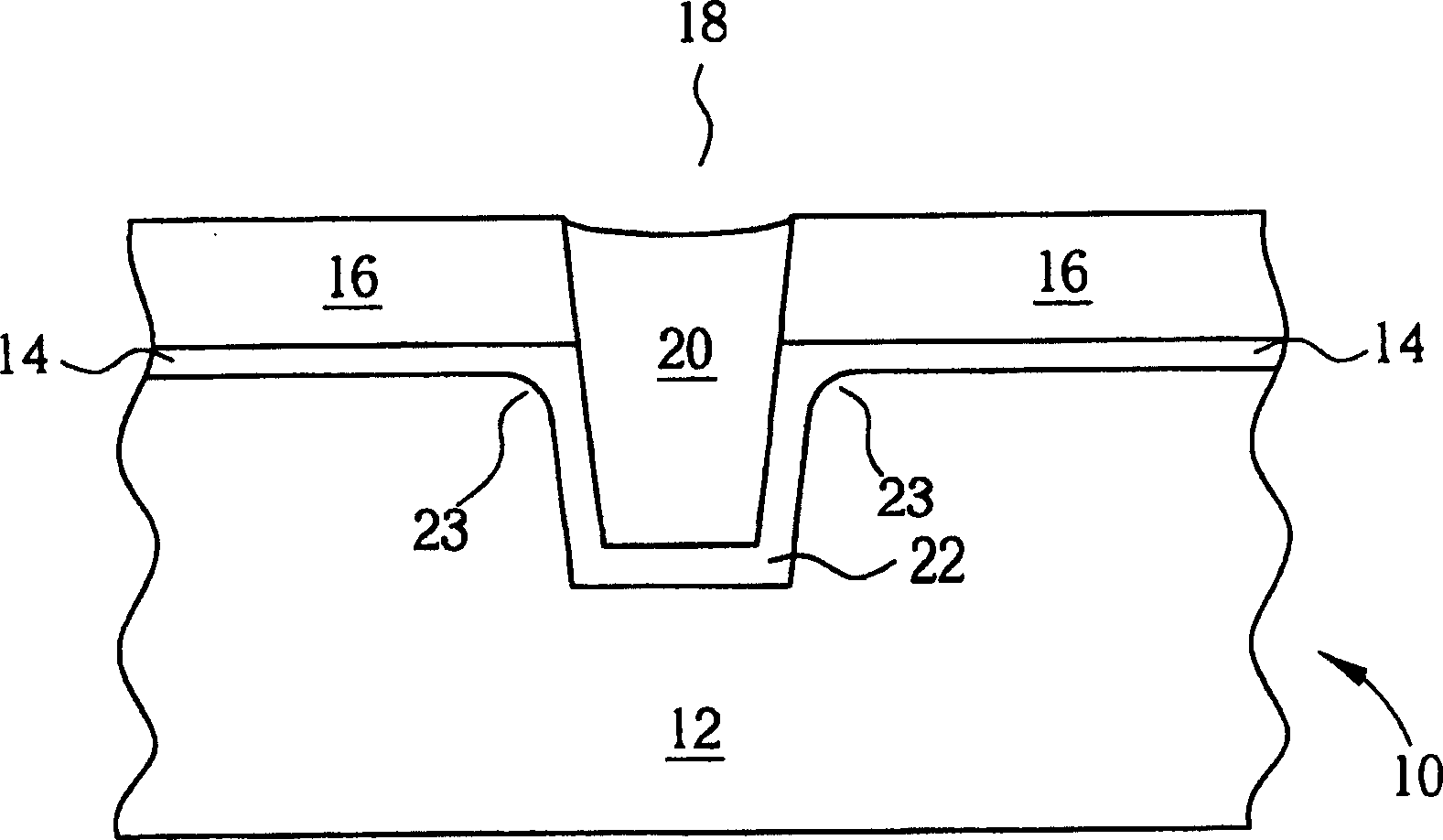

[0037] 6). Performing a second ion implantation process to form a drain region and a source region on both sides of the gate in the doped well region;

[0038] 7). Forming a first dielectric layer on the substrate to cover the doped well region, the gate and regions other ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More