Shallow-channel insulation making process

A technology of shallow trenches and liner layers, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of reduced product reliability, abnormal conductivity of semiconductor components, poor double-bumps, etc., to improve reliability. degree, enhance product competitiveness, and ensure the effect of electrical insulation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

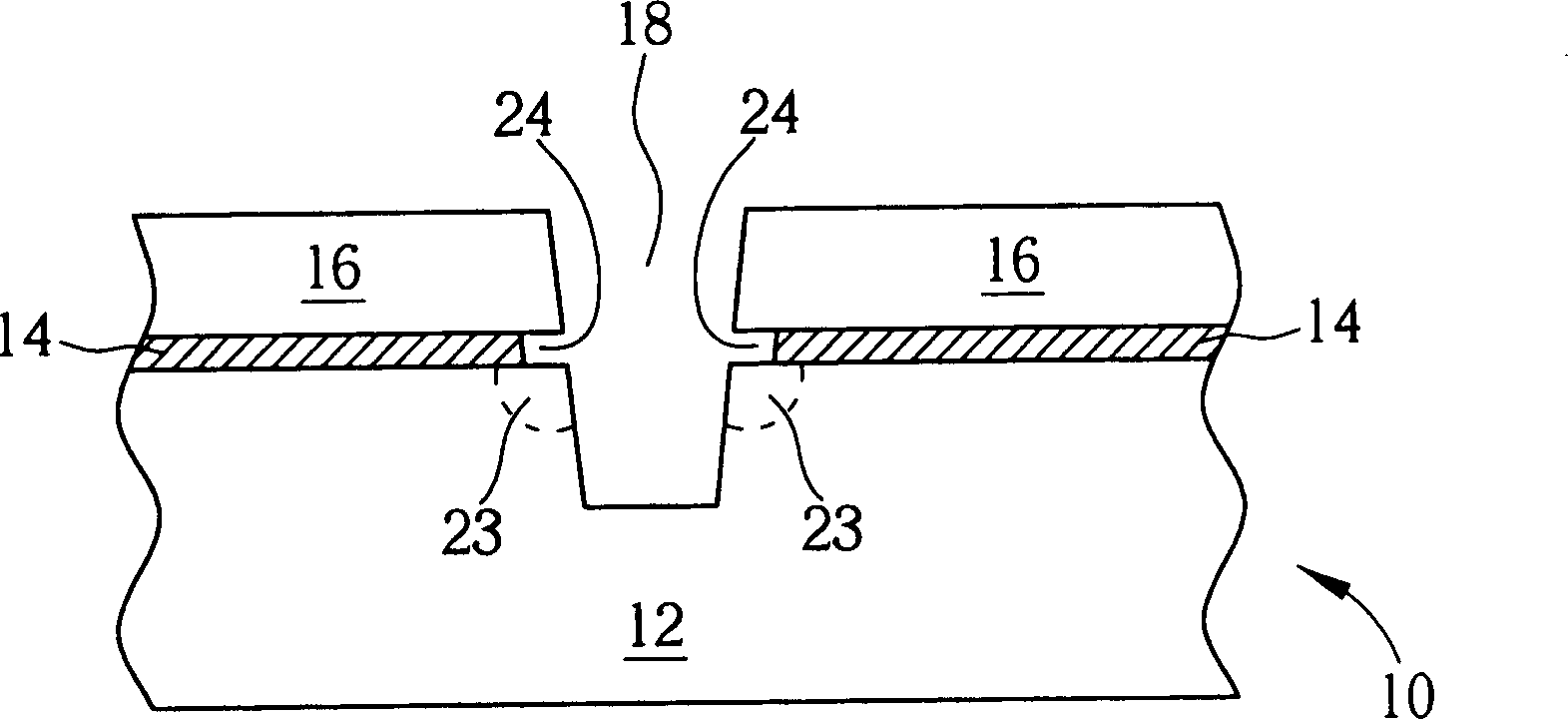

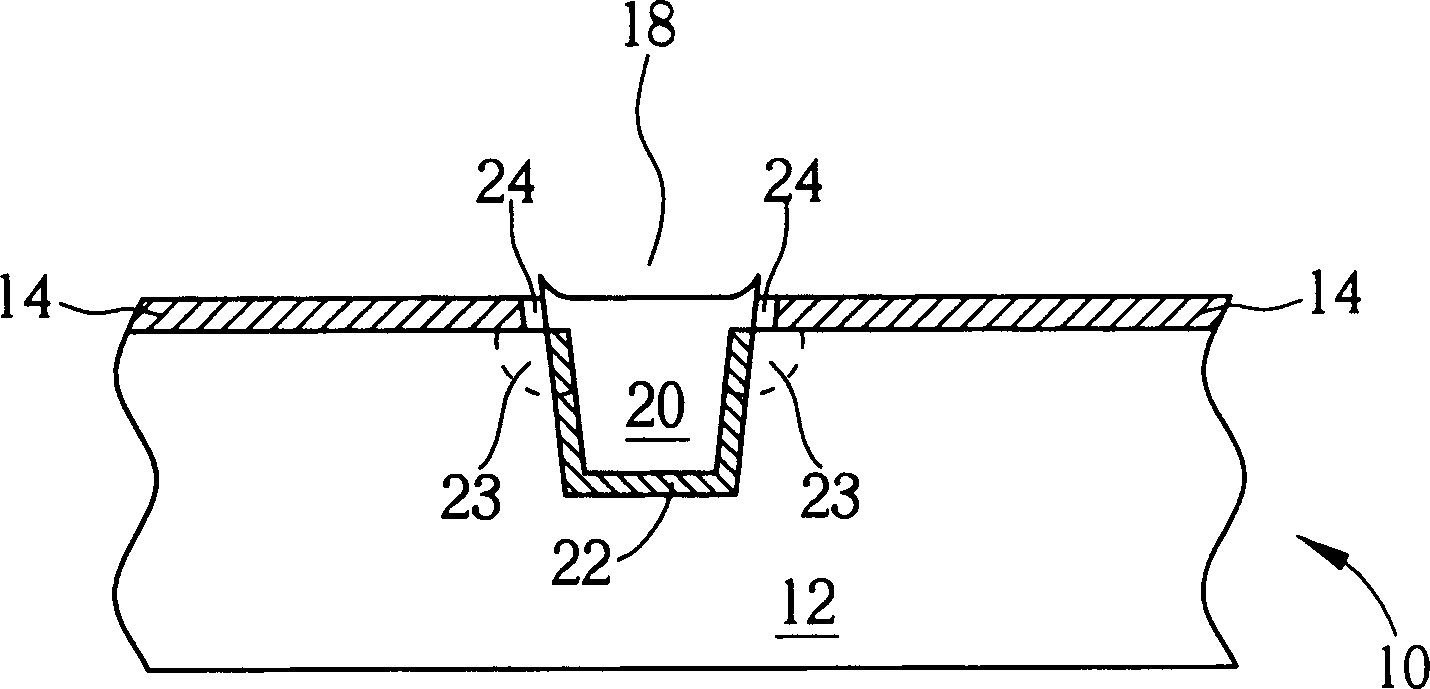

[0024] Please refer to Figure 4 to Figure 8 , Figure 4 to Figure 8 It is a schematic diagram of the shallow trench isolation process method of the present invention. Such as Figure 4 As shown, the semiconductor wafer 30 includes a silicon substrate 32 and a stacked mask layer 37 composed of a pad oxide layer 34 and a stopper layer 36 and having at least one opening 46 exposing a portion of the surface of the silicon substrate 32 . The stop layer 36 is a silicon nitride layer.

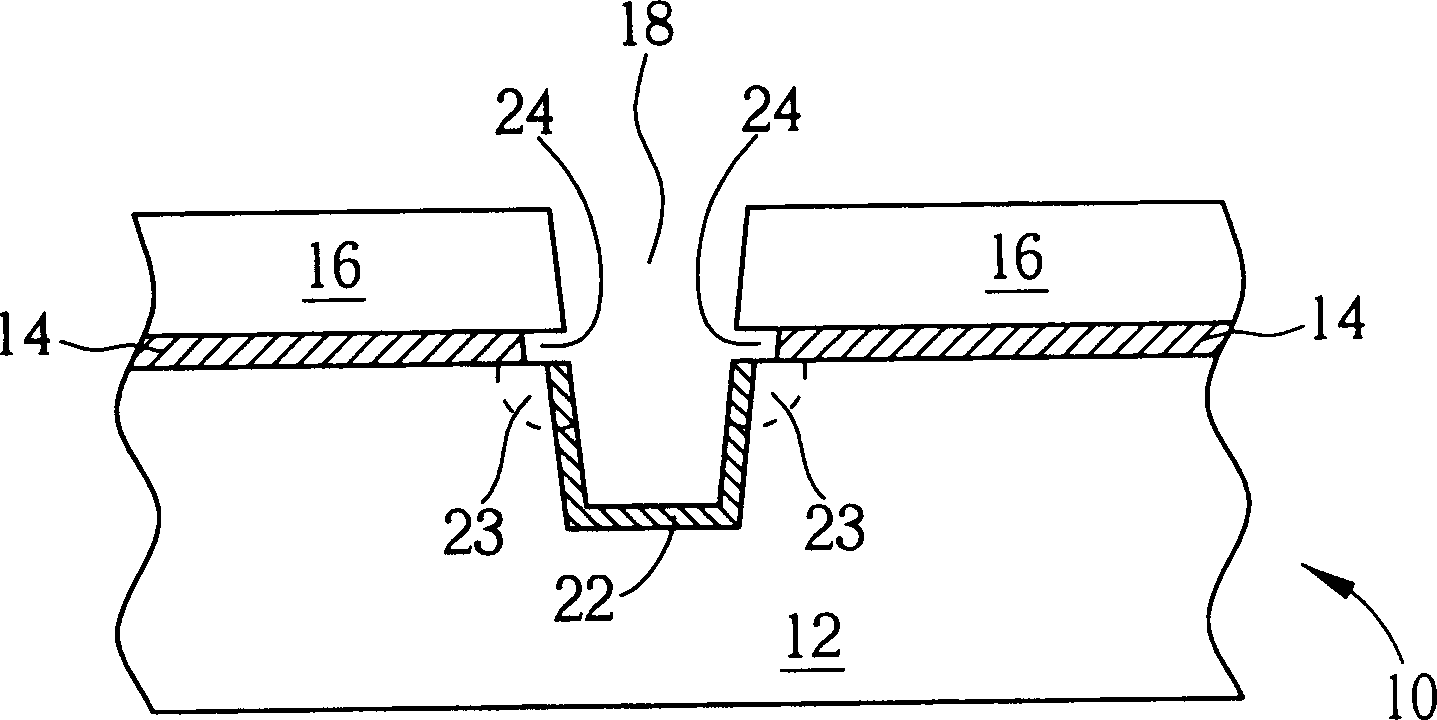

[0025] Such as Figure 5 As shown, an anisotropic dry etching process is first performed to etch the surface of the silicon substrate 32 through the opening 46 to form a shallow trench 38 on the semiconductor wafer 30 and penetrate into the silicon substrate 32 to a certain depth. Since the etch rate of the pad oxide layer 34 is greater than the etch rate of the stop layer 36, an oxide layer depression 44 will be generated at the shallow trench corner region 33 of the shallow trench region 18 at ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More