Semiconductor memory device and electronic information apparatus using same

A technology of memory devices and semiconductors, which is applied in the directions of digital memory information, static memory, read-only memory, etc., and can solve the problem of not improving the data readout rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

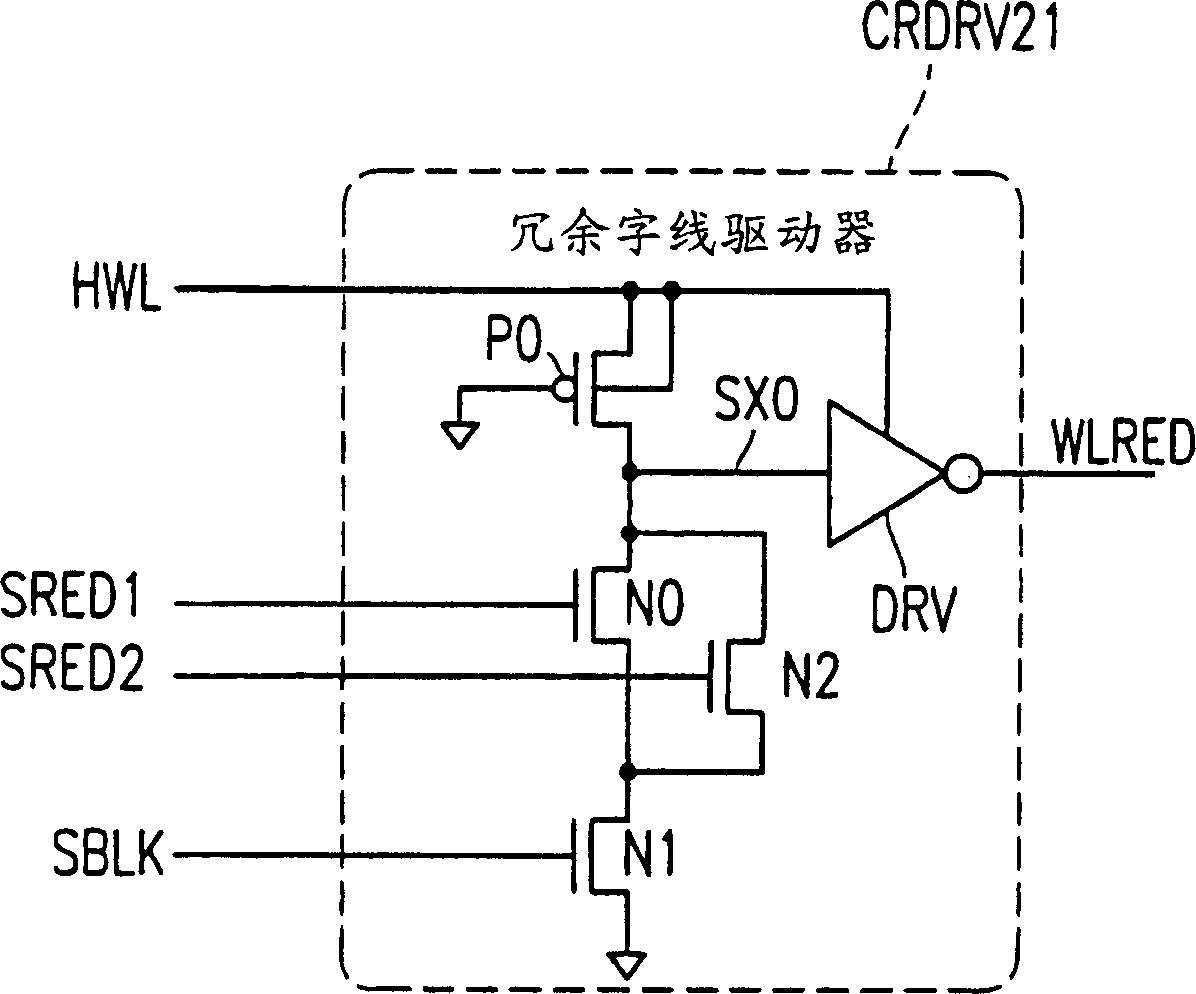

[0077] Embodiments of the present invention will be described below with reference to the accompanying drawings.

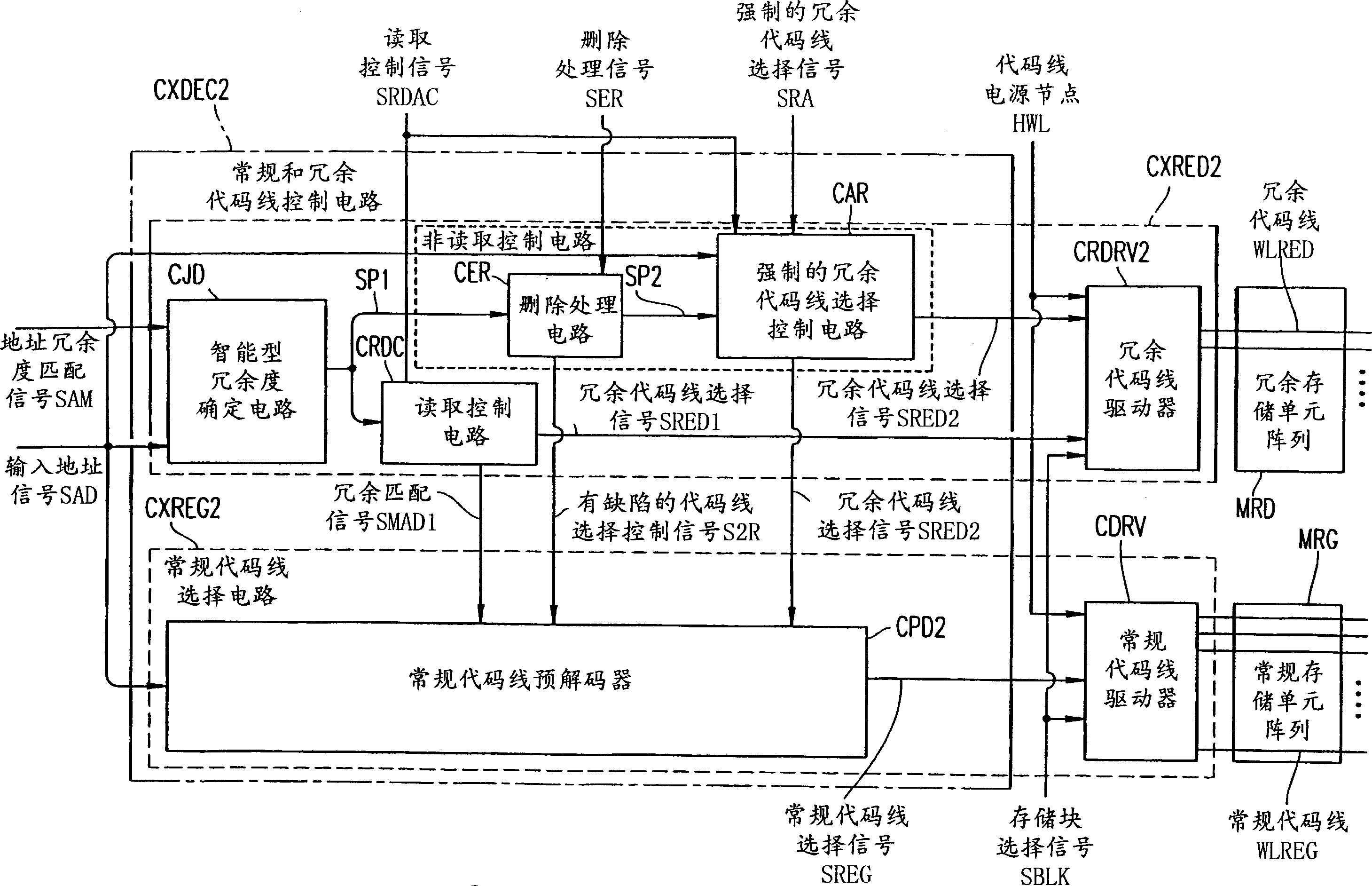

[0078] Referring to FIGS. 1 to 3, a semiconductor memory device 10 according to an example of the present invention will be described. The same units as those shown in FIGS. 4 to 6 are denoted by the same reference numerals, and a detailed description thereof will be omitted.

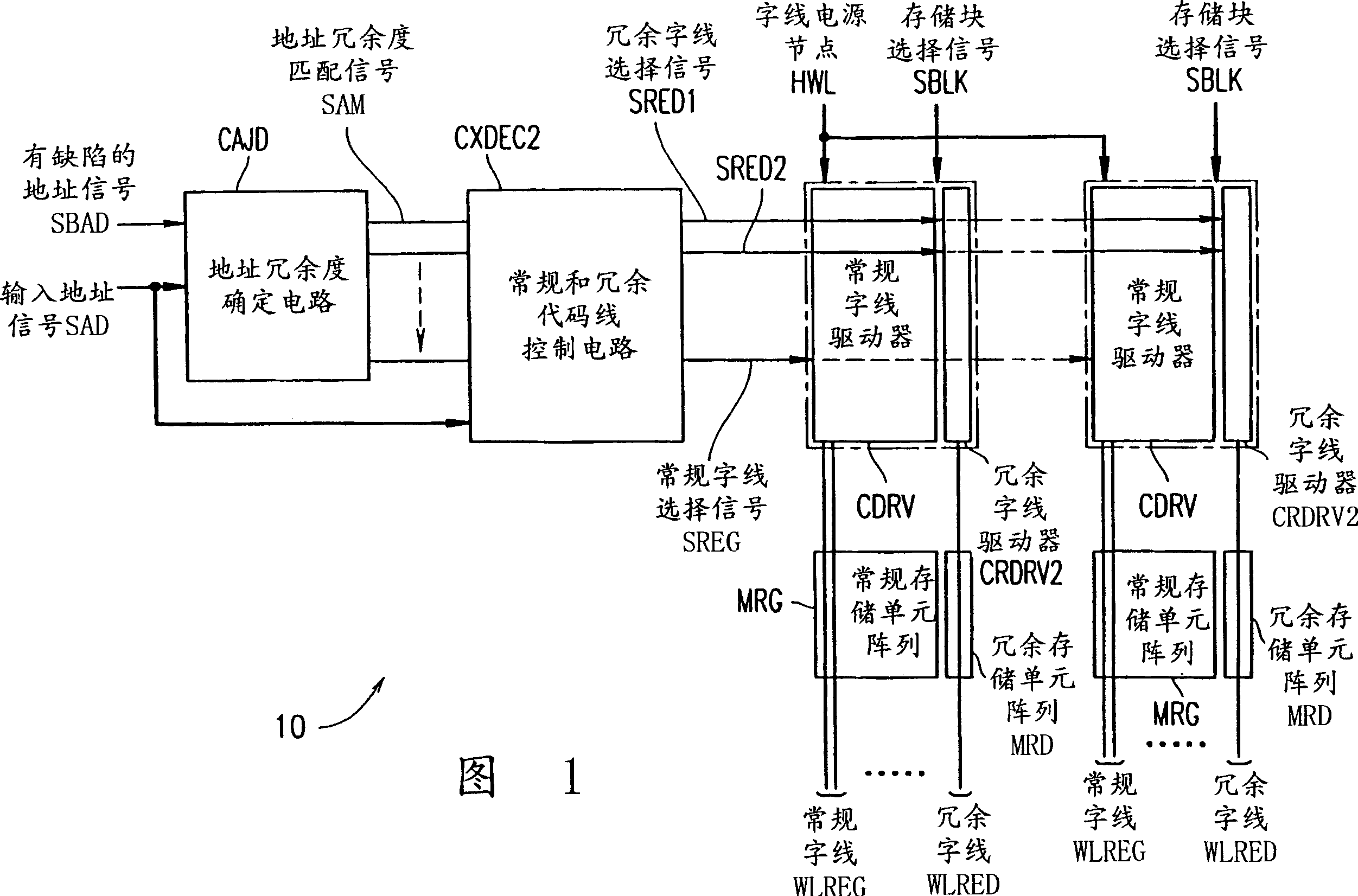

[0079] FIG. 1 is a block diagram illustrating a part of the structure of the semiconductor memory device 10. As shown in FIG.

[0080] As shown in FIG. 1, the semiconductor memory device 10 includes an address redundancy determination circuit CAJD, a conventional and redundant word line control circuit CXDEC2, a plurality of conventional memory cell arrays MRG, a plurality of redundant memory cell arrays MRD, a plurality of A normal word line driver CDRV, and a plurality of redundant word line drivers CRDRV2.

[0081] The address redundancy determination circuit CAJD determines whether th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More