Semiconductor memory

A technology of semiconductor and memory, which is applied in the field of semiconductor memory and can solve problems such as effective operation delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] Embodiments of the present invention will now be described with reference to the drawings.

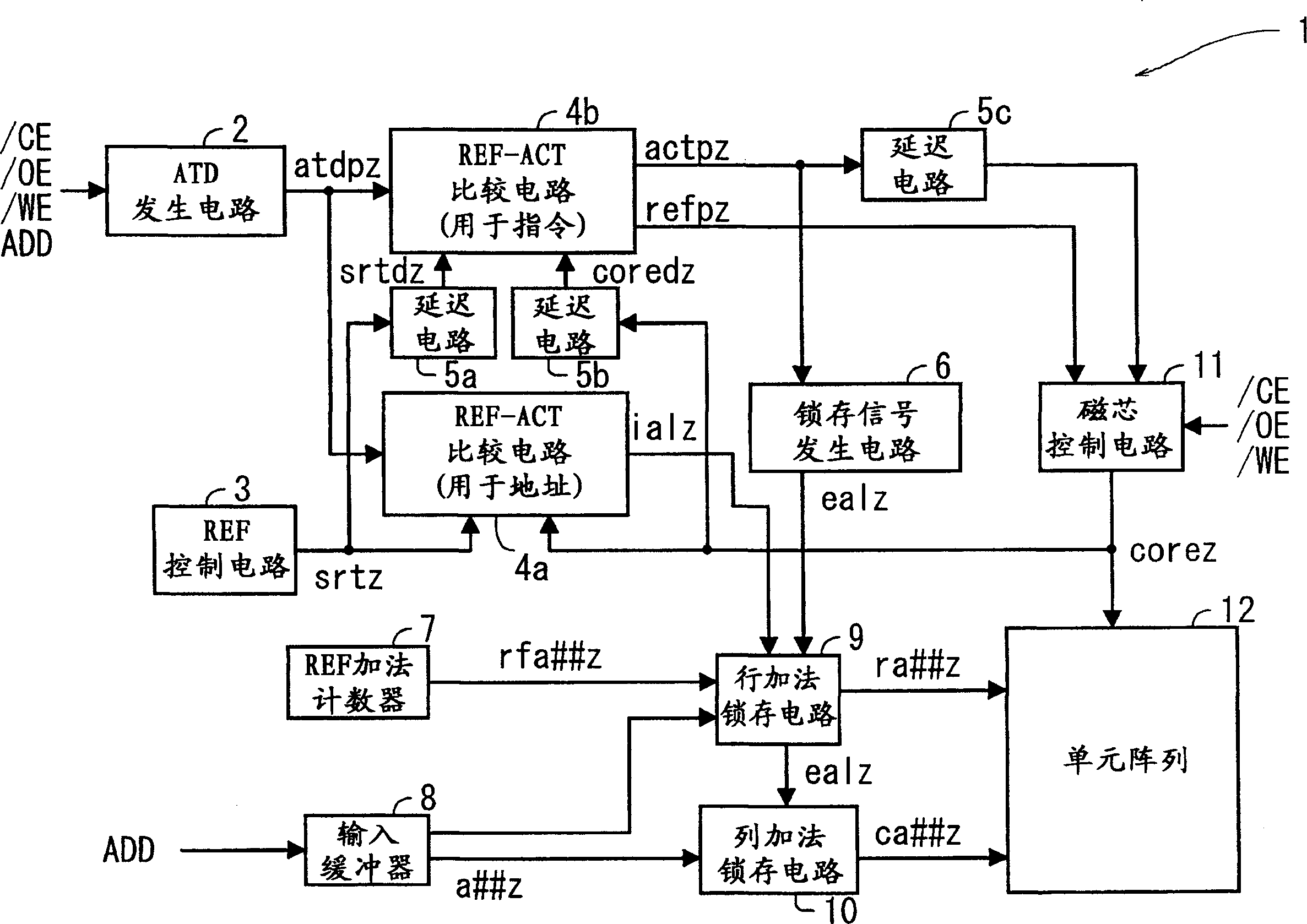

[0054] attached figure 1 Shown is a structural view of a semiconductor memory according to an embodiment of the present invention.

[0055] The semiconductor memory 1 has an ATD generation circuit 2, a REF control circuit 3, REF-ACT comparison circuits 4a and 4b, delay circuits 5a to 5c, a latch signal generation circuit 6, a REF addition counter 7, an input buffer 8, a row addition latch circuit 9, column addition latch circuit 10, core control circuit 11, and memory cell array (core circuit) 12, and has a DRAM structure with an asynchronous SRAM interface in which a refresh operation is automatically performed internally.

[0056] ATD generation circuit 2 detects changes in external signals ( / CE, / WE, / OE and ADD) and generates, for example, an active request signal atdpz representing a read / write request.

[0057] In this case, / CE, / WE, / OE, and ADD are chip enable signal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More