Semiconductor integrated circuit device

一种集成电路、半导体的技术,应用在半导体器件、电路、半导体/固态器件制造等方向,能够解决改变布线、信号延迟时间不平衡、布局设计困难等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

[0044] Referring now to the drawings, a first embodiment of the present invention will be described.

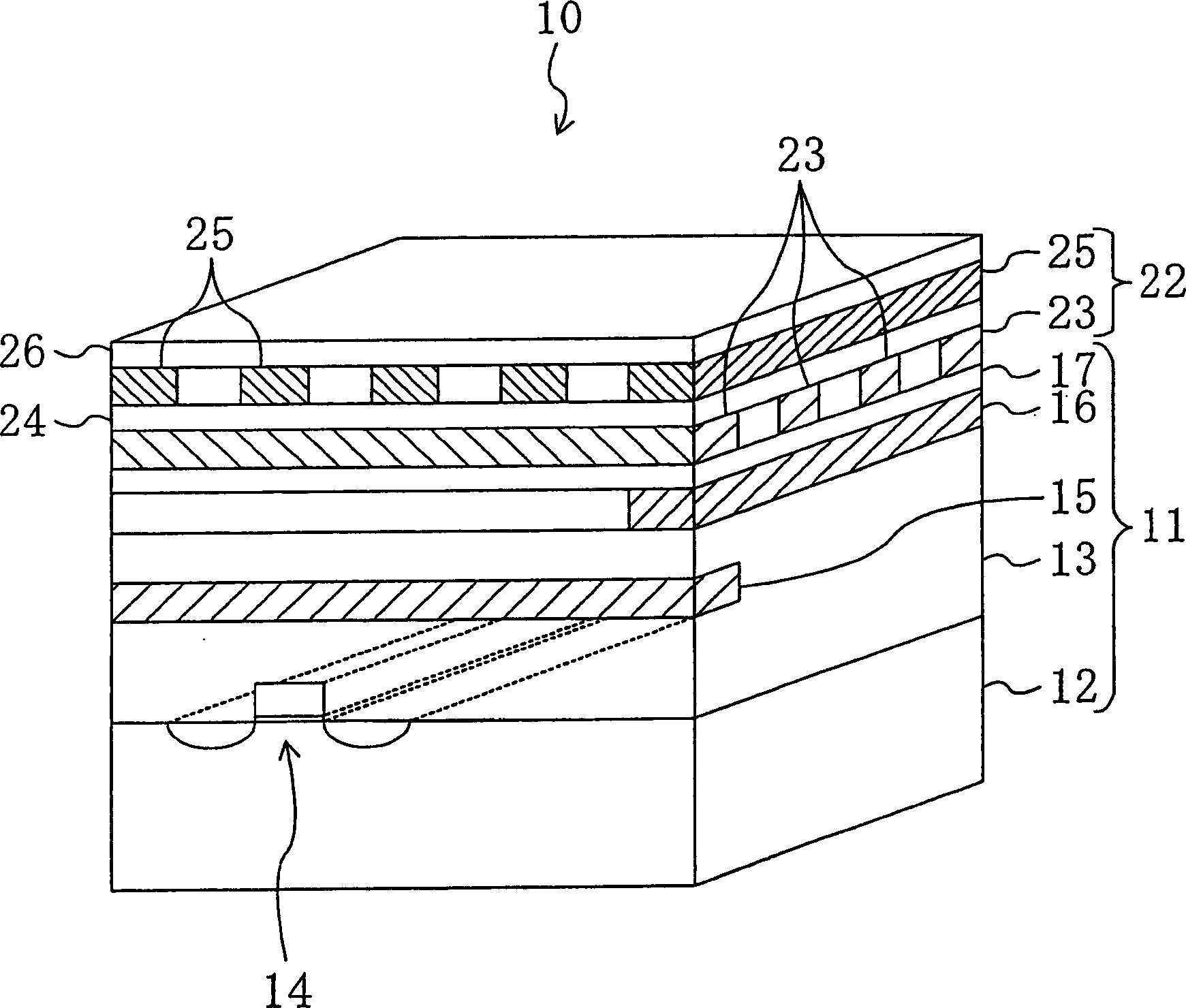

[0045] figure 1 It is a schematic diagram of the cross-sectional structure of the semiconductor integrated circuit device having the shielded wiring layer according to the first embodiment of the present invention.

[0046] as figure 1 As shown, the semiconductor integrated circuit device 10 according to the first embodiment is composed of an LSI function part 11 and a shield wiring layer 22 formed thereon.

[0047] The LSI function unit 11 is composed of a semiconductor substrate 12 and a first insulating film 13 , and a plurality of circuit elements including, for example, MOS transistors 14 are formed on the semiconductor substrate 12 . On the first insulating film 13, the first LSI wiring 15 and the second LSI wiring 16 are formed; on the first insulating film 13, the second insulating film 17 is formed.

[0048] The shield wiring layer 22 is composed of a lower shield...

no. 2 Embodiment approach

[0065] Next, a second embodiment of the present invention will be described with reference to the drawings.

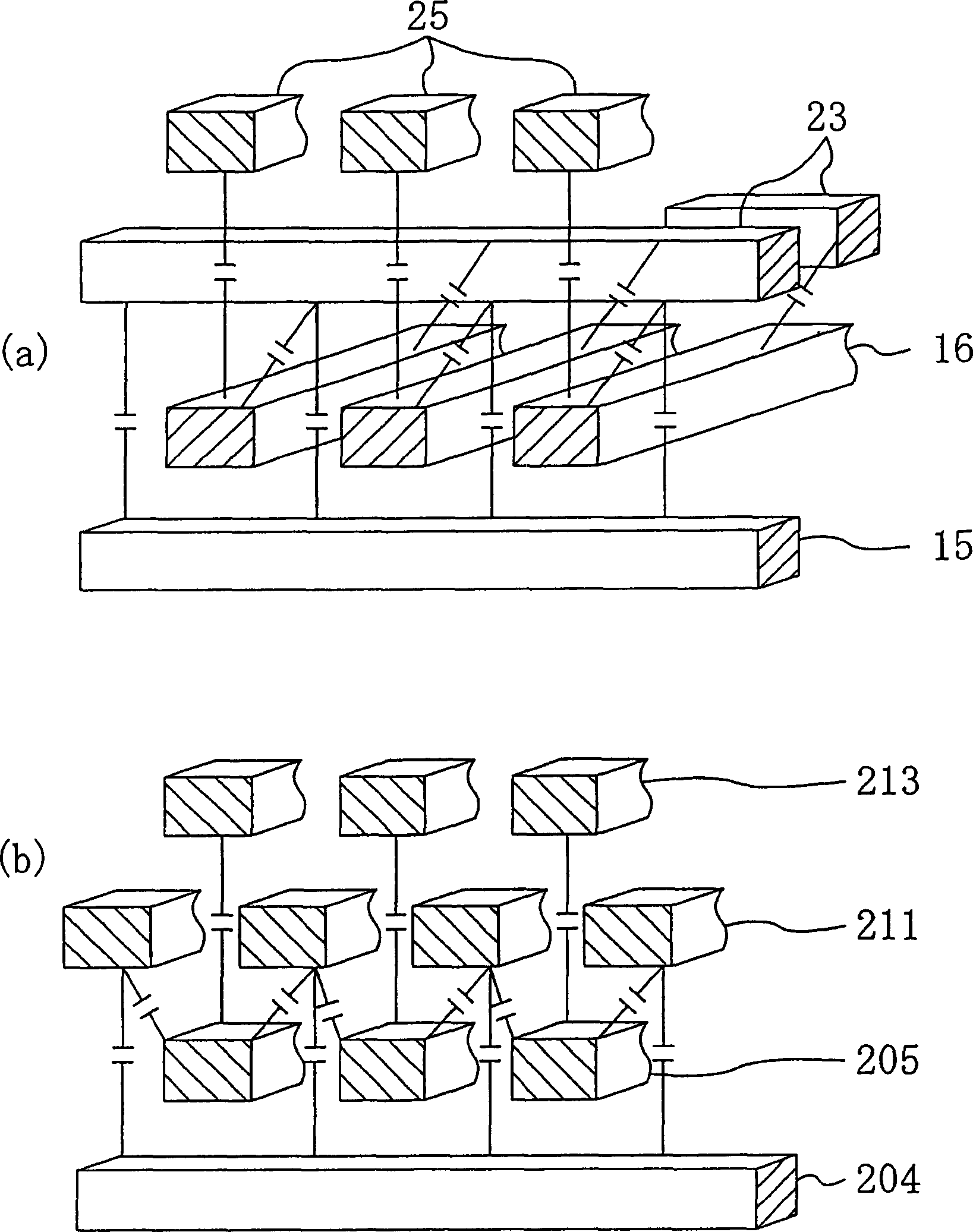

[0066] Figure 5 (a) and Figure 5 (b) is the semiconductor integrated circuit according to the second embodiment of the present invention, Figure 5 (a) shows the planar structure of the shielded wiring, Figure 5 (b) shows a partially enlarged planar structure of shield wiring and LSI wiring. exist Figure 5 (a) and Figure 5 In (b), for and figure 1 Structural components that are the same as those shown are assigned the same symbols, and description thereof will be omitted.

[0067] Such as Figure 5 As shown in (a), the shield wiring 52 according to the second embodiment is repeatedly arranged and extended parallel to one diagonal of the semiconductor integrated circuit device (chip) 10 having a planar square shape. Here, the shield wiring 52 may be one layer or two layers. In addition, when the upper shield wiring and the lower shield wiring are composed...

no. 3 Embodiment approach

[0077] Next, referring to the drawings, a third embodiment of the present invention will be described.

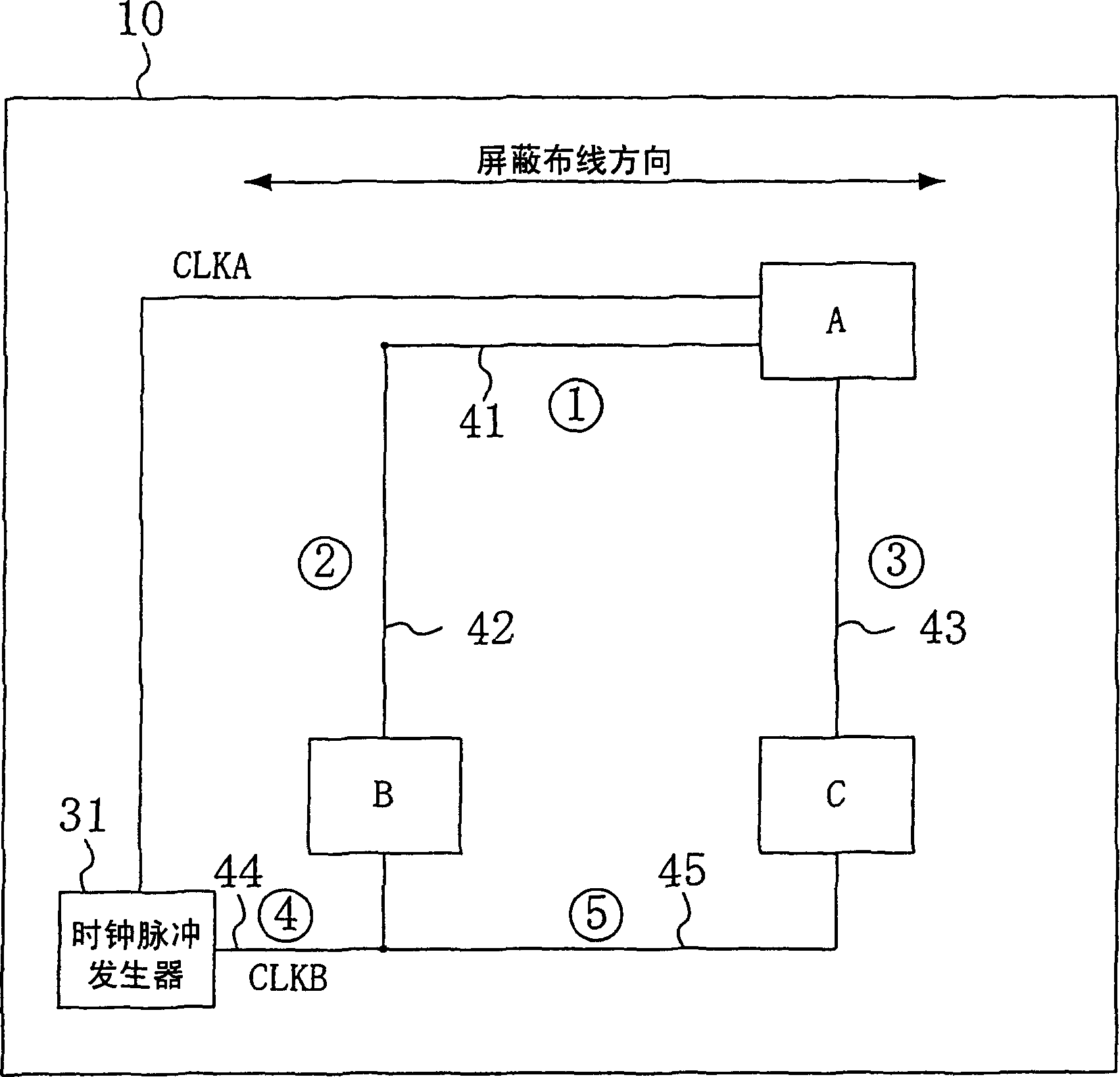

[0078] Figure 8 It is a schematic diagram showing an example of the switching circuit configuration of the shield wiring in the semiconductor integrated circuit device according to the third embodiment of the present invention.

[0079] Such as Figure 8 As shown, for example, one end or both ends of each of the eight shielded wirings 60a, 60b, . . .

[0080] The switching circuit 61 has an 8-bit register 65 connected to a setting signal line 66 which can be set externally, and a first switching circuit 64A, a second switching circuit 64A, and a second switching circuit 64A are respectively provided between the register 65 and the shielded wiring lines 60a to 60h. The switch circuit 64B, the third switch circuit 64C, and the fourth switch circuit 64D.

[0081] Although not shown in the figure, the register 65 has an 8-bit structure of bit 0 (b0), bit 1 (b1), . . . , bit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More