Grid electrode control circuit of up-draw transistor for high-voltage input

A gate control, transistor technology, applied in logic circuits, electrical components, electronic switches, etc., can solve the problems of TDDB reliability, system failure, input signals that cannot be turned off by PMOS transistors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

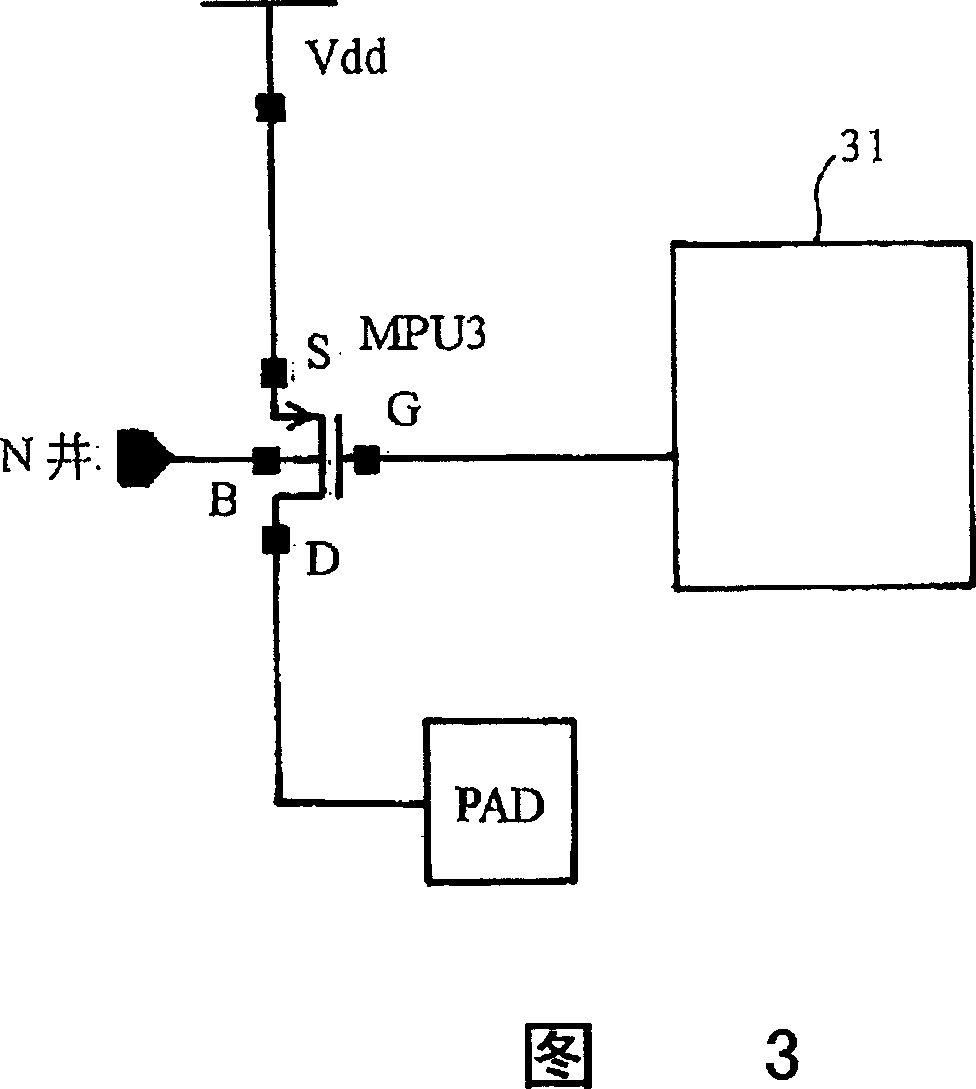

[0040] Preferred embodiments according to the present invention will now be described hereinafter with reference to the accompanying drawings.

[0041] 3 shows a schematic circuit diagram including a gate control circuit for a pull-up transistor according to the present invention. In this circuit, the gate terminal G of the pull-up transistor MPU 3 is connected to the gate control circuit 31, and the transistor MPU 3 The source terminal S of the transistor MPU 3 is connected to the power supply potential Vdd, the drain terminal D of the transistor MPU 3 is connected to the pad PAD node, and the base B of the transistor MPU 3 is connected to an N-well. The operation of the circuit in FIG. 3 is that when a high voltage signal is applied, the gate control circuit 31 is used to control the gate bias voltage of the pull-up transistor MPU 3, that is, the gate control circuit 31 controls the pull-up transistor MPU 3. The gate voltage of the transistor MPU 3 is pulled, and the well bi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com