System and method for dynamically selecting storage instruction performance scheme

A technology for storing instructions and processors, applied in the field of setting hardware-based performance solutions, which can solve problems such as harmfulness and multi-threading

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The following is intended to provide a detailed description of examples of the present invention and should not be considered as limiting the invention itself. Rather, any number of variations will fall within the scope of the invention as defined in the claims following the description.

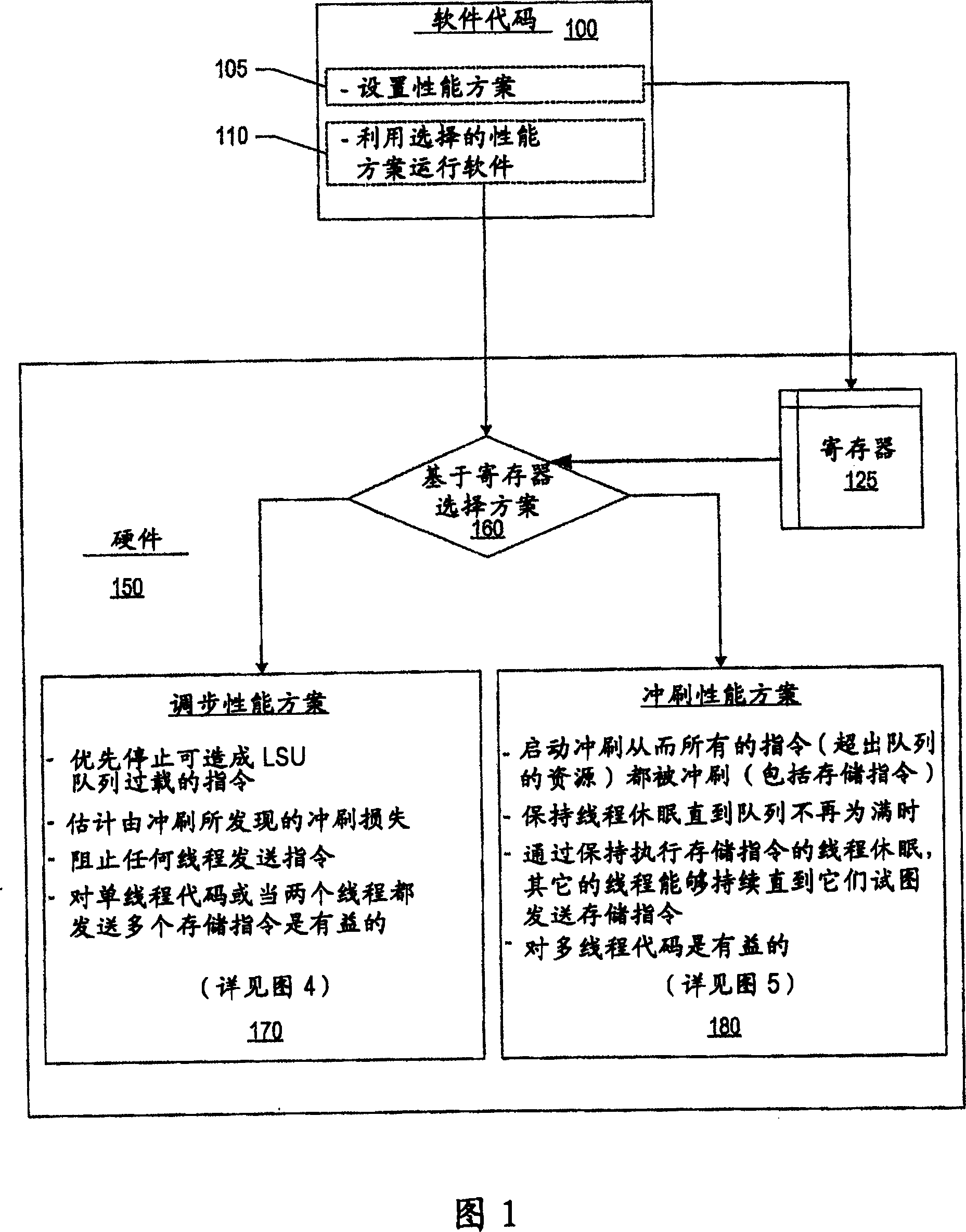

[0019] Figure 1 is a high-level diagram illustrating the interaction between software code and hardware in a select performance scheme. Software code 100 includes a number of instructions. Instructions 105 set the performance scheme used by hardware 150 . When the instruction 105 is executed, data is recorded in one or more bits of the hardware register 125 indicating the performance scheme used by the hardware 150 . The software instructions are then executed 110 using the selected performance scheme.

[0020] Hardware 150 selects a performance scheme based on performance scheme settings stored in hardware registers 125 (160). One setting results in instructions being executed us...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More