Patents

Literature

35 results about "Threaded code" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, the term threaded code refers to a programming technique where the code has a form that essentially consists entirely of calls to subroutines. It is often, but not only, found in compiler implementations that generate code in that form and/or are implemented in that form themselves. The code may be processed by an interpreter, or may simply be a sequence of machine code call instructions.

Technique for dynamically restricting thread concurrency without rewriting thread code

ActiveUS7373640B1Reduce decreaseEasy to scaleSoftware engineeringDigital computer detailsMulti processorParallel computing

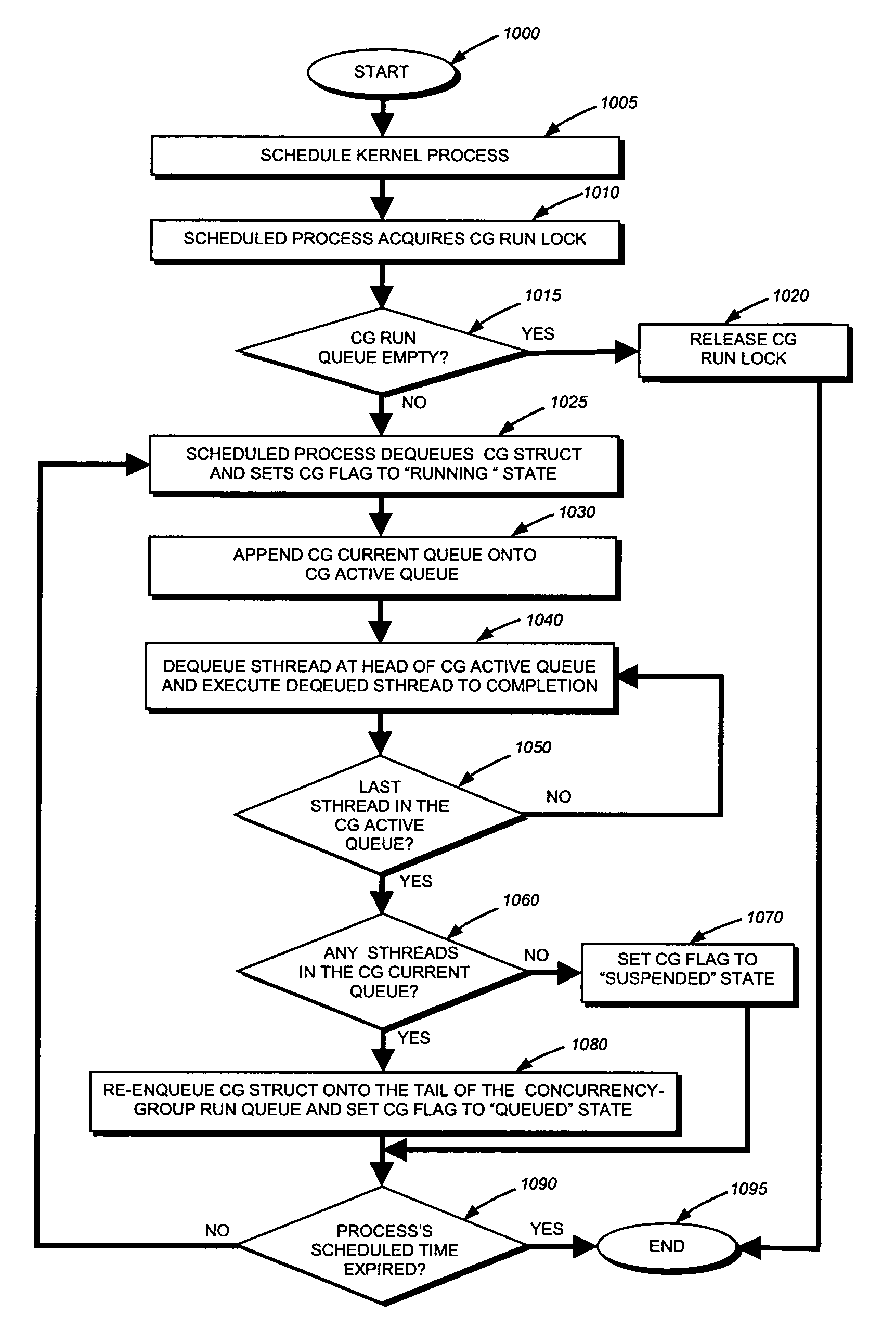

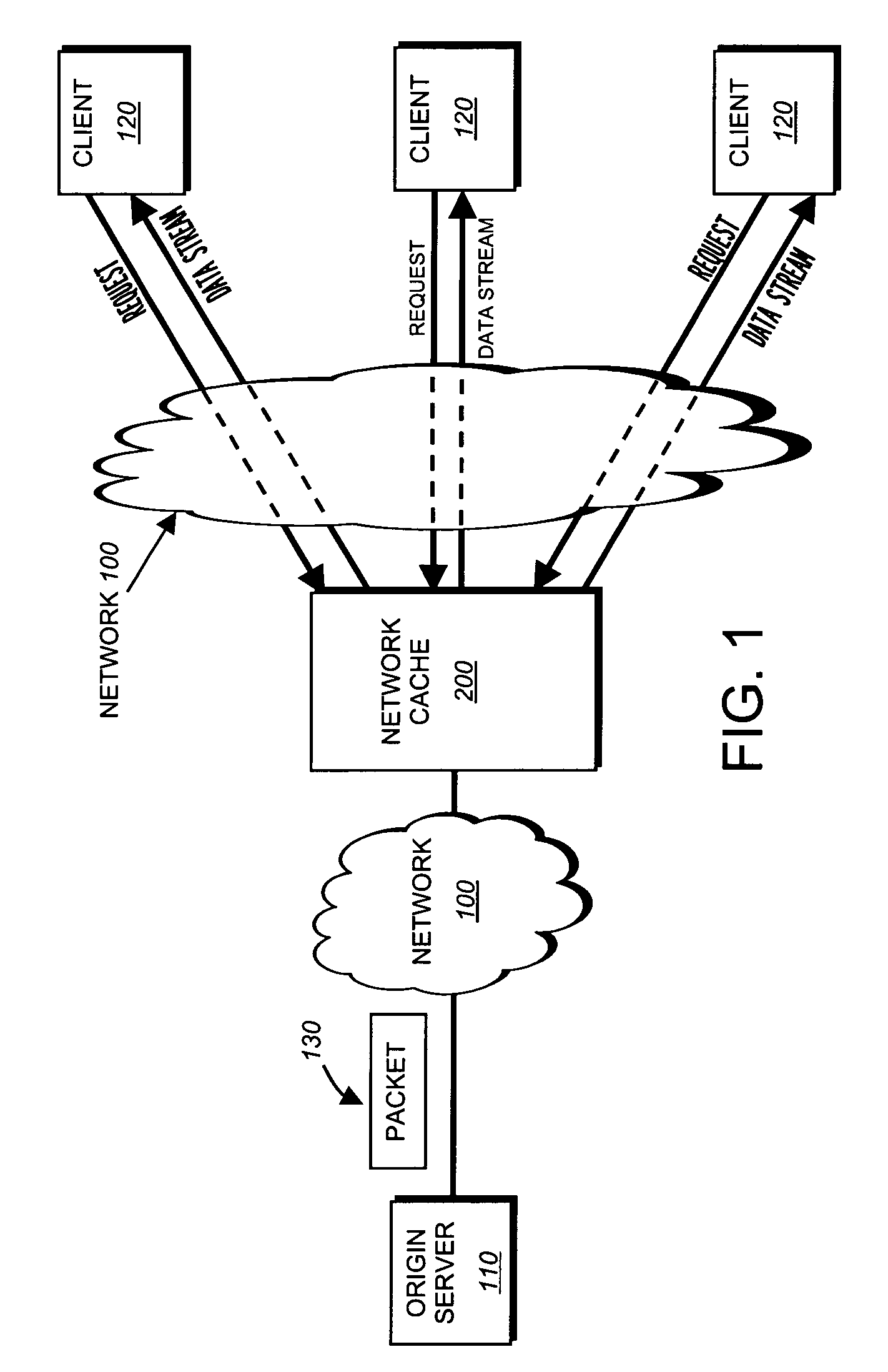

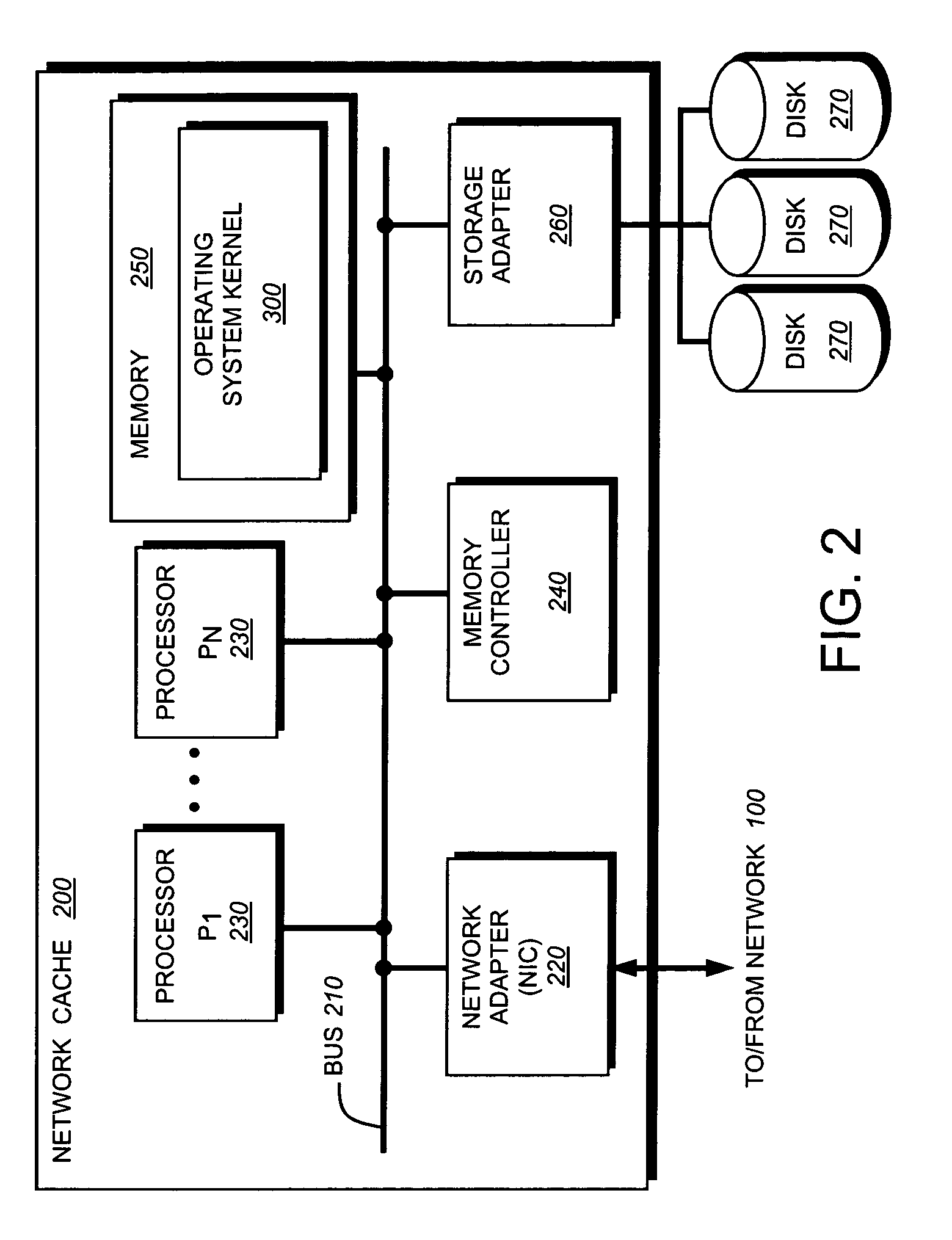

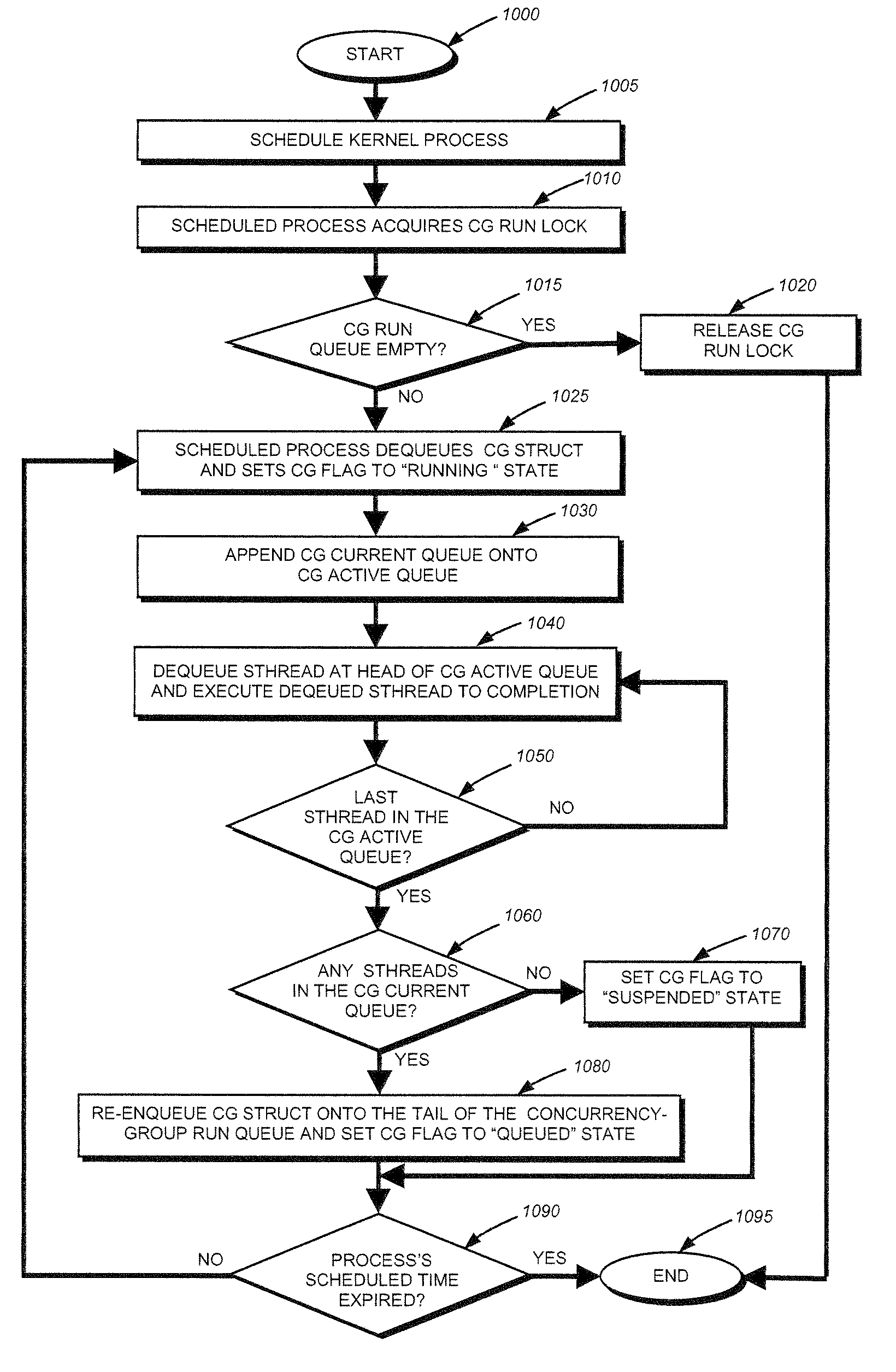

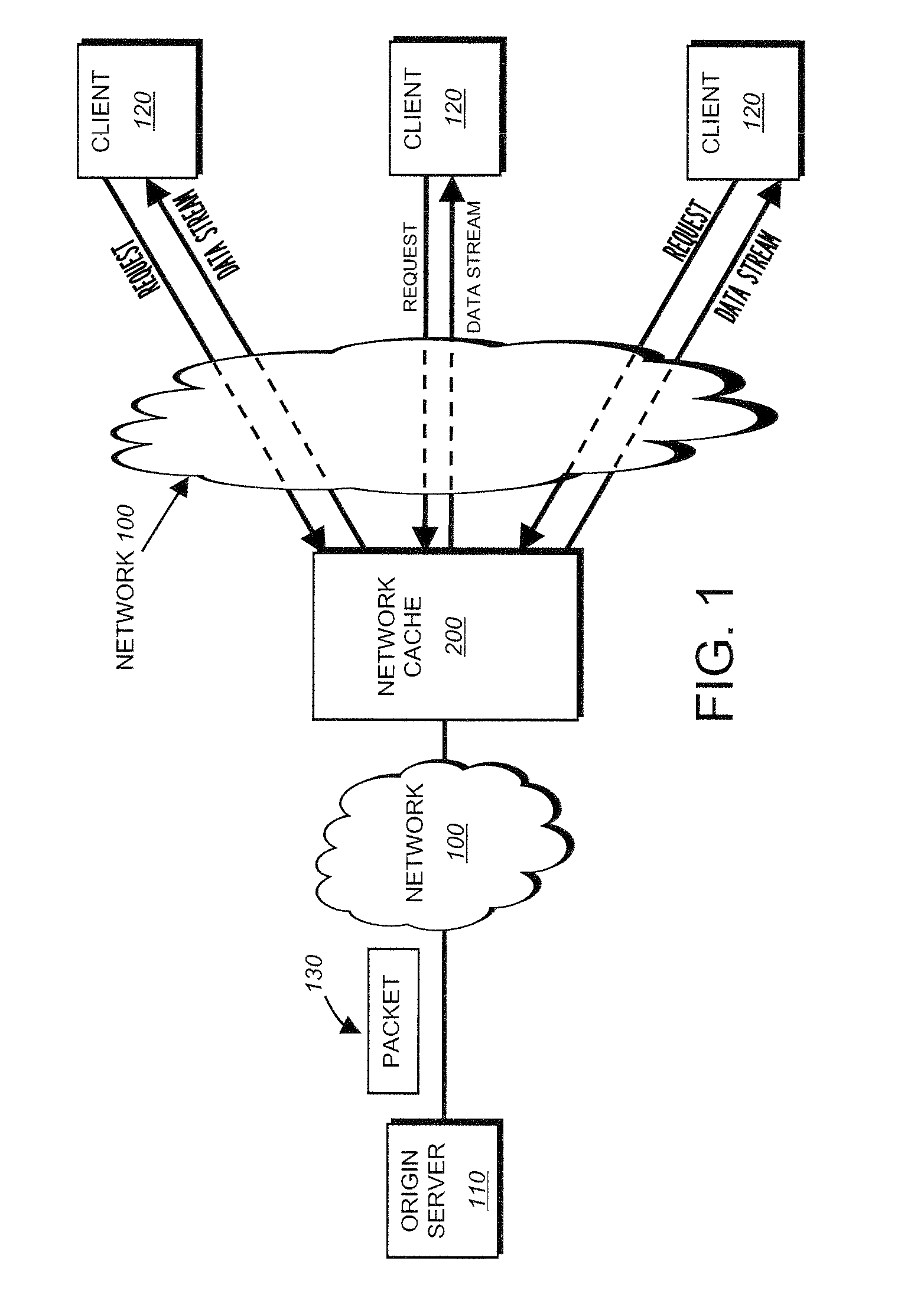

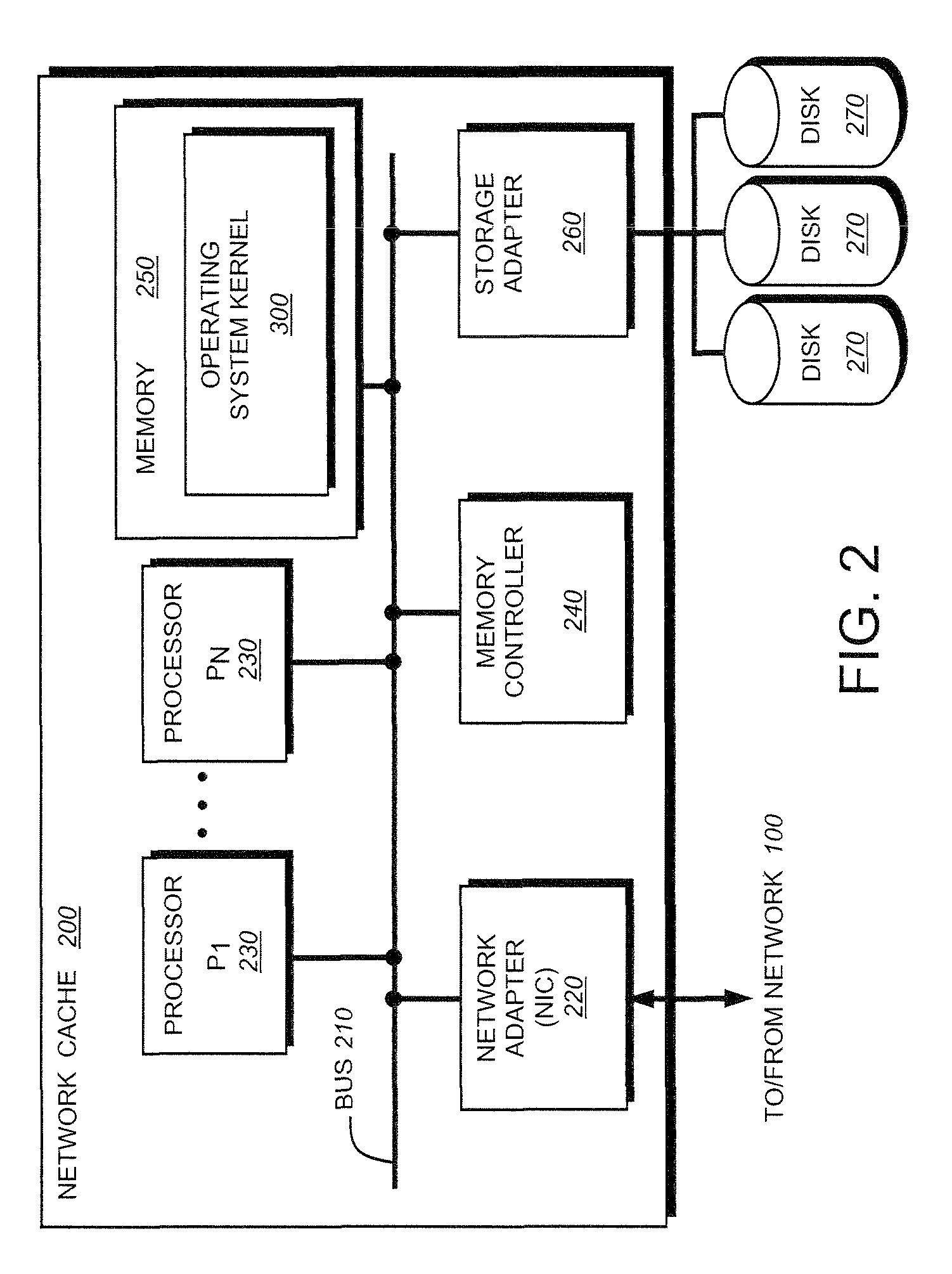

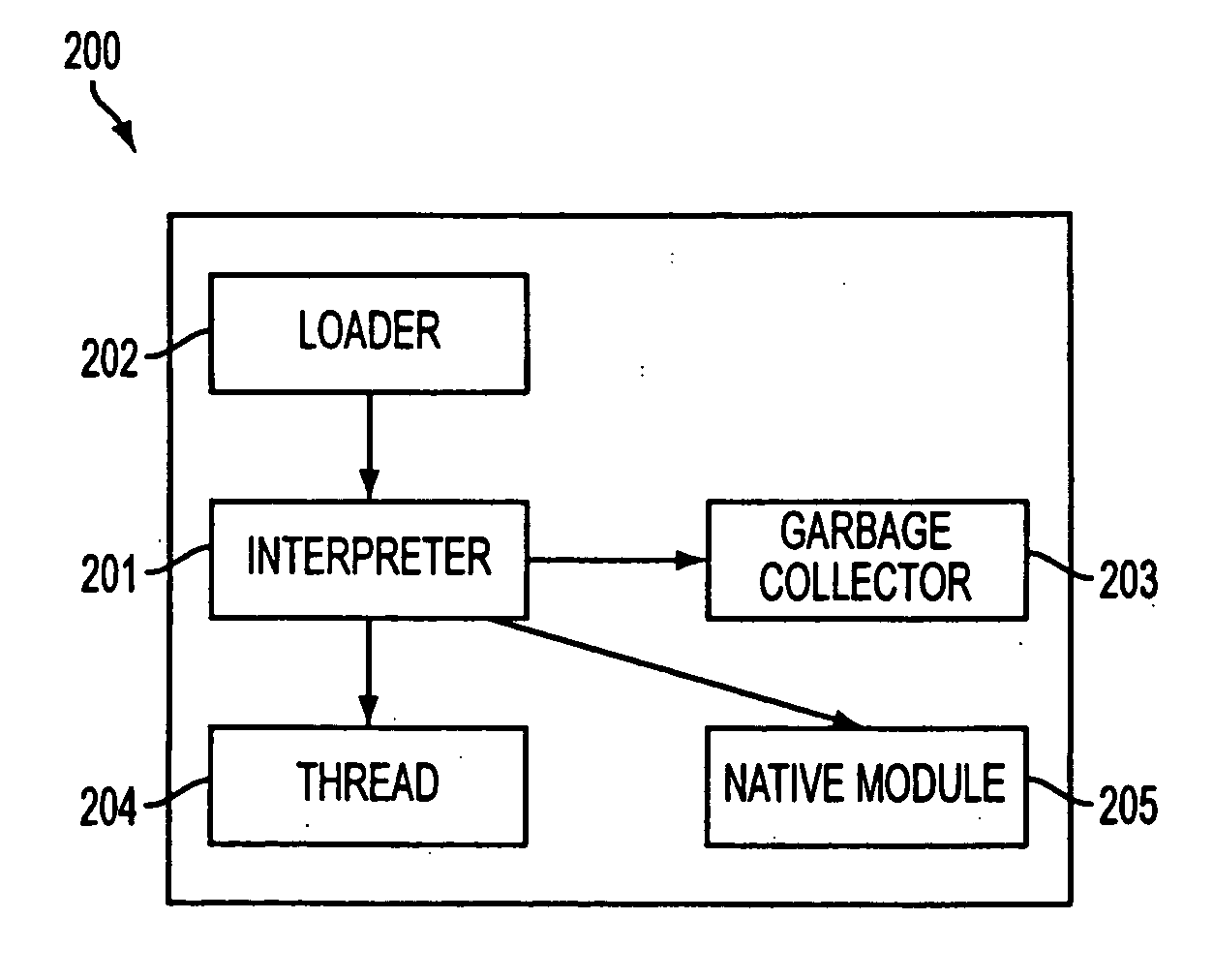

The present invention provides a technique for converting a multi-threaded application configured to execute on a uniprocessor (UP) system to one that executes on a multiprocessor (MP) system. Unlike previous approaches, a novel scheduling technique is employed so that different UP-coded user-level threads (“sthreads”) can execute concurrently in the MP system without having to rewrite their original code. To that end, the UP-coded sthreads are organized into different concurrency groups, each of which defines a set of one or more sthreads not permitted to execute concurrently. By grouping the UP-coded sthreads in this manner, different concurrency groups can be scheduled to execute their UP-coded sthreads at substantially the same time without incorporating traditional synchronization mechanisms into the sthreads' original UP code.

Owner:NETWORK APPLIANCE INC

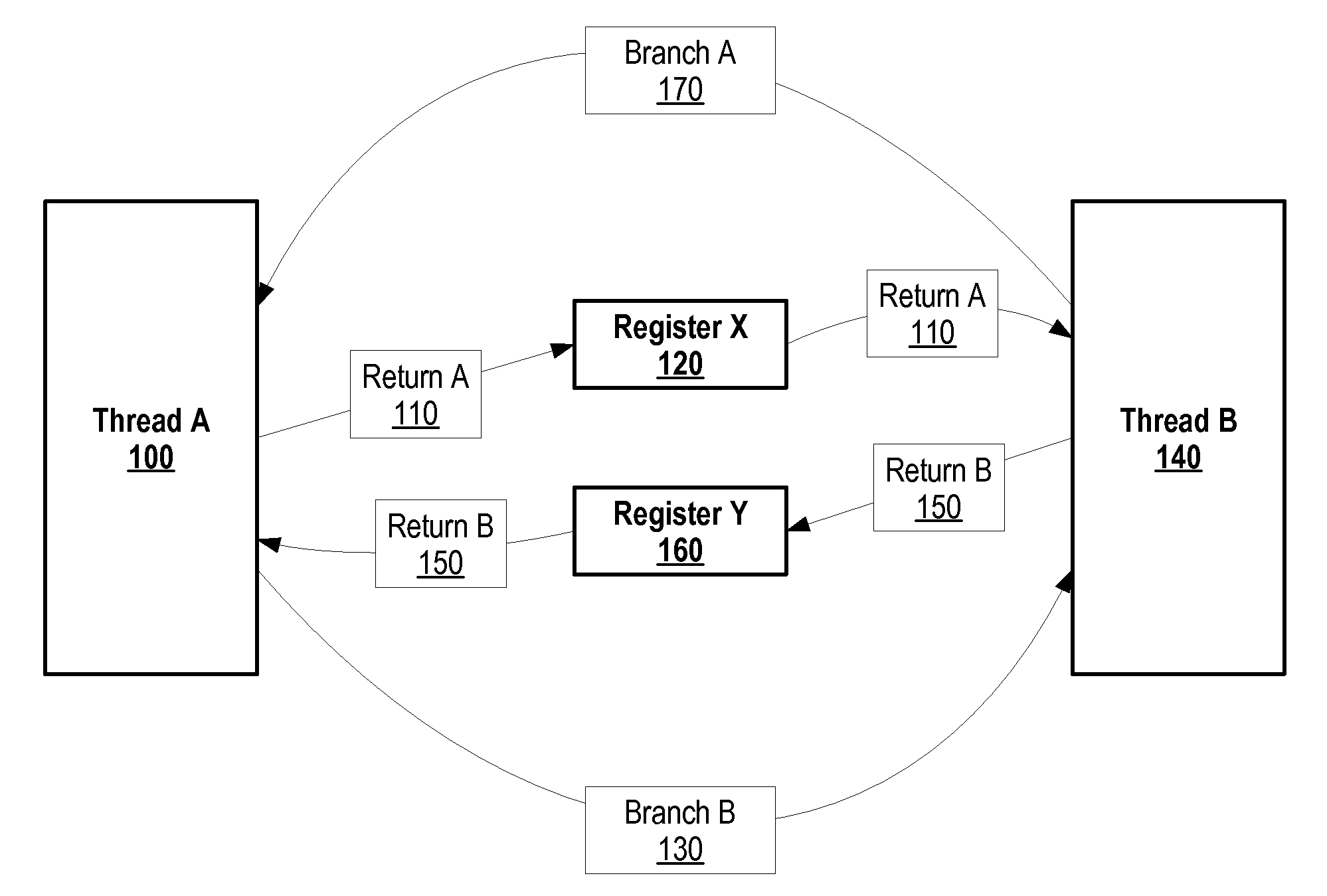

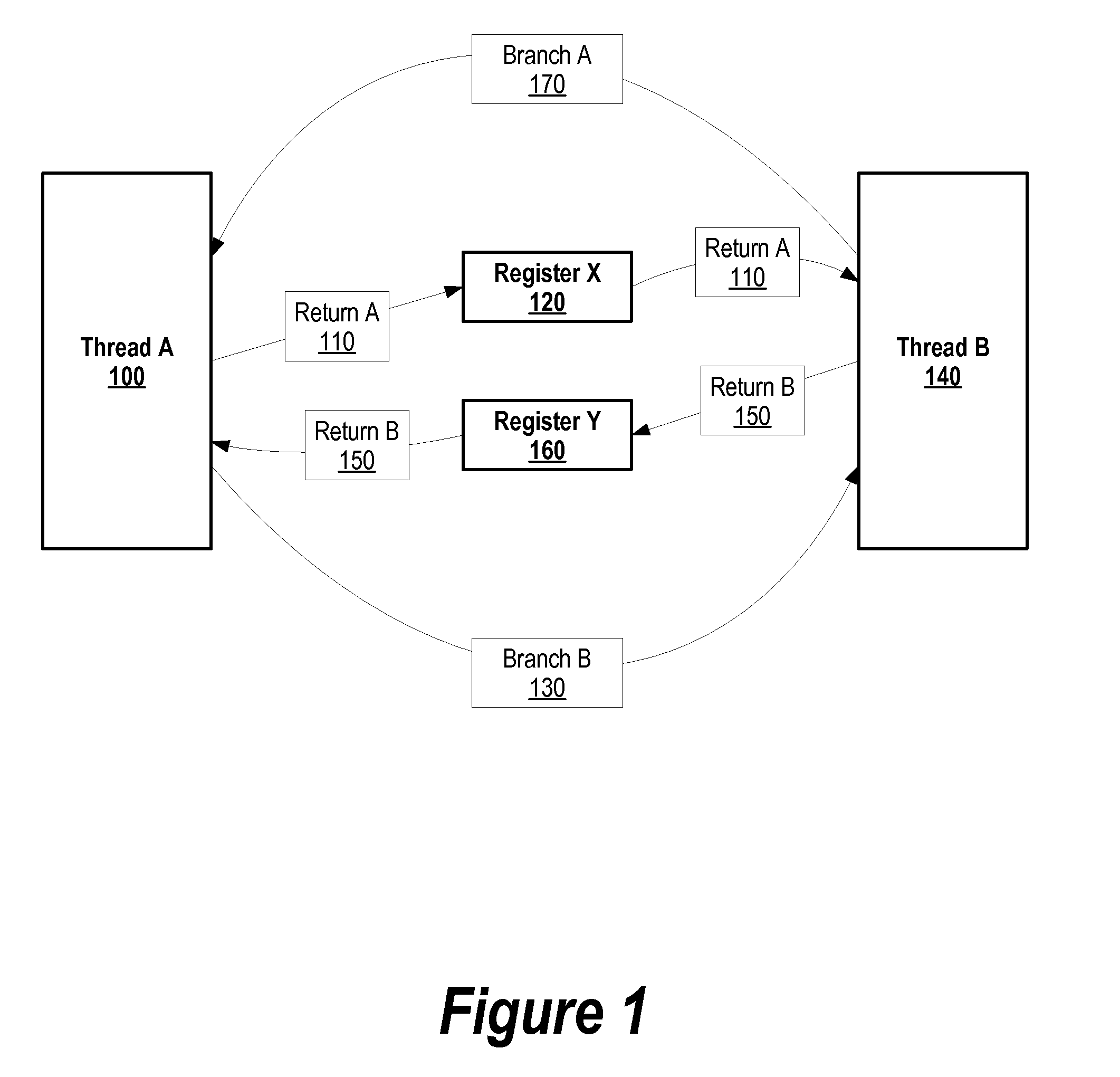

Method and apparatus for efficient helper thread state initialization using inter-thread register copy

InactiveUS20110296431A1Digital computer detailsMultiprogramming arrangementsMemory hierarchyAccess time

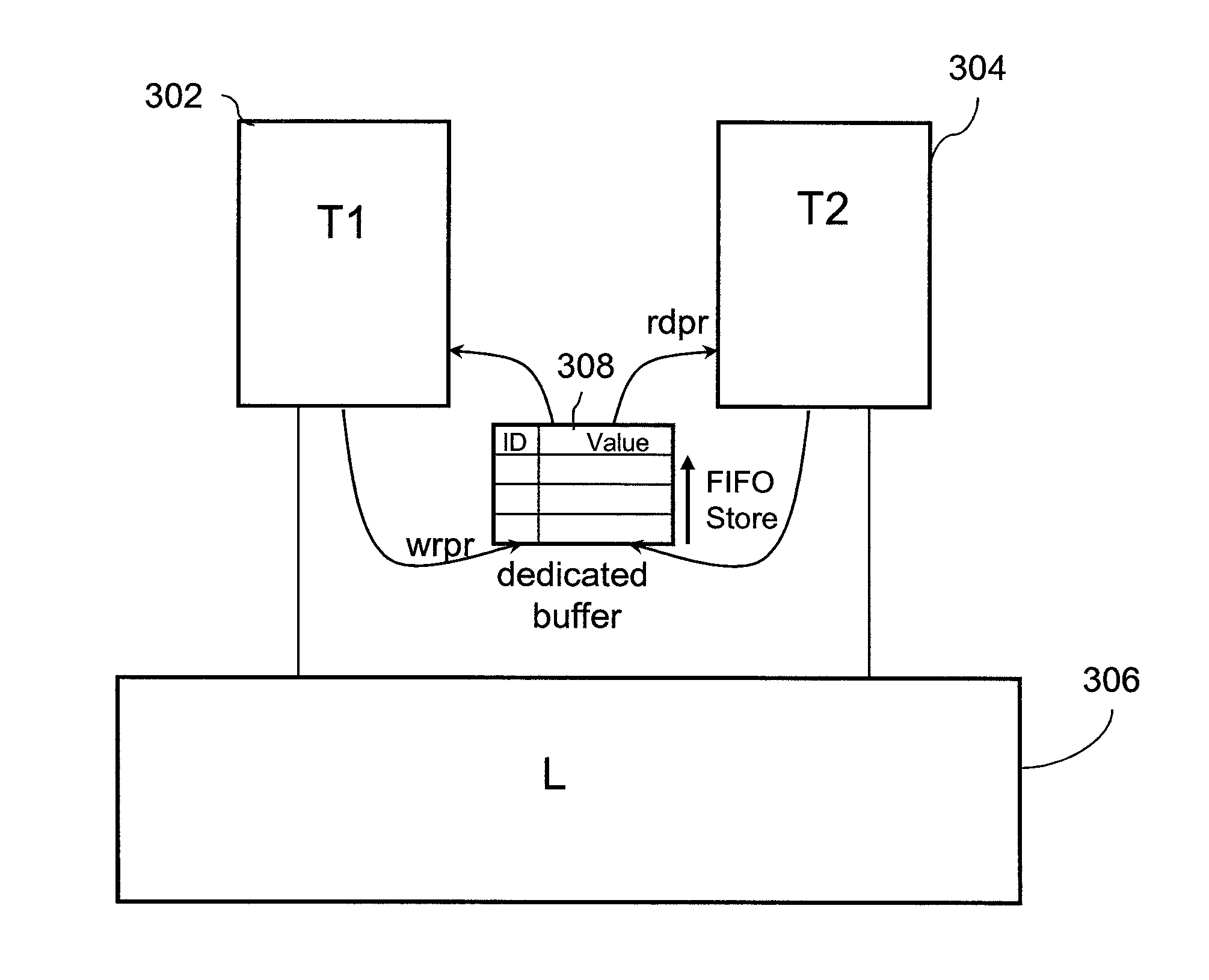

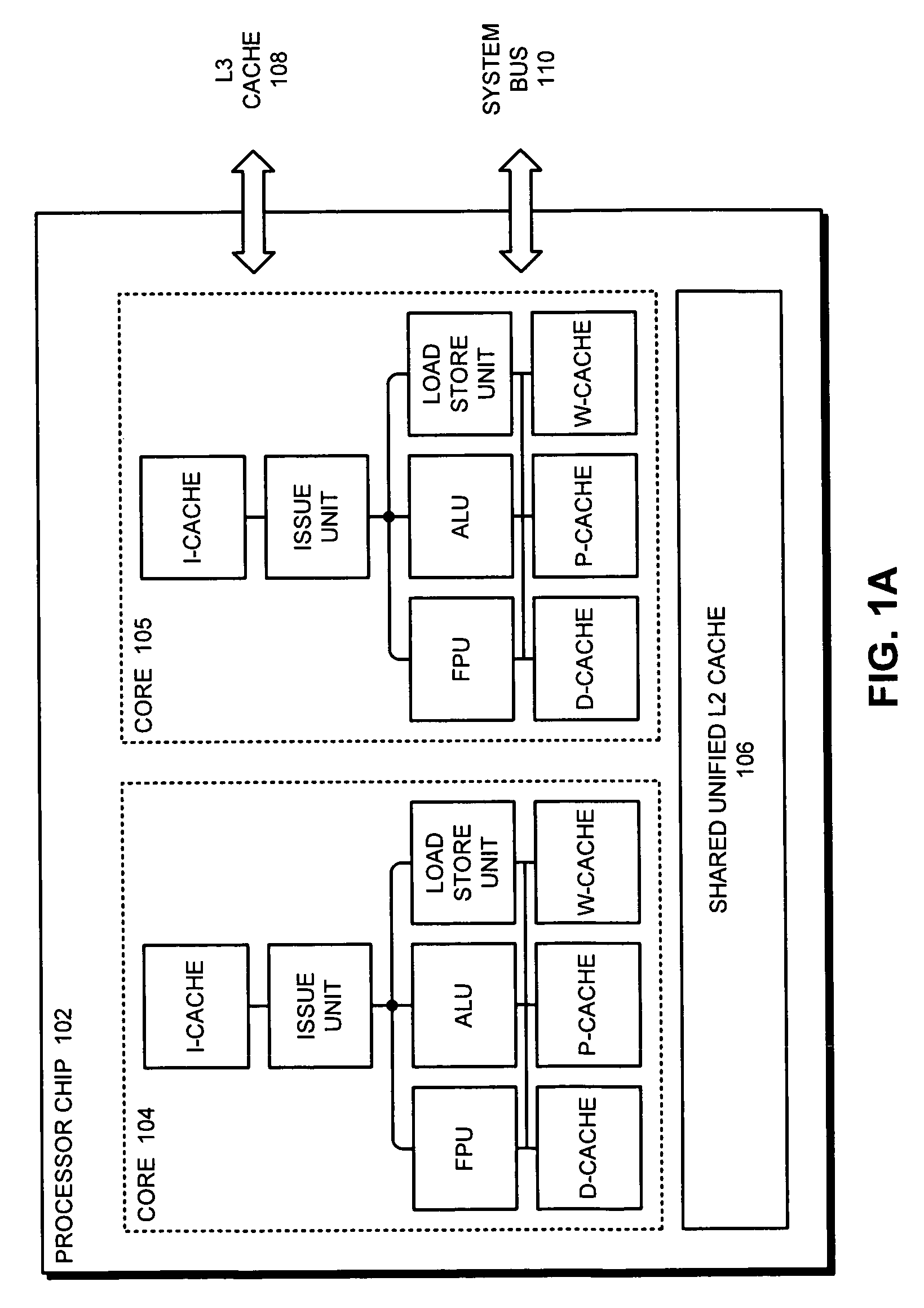

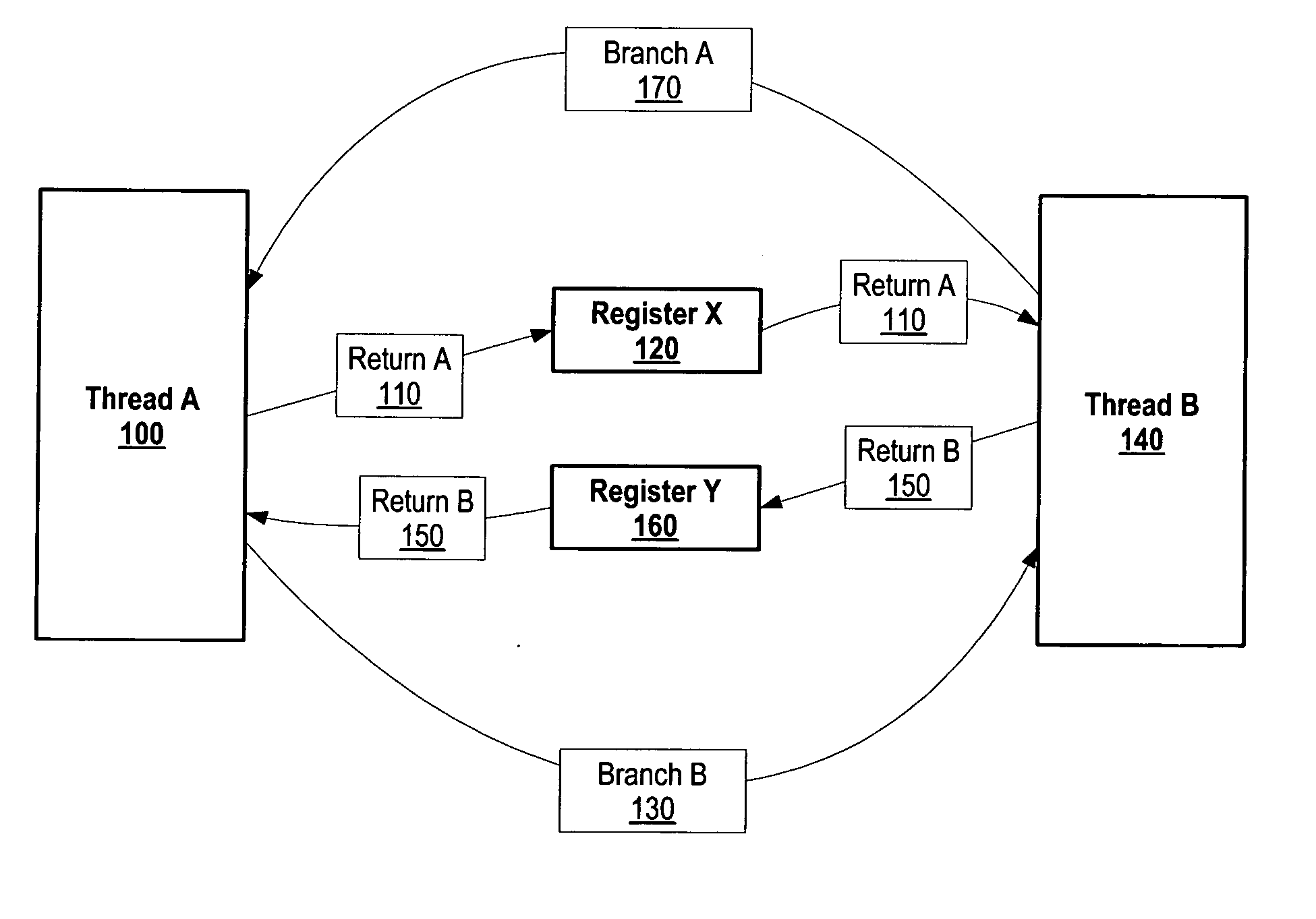

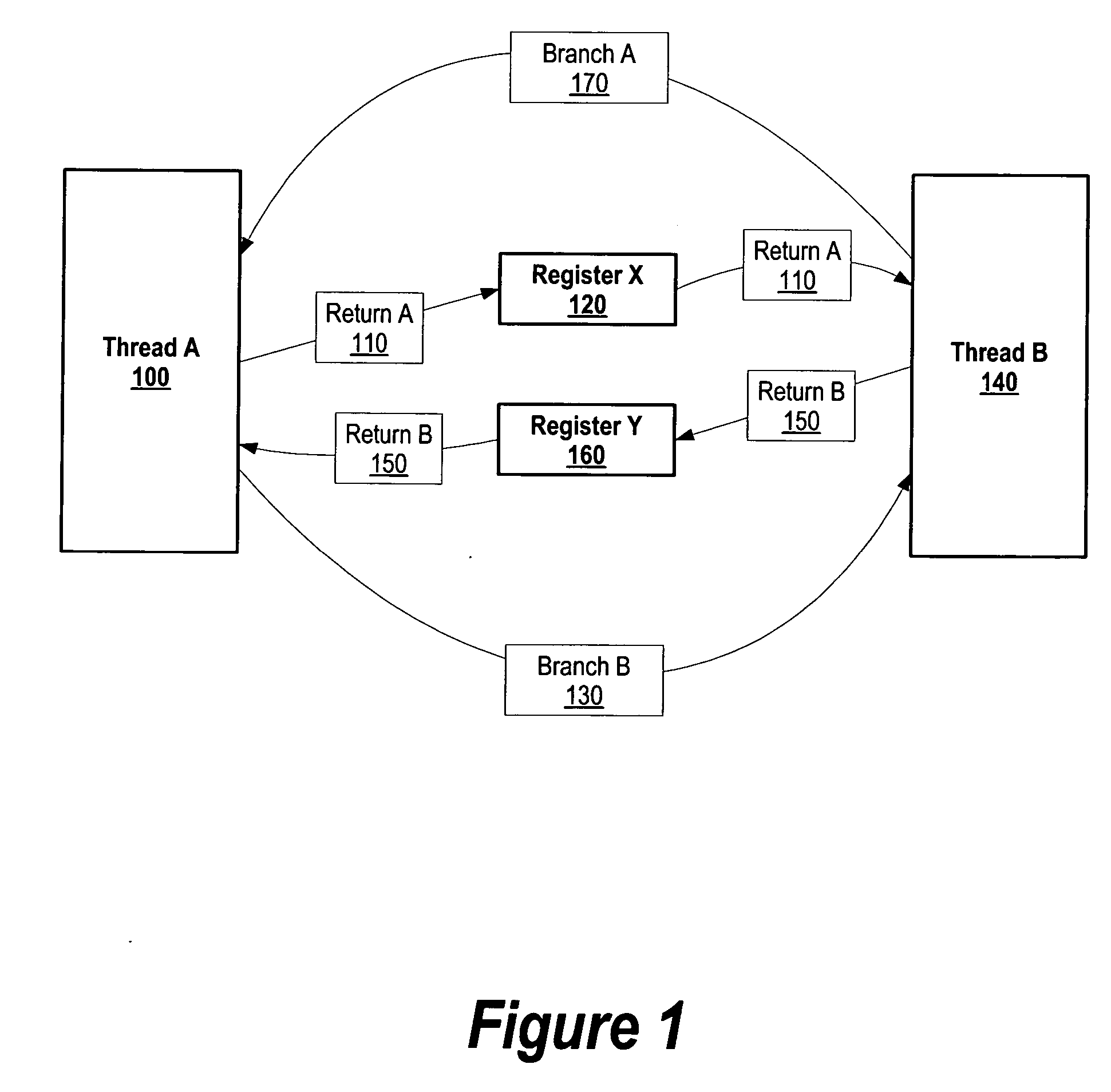

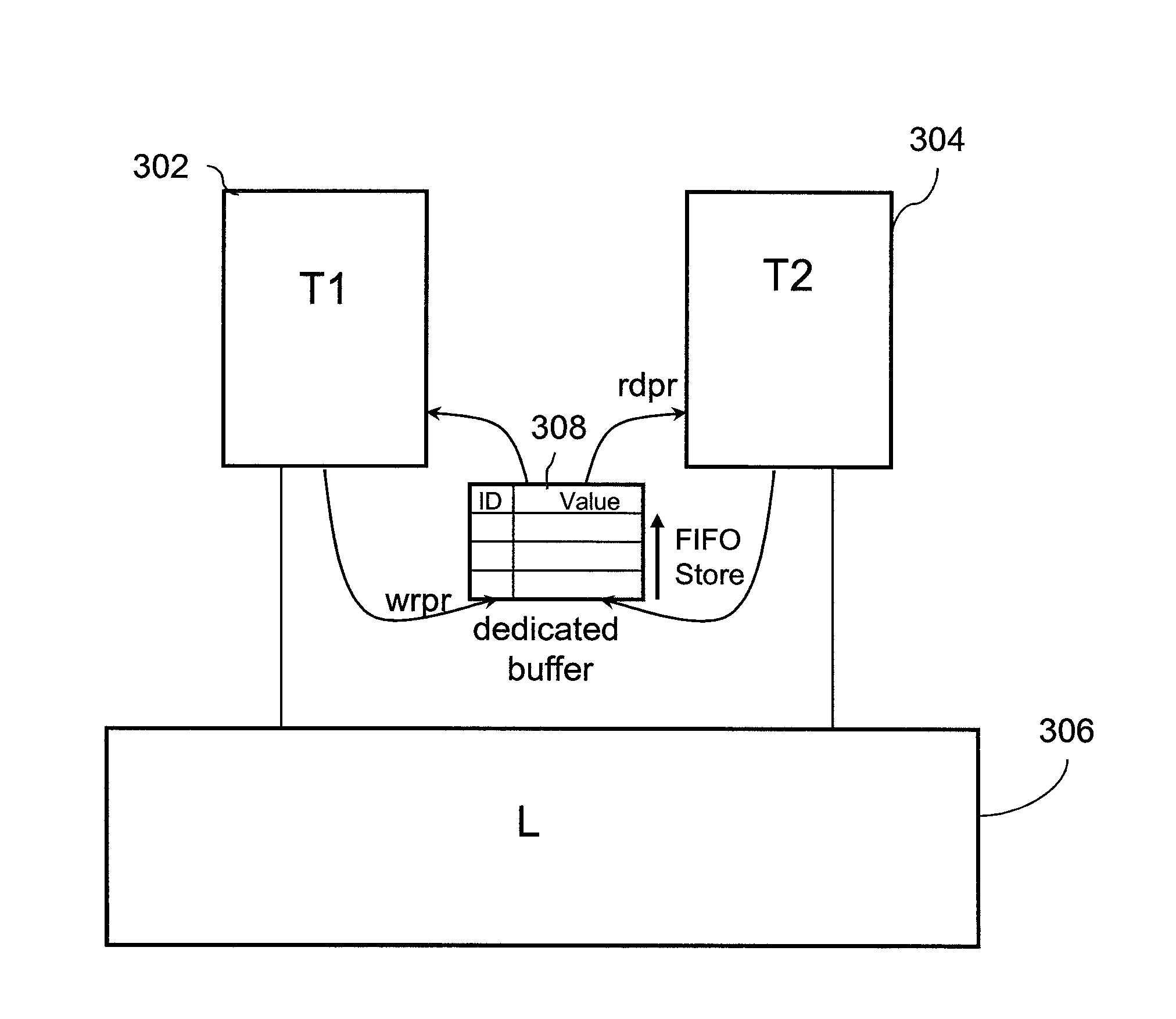

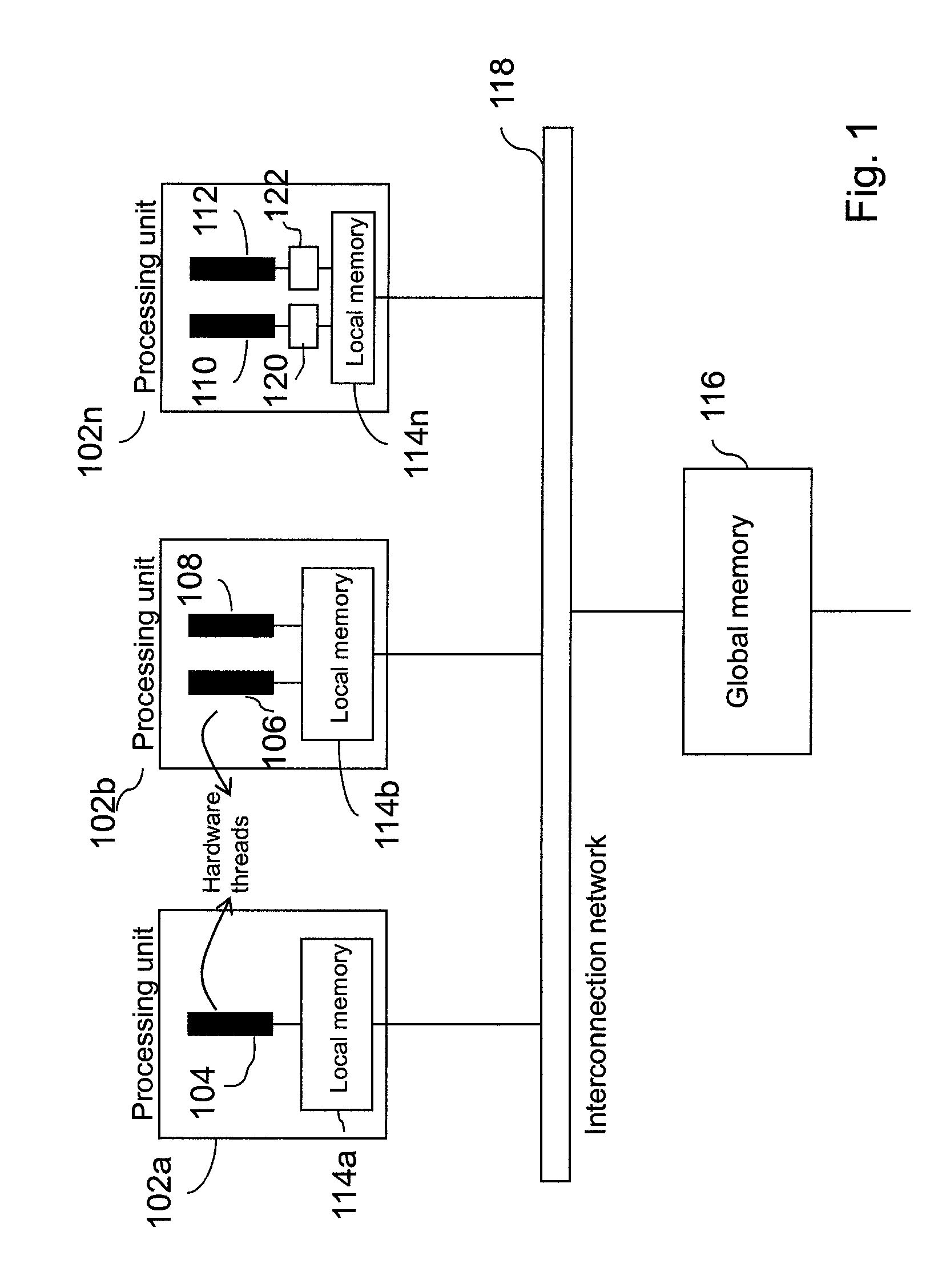

This disclosure describes a method and system that may enable fast, hardware-assisted, producer-consumer style communication of values between threads. The method, in one aspect, uses a dedicated hardware buffer as an intermediary storage for transferring values from registers in one thread to registers in another thread. The method may provide a generic, programmable solution that can transfer any subset of register values between threads in any given order, where the source and target registers may or may not be correlated. The method also may allow for determinate access times, since it completely bypasses the memory hierarchy. Also, the method is designed to be lightweight, focusing on communication, and keeping synchronization facilities orthogonal to the communication mechanism. It may be used by a helper thread that performs data prefetching for an application thread, for example, to initialize the upward-exposed reads in the address computation slice of the helper thread code.

Owner:IBM CORP

Facilitating communication and synchronization between main and scout threads

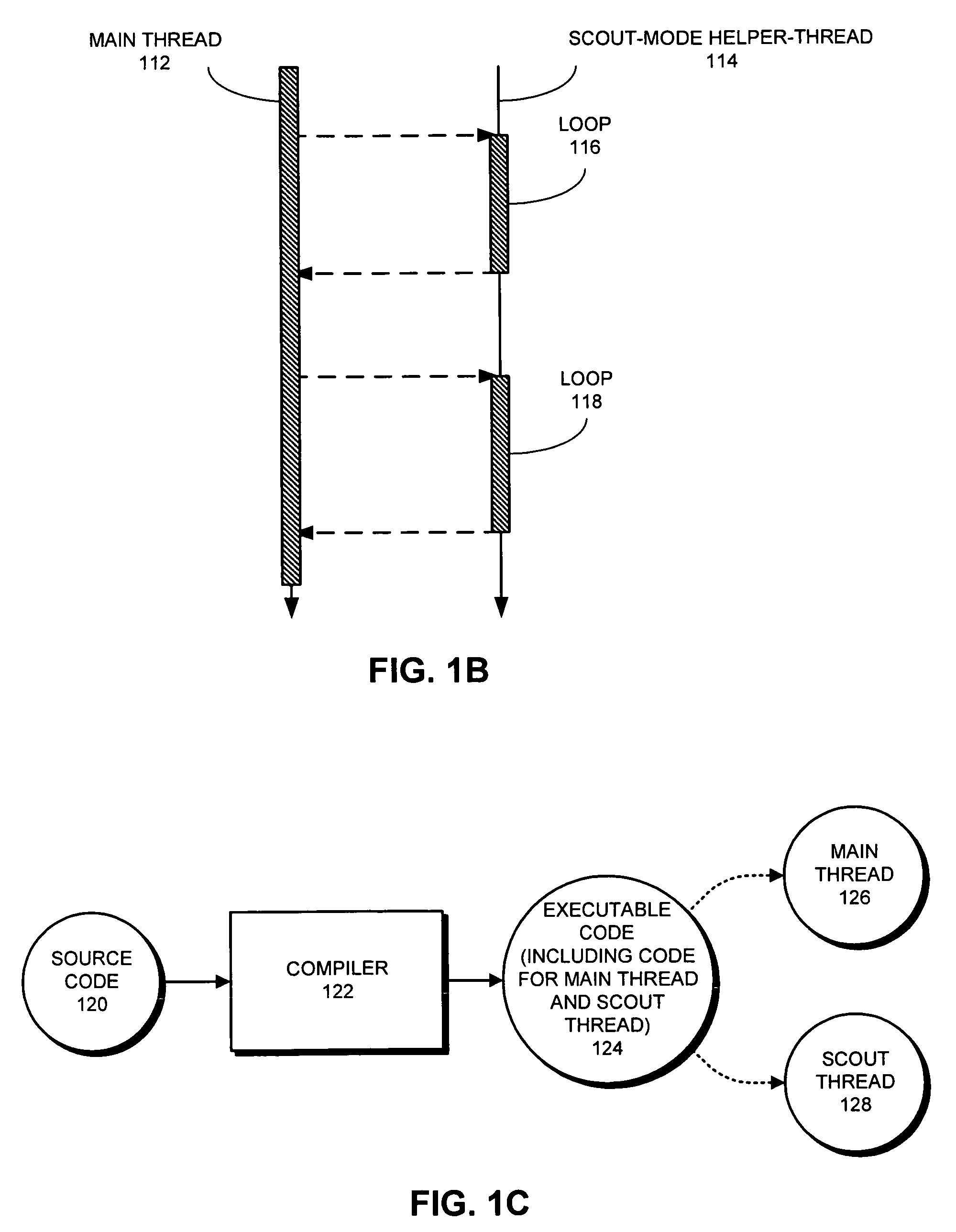

ActiveUS20070022422A1Preventing executionMemory architecture accessing/allocationProgram synchronisationParallel computingThreaded code

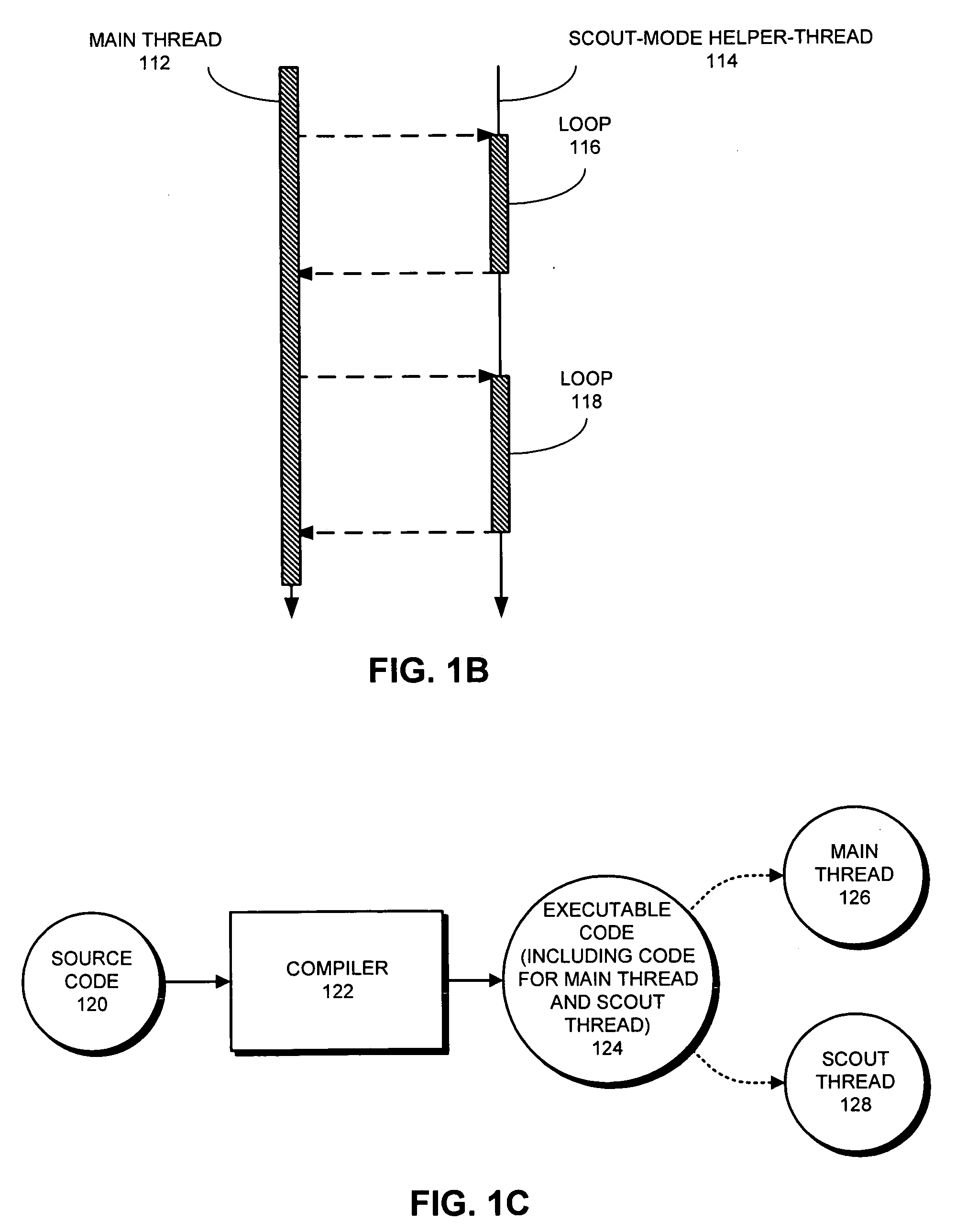

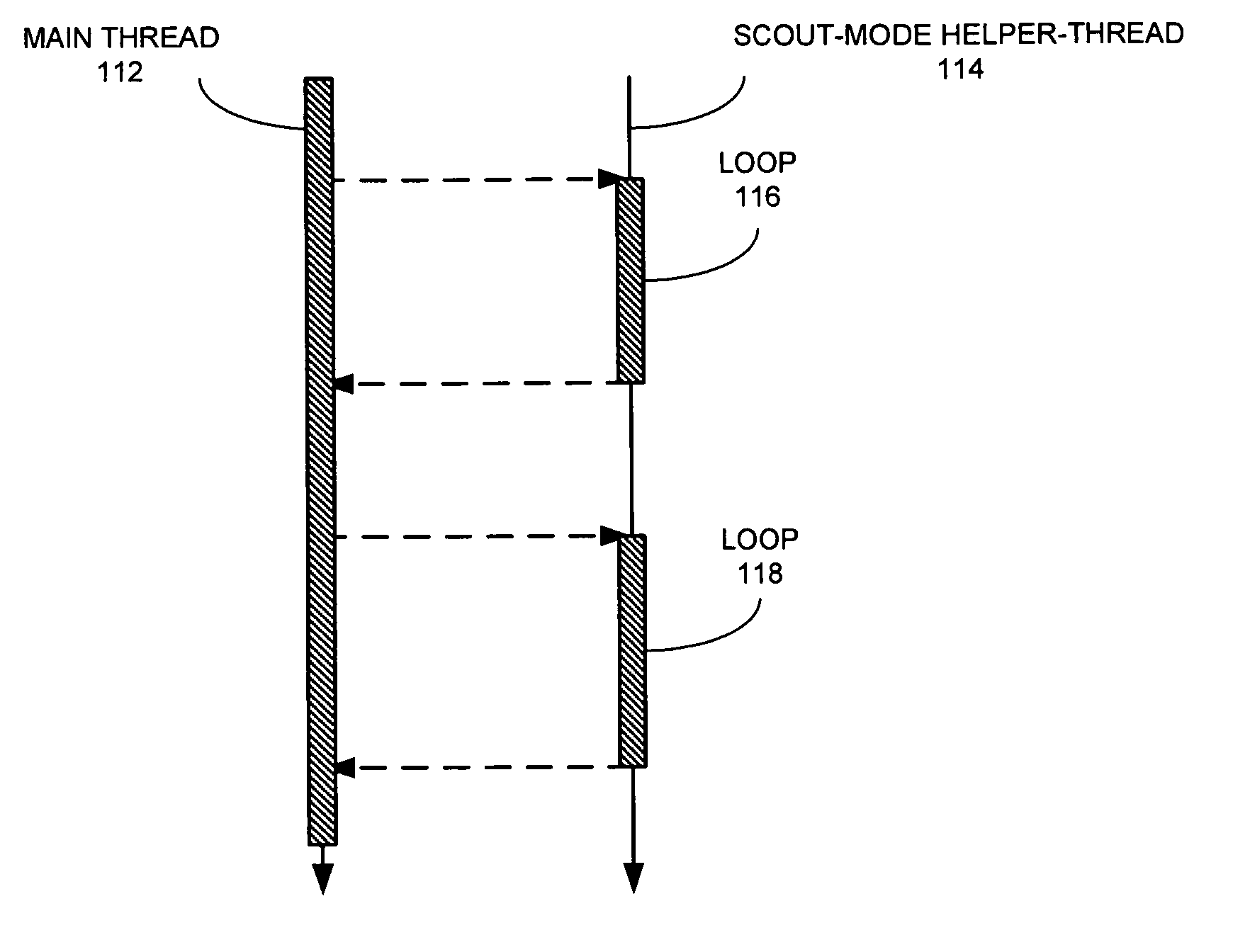

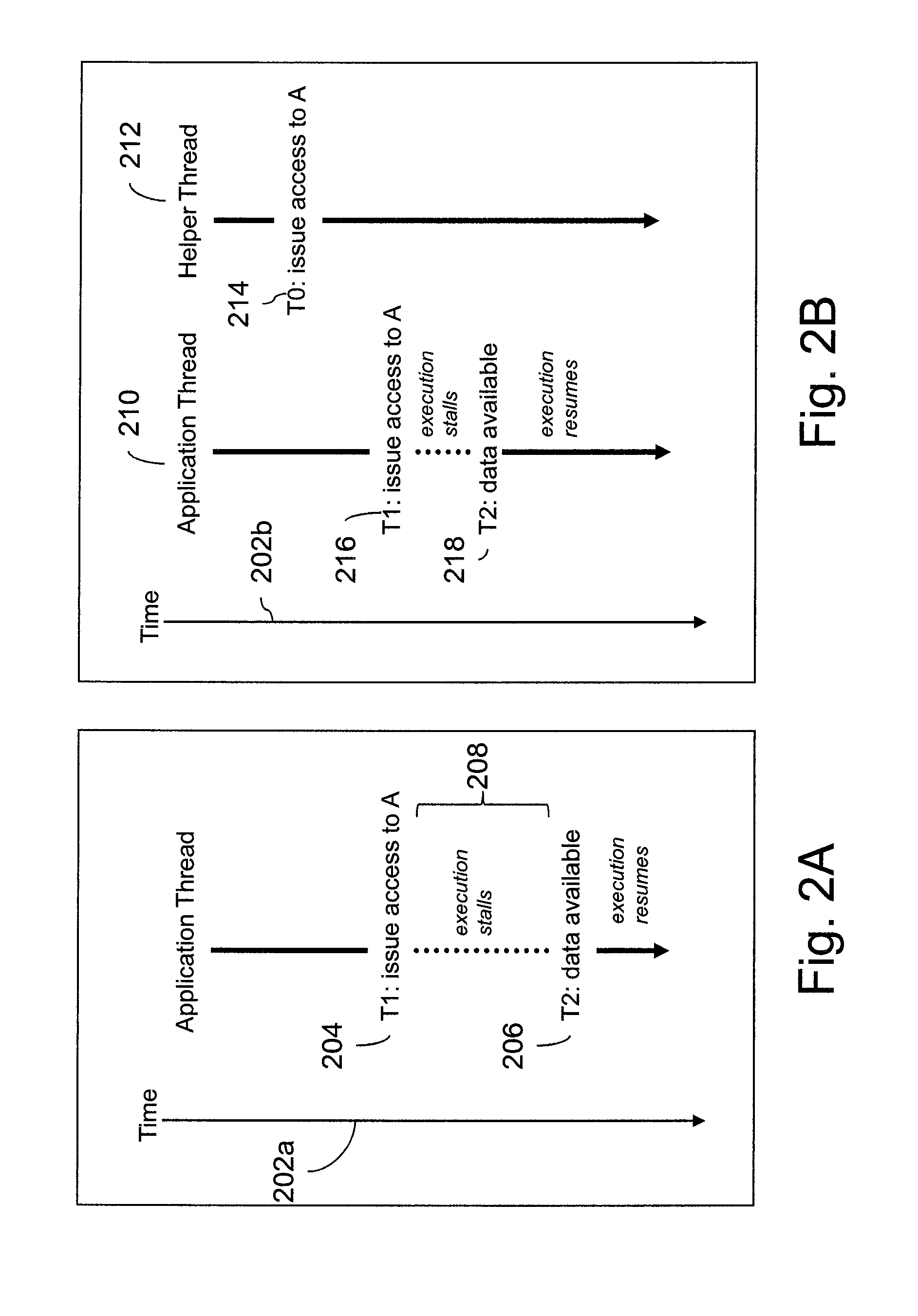

One embodiment of the present invention provides a system for communicating and performing synchronization operations between a main thread and a helper-thread. The system starts by executing a program in a main thread. Upon encountering a loop which has associated helper-thread code, the system commences the execution of the code by the helper-thread separately and in parallel with the main thread. While executing the code by the helper-thread, the system periodically checks the progress of the main thread and deactivates the helper-thread if the code being executed by the helper-thread is no longer performing useful work. Hence, the helper-thread is executes in advance of where the main thread is executing to prefetch data items for the main thread without unnecessarily consuming processor resources or hampering the execution of the main thread.

Owner:ORACLE INT CORP

Power management system and method

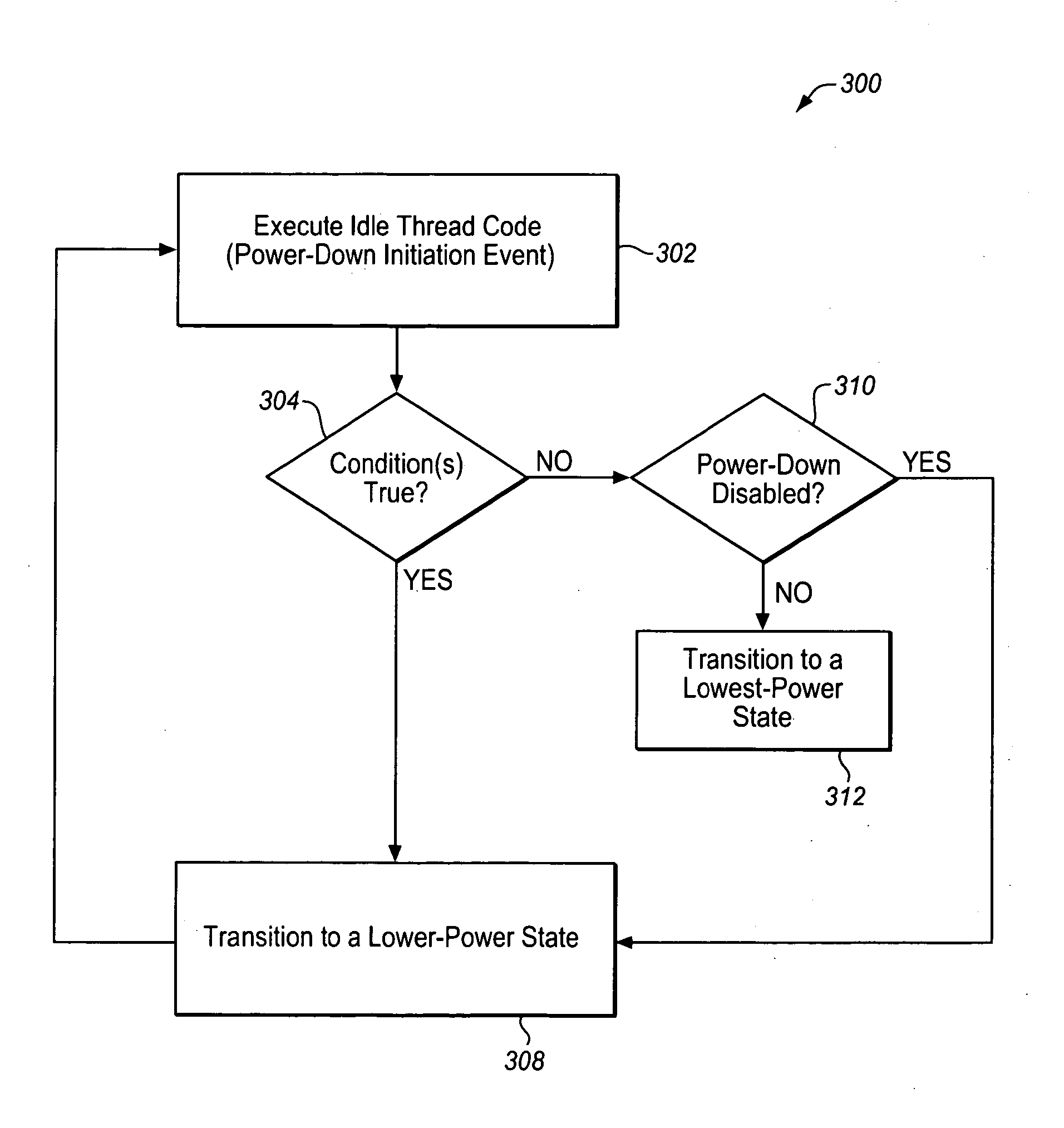

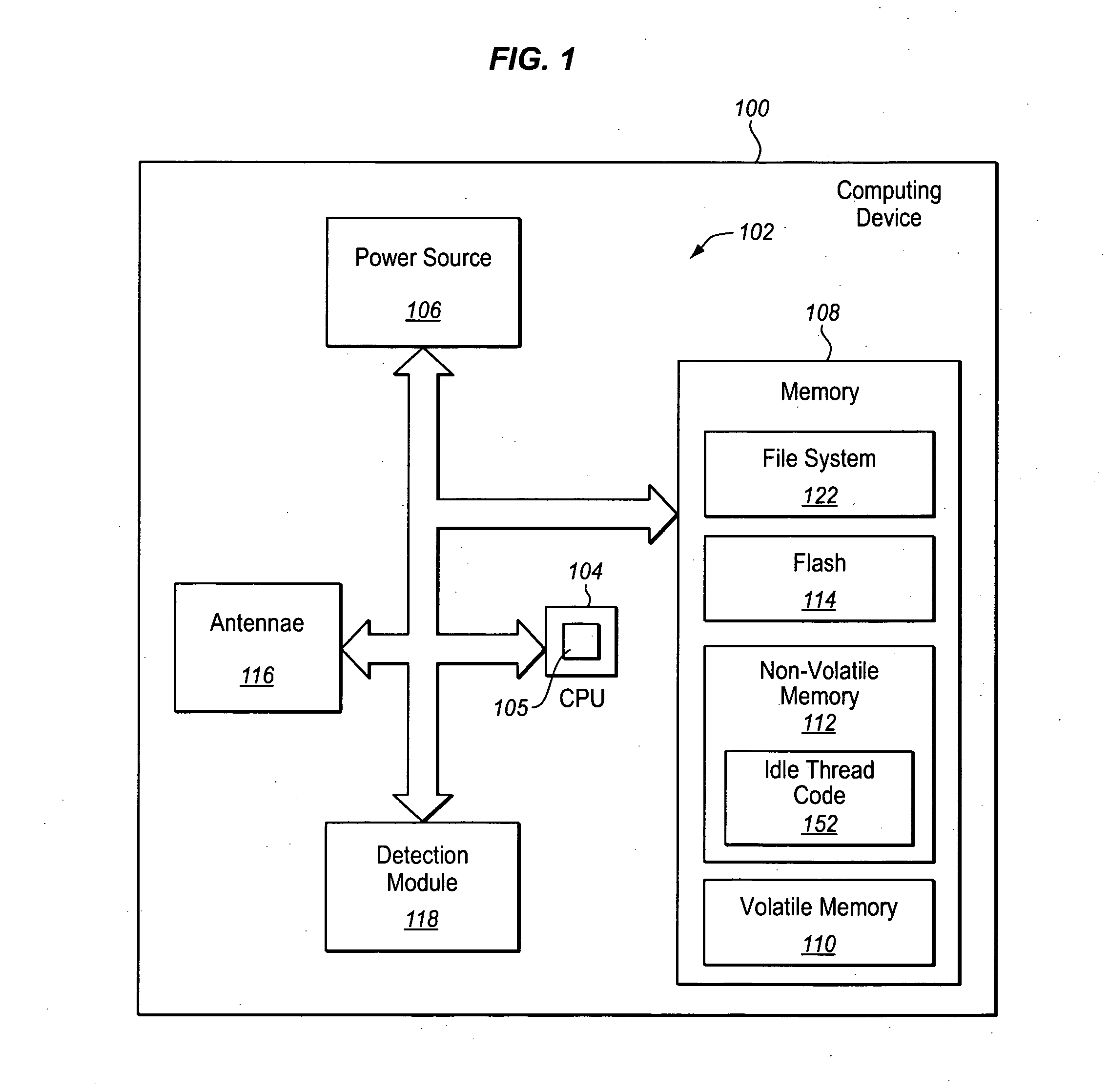

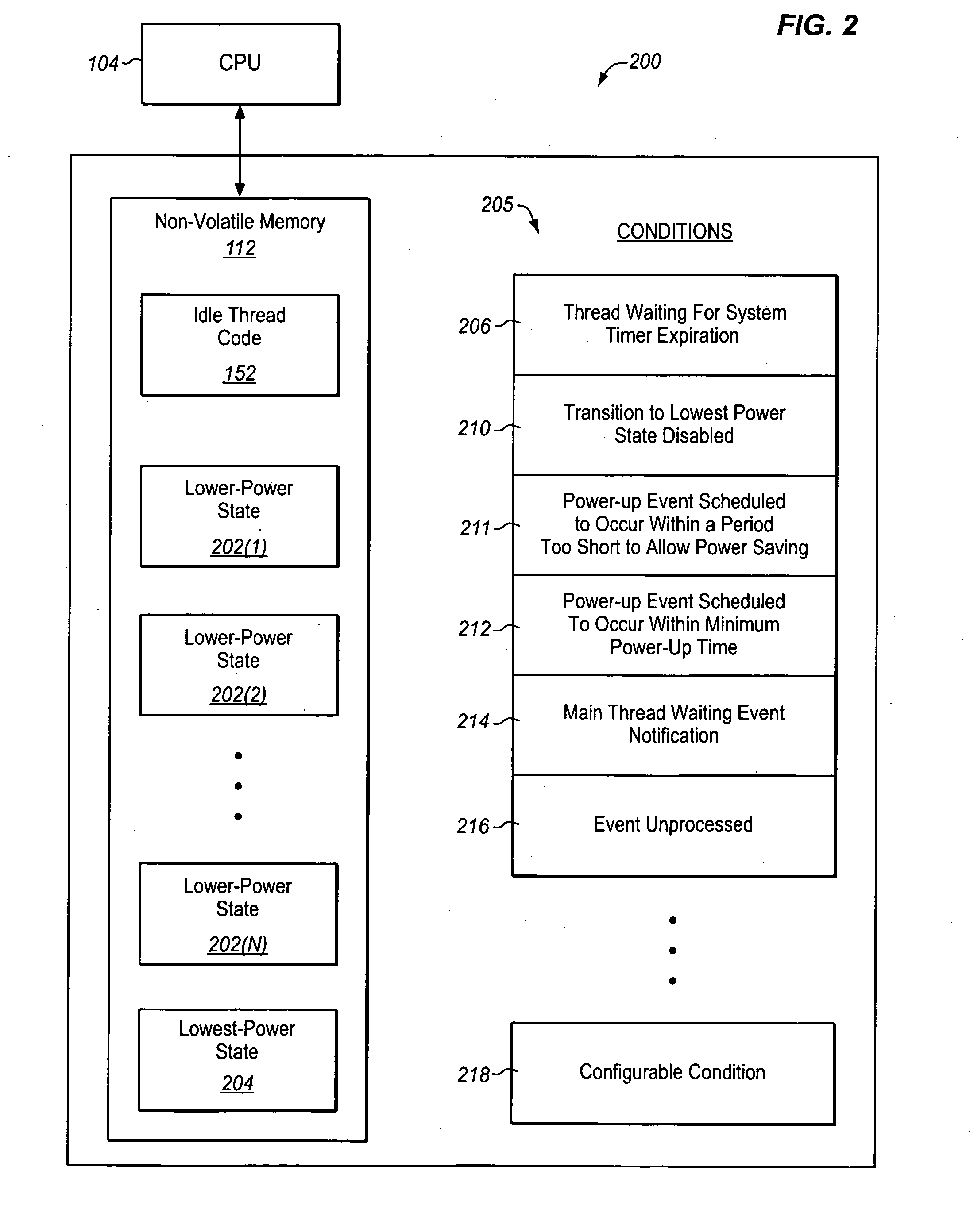

InactiveUS20080098245A1Energy efficient ICTDigital data processing detailsEngineeringState switching

Power management for a computing device is described based on idle thread code execution and other conditions. In one example, a controller is operated at a first power state. Then the controller is transitioned from the first power state to a second lower power state after it starts executing idle thread code. As an additional optional feature it may be determined whether any one or more of a plurality of conditions is true and the controller may be transitioned from the first power state to the second power state if one or more of the plurality of conditions is true.

Owner:G2 MICROSYST

Technique for dynamically restricting thread concurrency without rewriting thread code

ActiveUS8245207B1Easy to scaleReduce the amount requiredSoftware engineeringDigital computer detailsParallel computingWorkload

Owner:NETWORK APPLIANCE INC

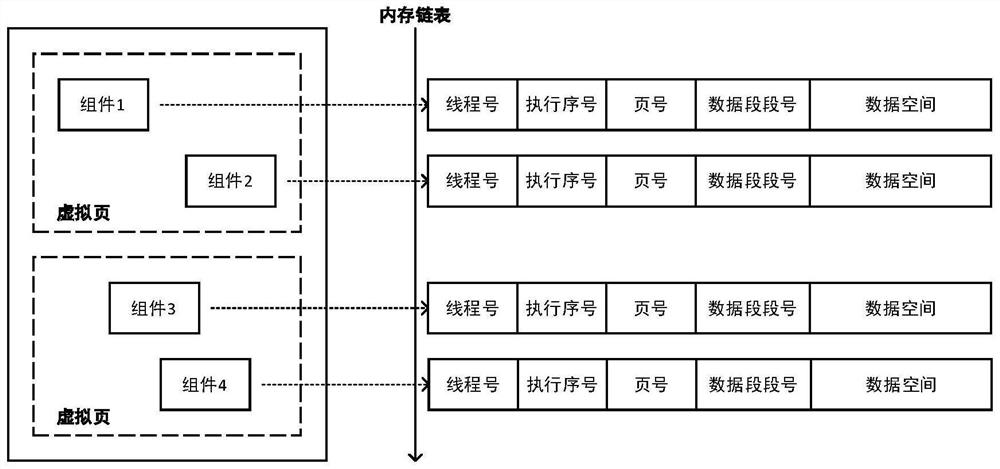

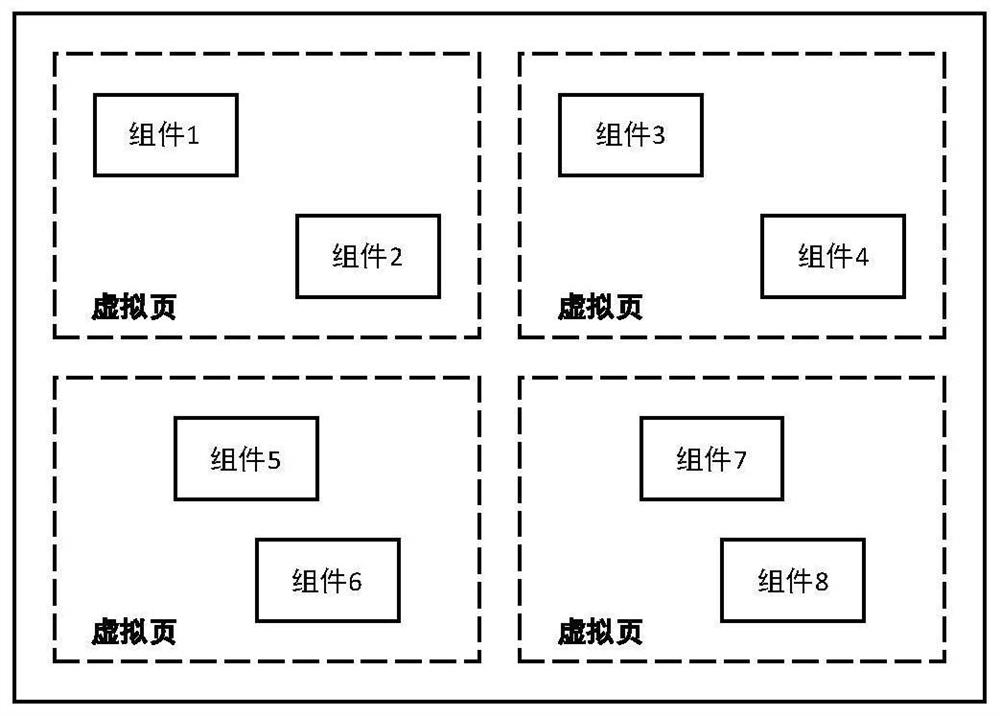

Method and device for mobile terminal to access webpage

InactiveCN102065114AEasy and smooth accessTransmissionSpecial data processing applicationsThumbnailComputer terminal

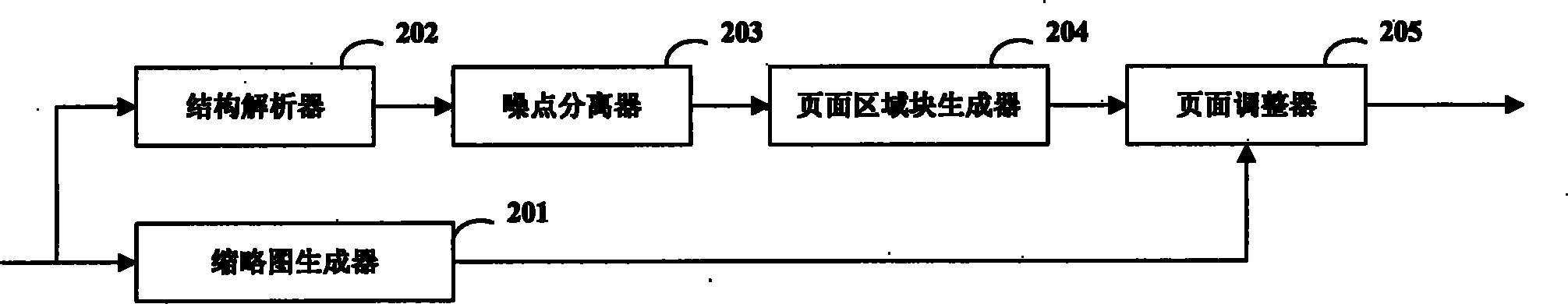

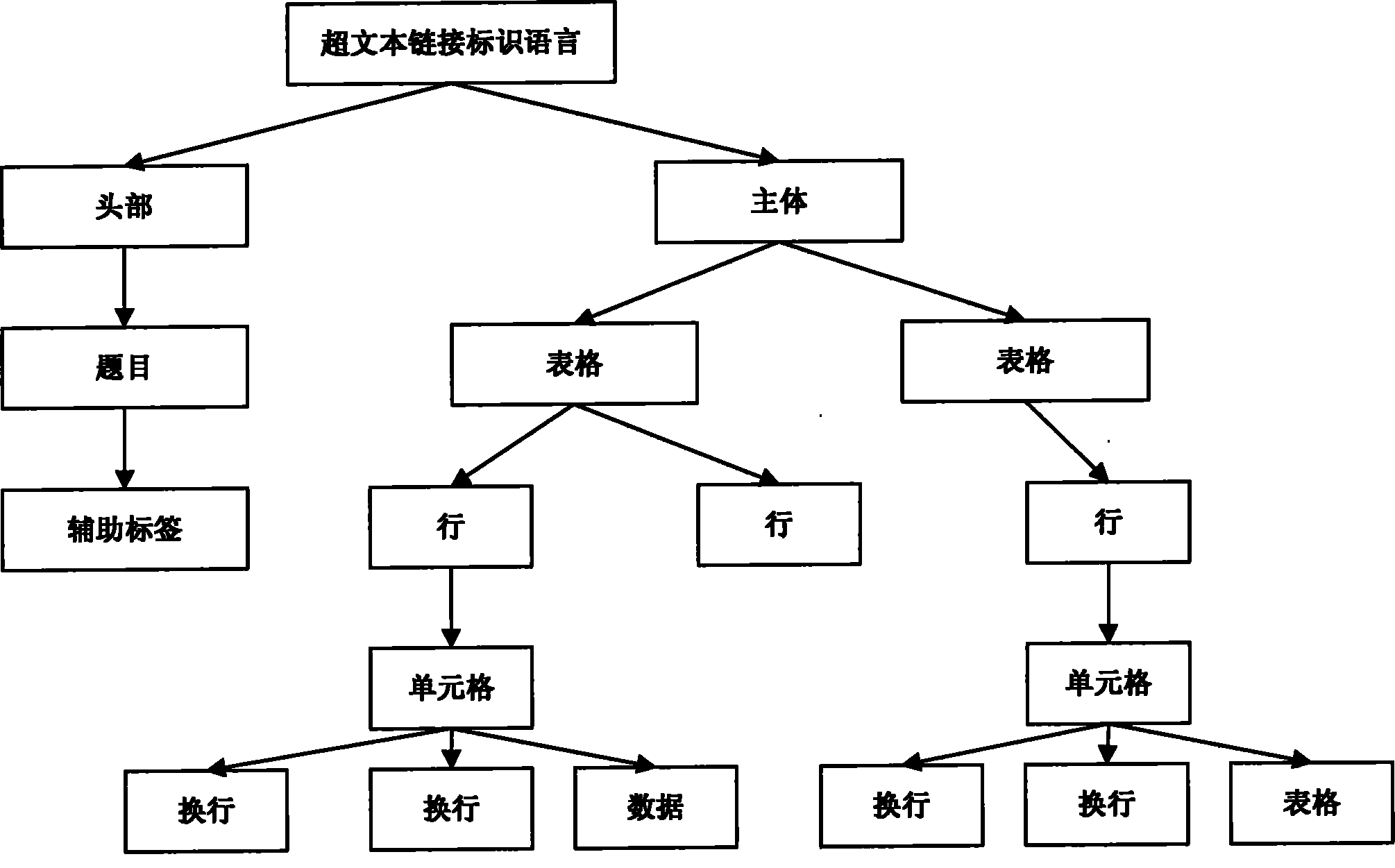

The invention discloses a device for a mobile terminal to access a webpage. The device comprises a thumbnail generator, a structure processor, a noise eliminator, a page blocker and a page tailor, wherein the thumbnail generator generates a thumbnail picture in a joint picture group (JPG) format according to a WEB page of a WEB website and transmits the thumbnail picture to the page tailor; the structure processor processes codes of the WEB page of the WEB website into a document object model (DOM) tree and transmits the DOM tree to the noise eliminator; the noise eliminator trims the DOM tree and transmits the trimmed DOM tree to the page blocker; the page blocker generates a regional Block according to the trimmed DOM tree and transmits the Block to the page tailor; and the page tailor analyzes the Block to acquire a threaded code, a picture and characters and transmits the threaded code, the picture, the characters and the thumbnail picture to the mobile terminal. The invention also discloses a method for the mobile terminal to access the webpage. After the embodiment provided by the invention is applied, the mobile terminal can access the WEB webpage without being influenced by hardware performance of the mobile terminal.

Owner:中国移动通信集团重庆有限公司

Facilitating communication and synchronization between main and scout threads

ActiveUS7950012B2Preventing executionMemory architecture accessing/allocationProgram synchronisationParallel computingFacilitated communication

One embodiment of the present invention provides a system for communicating and performing synchronization operations between a main thread and a helper-thread. The system starts by executing a program in a main thread. Upon encountering a loop which has associated helper-thread code, the system commences the execution of the code by the helper-thread separately and in parallel with the main thread. While executing the code by the helper-thread, the system periodically checks the progress of the main thread and deactivates the helper-thread if the code being executed by the helper-thread is no longer performing useful work. Hence, the helper-thread is executes in advance of where the main thread is executing to prefetch data items for the main thread without unnecessarily consuming processor resources or hampering the execution of the main thread.

Owner:ORACLE INT CORP

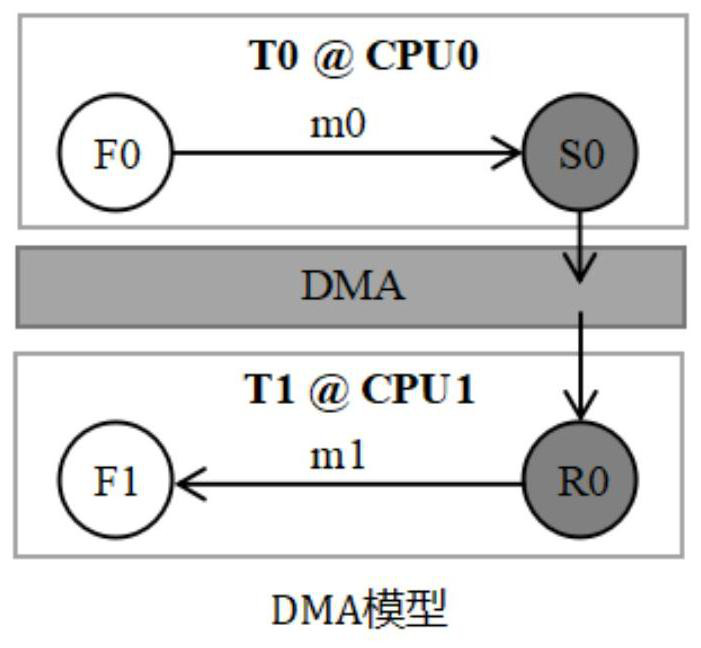

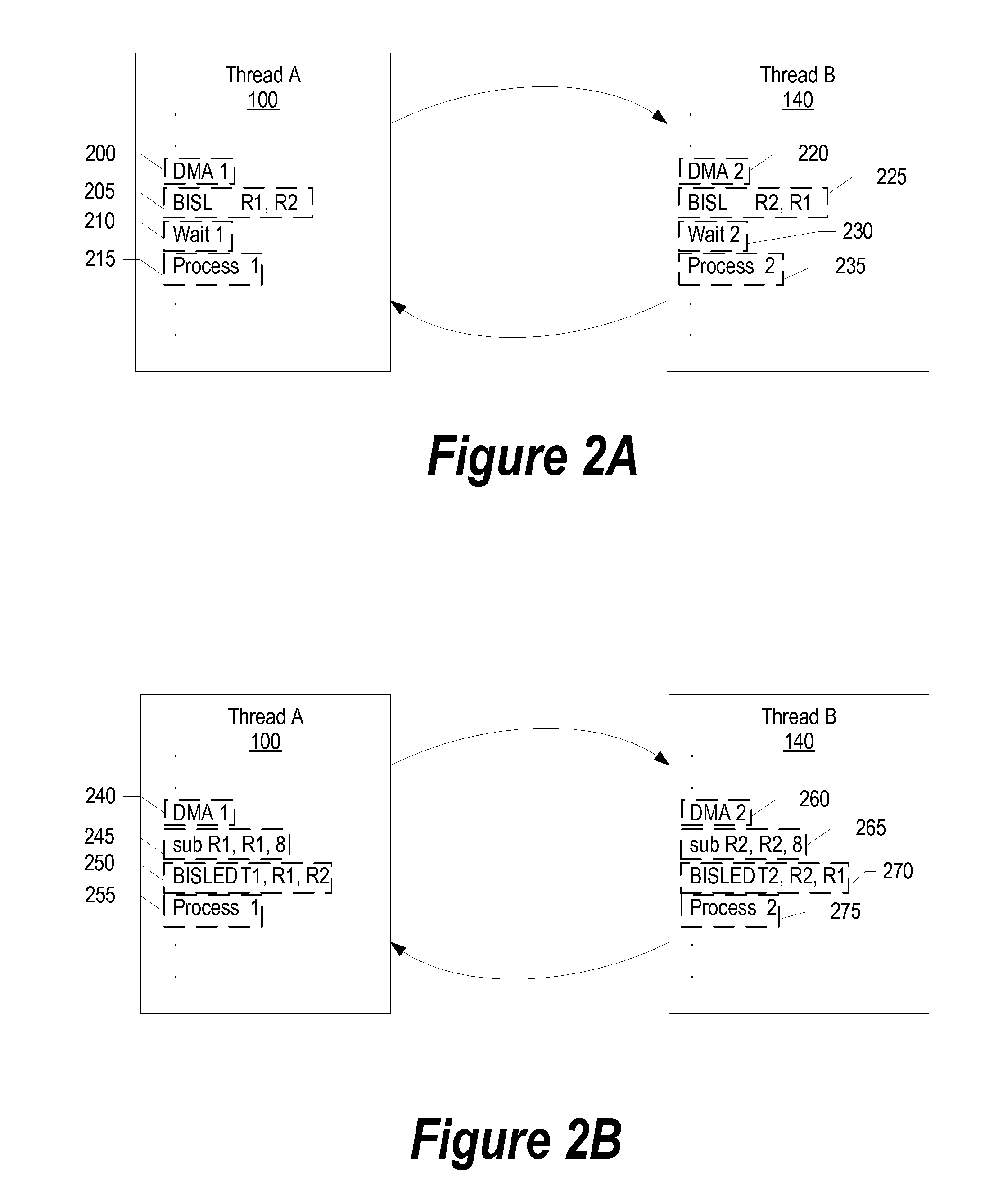

System and method for hiding memory latency

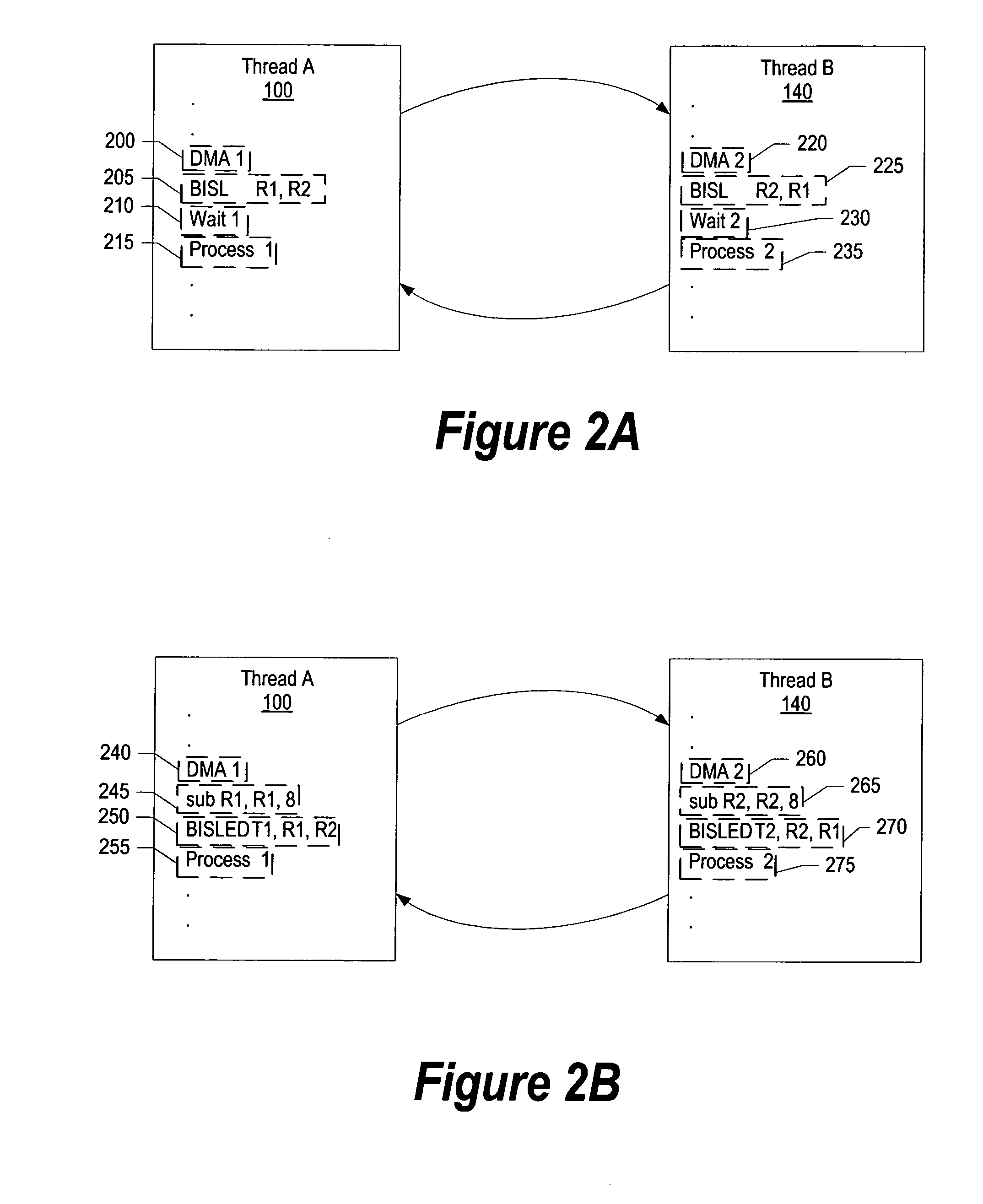

InactiveUS20060080661A1Hide memory latencyMemory latencyMultiprogramming arrangementsMemory systemsExternal dataParallel computing

A System and method for hiding memory latency in a multi-thread environment is presented. Branch Indirect and Set Link (BISL) and / or Branch Indirect and Set Link if External Data (BISLED) instructions are placed in thread code during compilation at instances that correspond to a prolonged instruction. A prolonged instruction is an instruction that instigates latency in a computer system, such as a DMA instruction. When a first thread encounters a BISL or a BISLED instruction, the first thread passes control to a second thread while the first thread's prolonged instruction executes. In turn, the computer system masks the latency of the first thread's prolonged instruction. The system can be optimized based on the memory latency by creating more threads and further dividing a register pool amongst the threads to further hide memory latency in operations that are highly memory bound.

Owner:IBM CORP

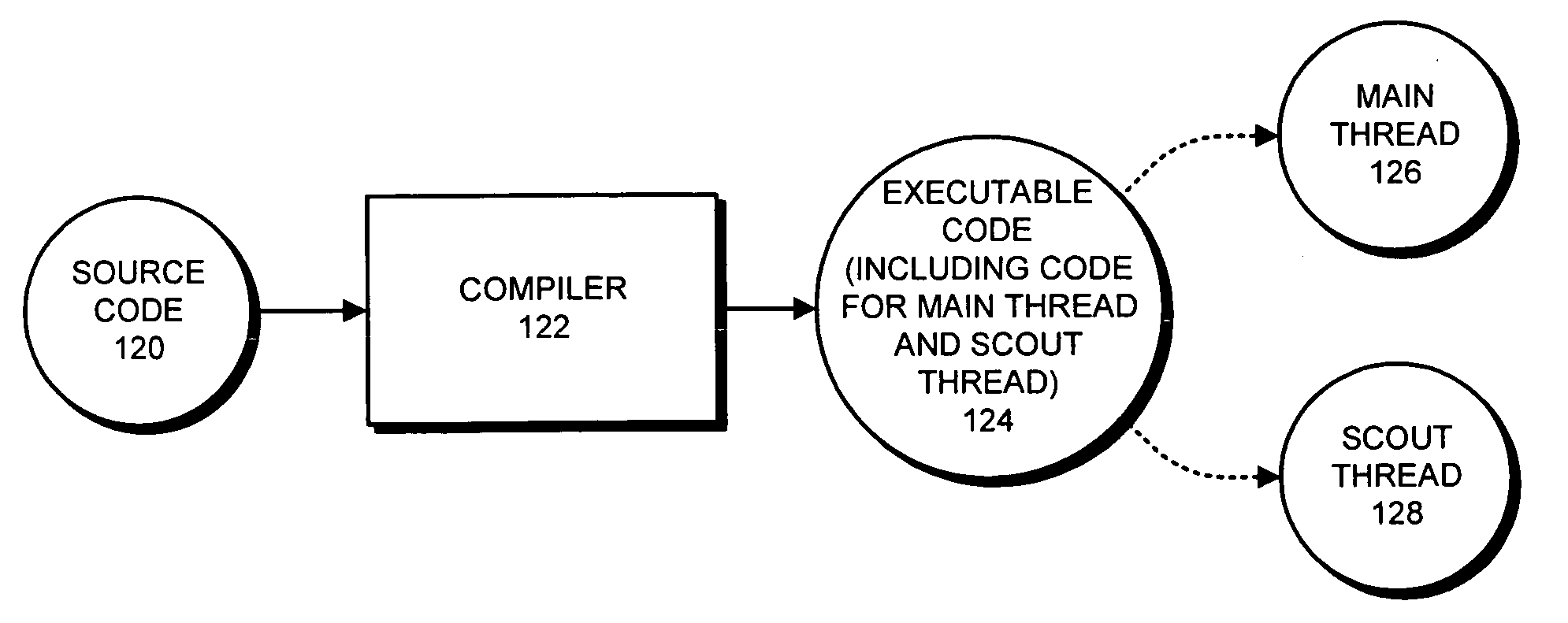

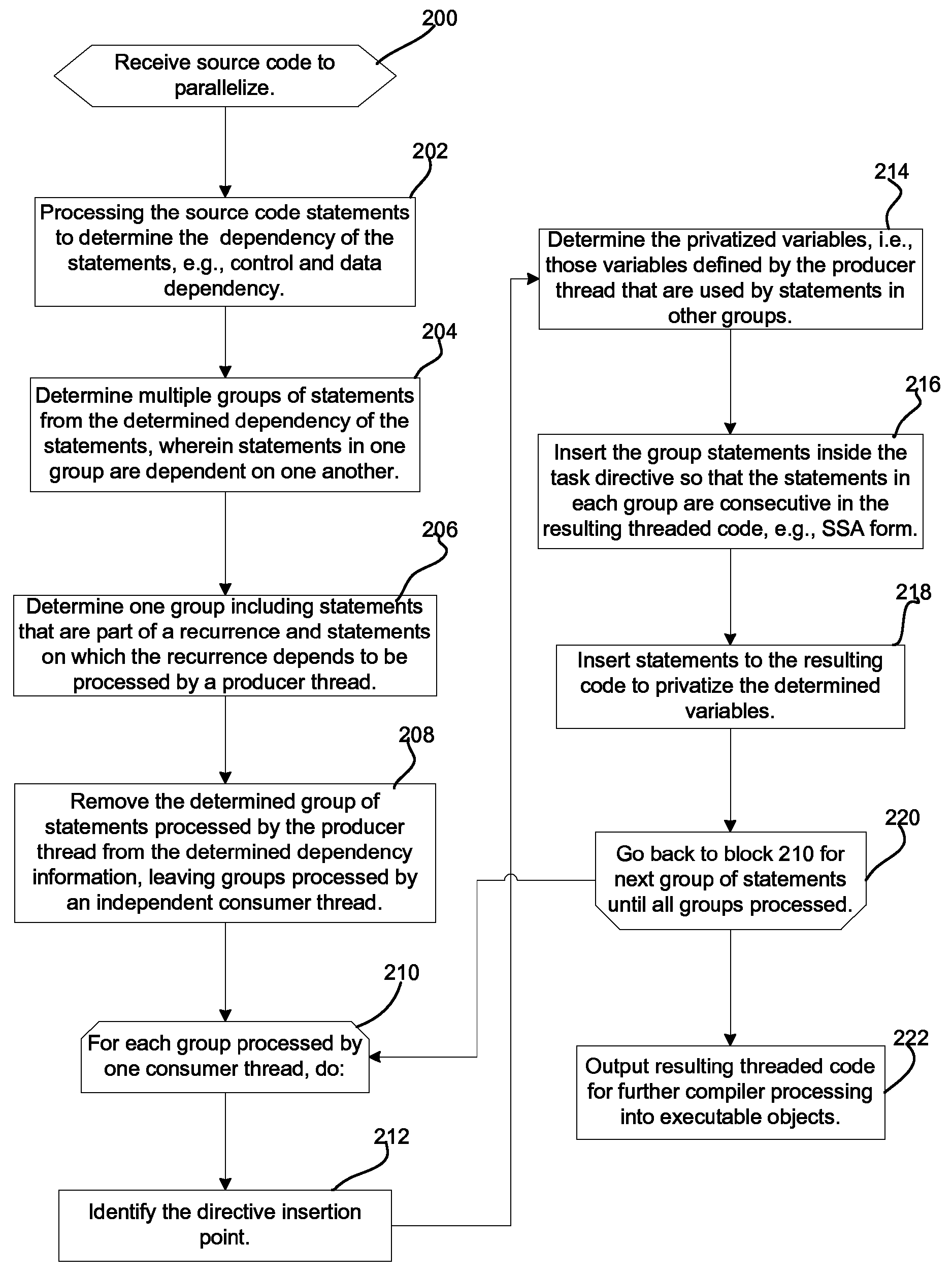

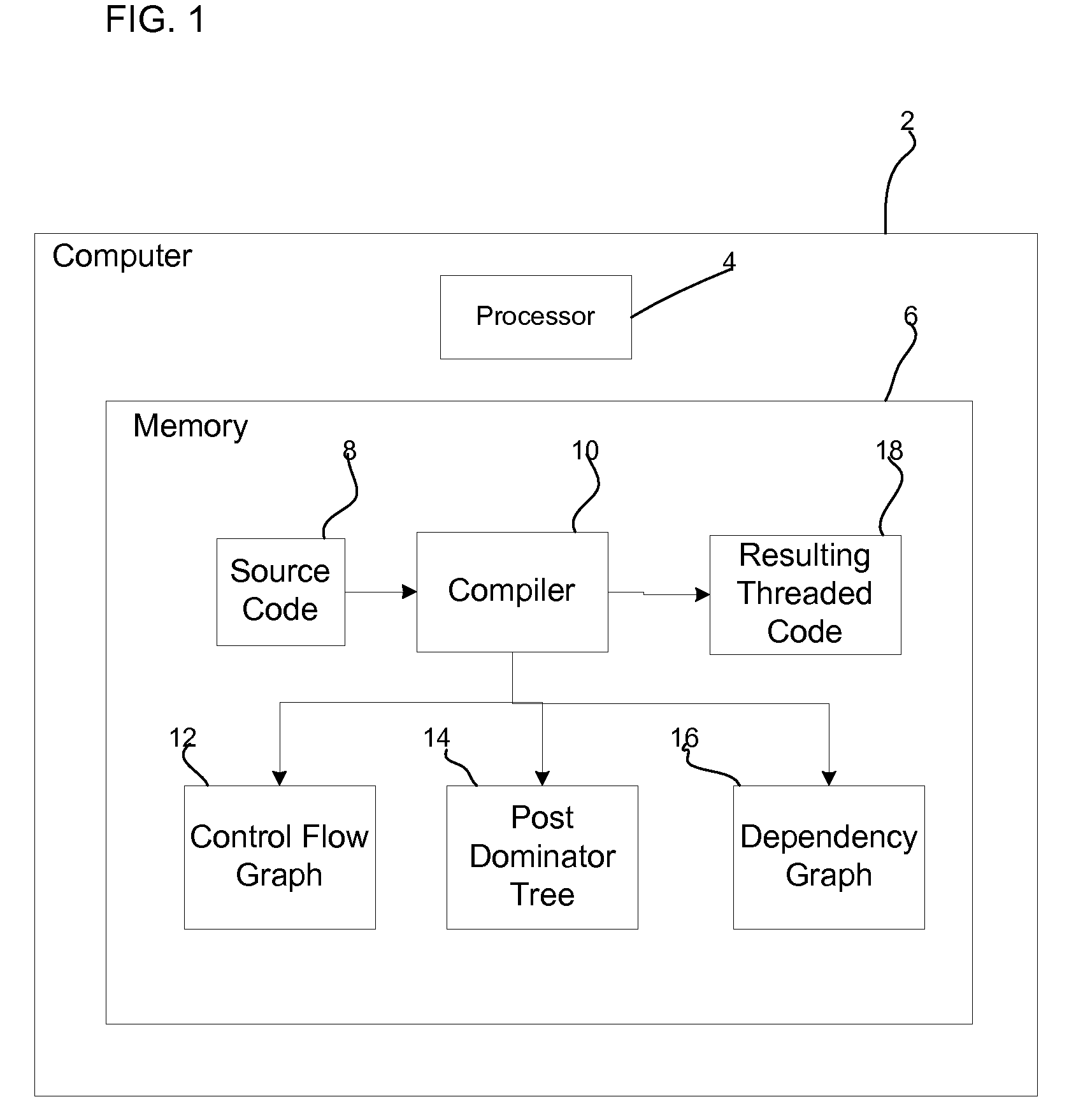

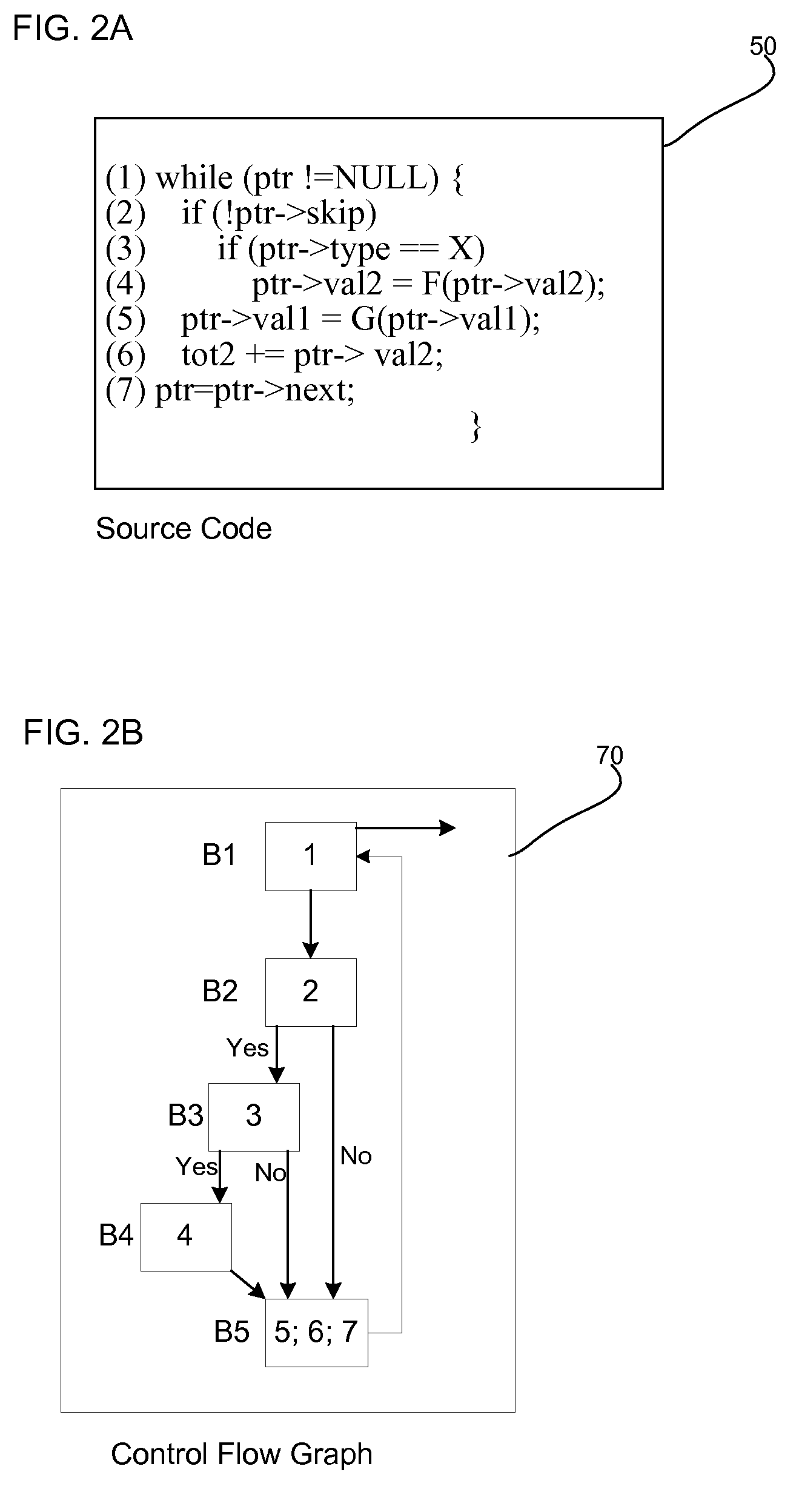

Method, system, and program of a compiler to parallelize source code

InactiveUS7882498B2Software engineeringSpecific program execution arrangementsSource codeThreaded code

Provided are a method, system, and program for parallelizing source code with a compiler. Source code including source code statements is received. The source code statements are processed to determine a dependency of the statements. Multiple groups of statements are determined from the determined dependency of the statements, wherein statements in one group are dependent on one another. At least one directive is inserted in the source code, wherein each directive is associated with one group of statements. Resulting threaded code is generated including the inserted at least one directive. The group of statements to which the directive in the resulting threaded code applies are processed as a separate task. Each group of statements designated by the directive to be processed as a separate task may be processed concurrently with respect to other groups of statements.

Owner:INTEL CORP

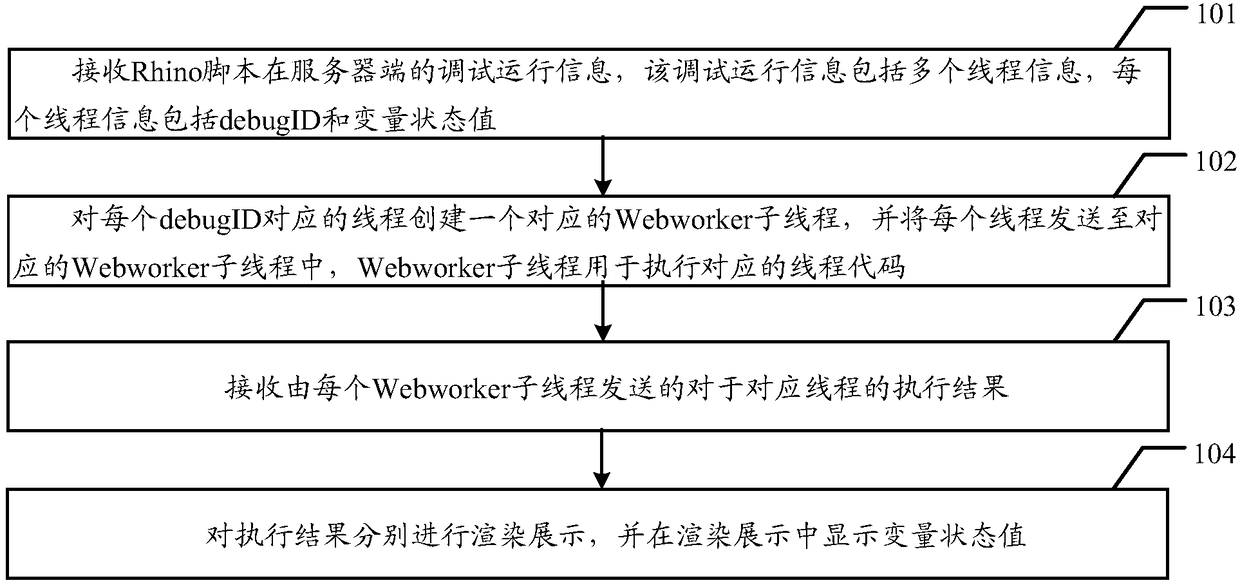

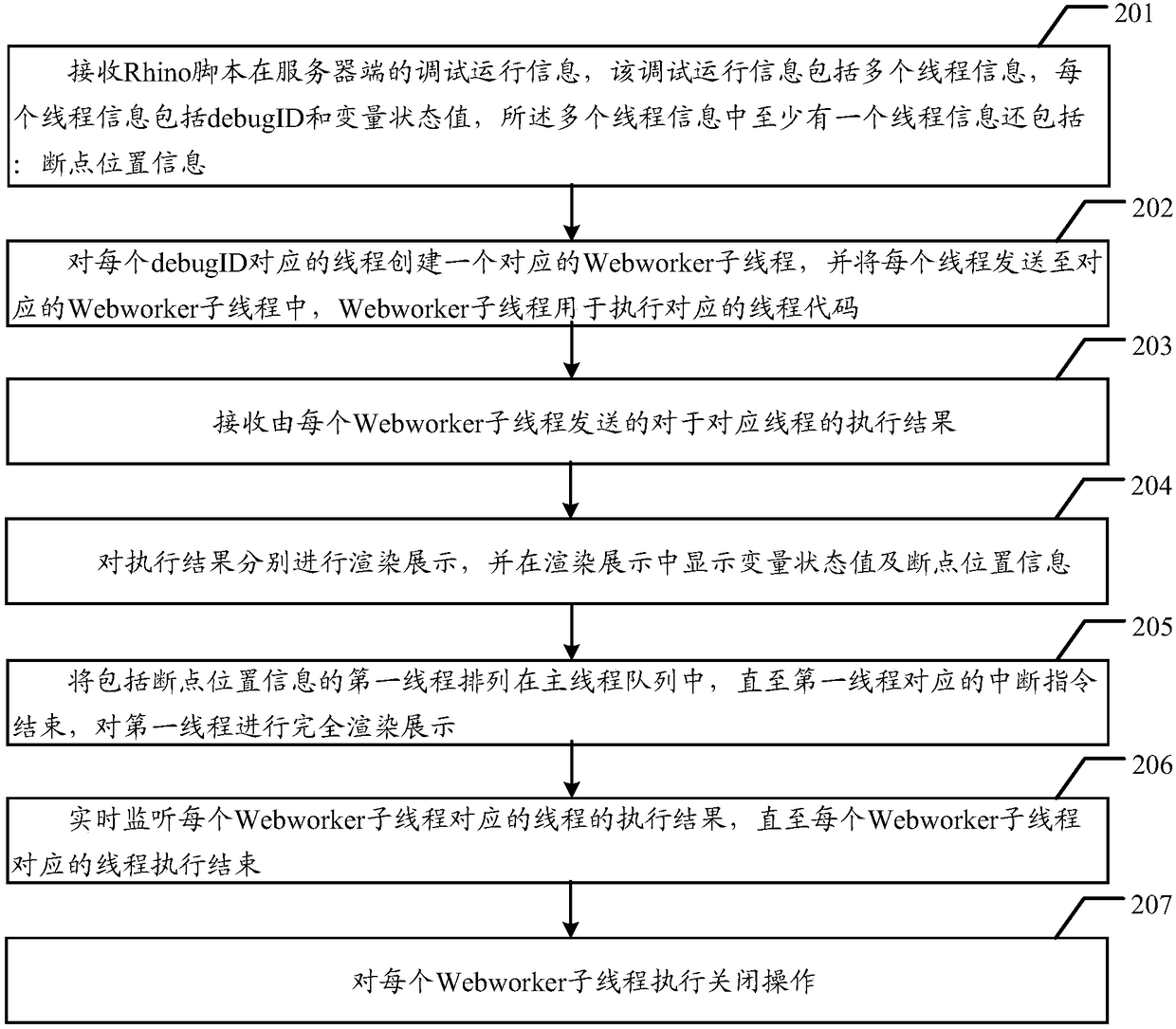

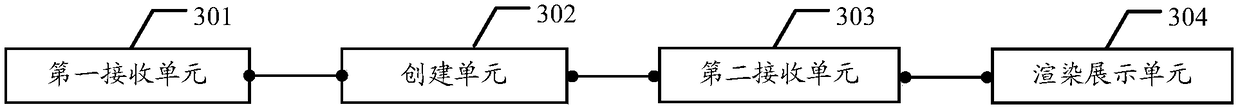

Concurrent debugging rendering method and device of script

ActiveCN108280027ASolve the blockageImplement concurrent debuggingSoftware testing/debuggingVisual/graphical programmingServer-sideThreaded code

The embodiment of the invention discloses a concurrent debugging rendering method and device of a script. The concurrent debugging rendering method and device are used for concurrently debugging and concurrently rendering multiple pages in the same integrated environment tab of WEB IDE. The method comprises the steps of receiving debugging running information of a Rhino script in a server side, wherein the debugging running information comprises multiple pieces of thread information, and each thread information comprises debug IDs and variable state values; creating a corresponding Webworker subsidiary thread for a thread corresponding to each debug ID, and sending each thread to the corresponding Webworker subsidiary thread, wherein each Webworker subsidiary thread is used for executing corresponding thread codes; receiving an executing result for the corresponding thread sent by each Webworker subsidiary thread; conducting rendering displaying on the executing results respectively, and displaying the variable state values in rendering displaying.

Owner:KINGDEE SOFTWARE(CHINA) CO LTD

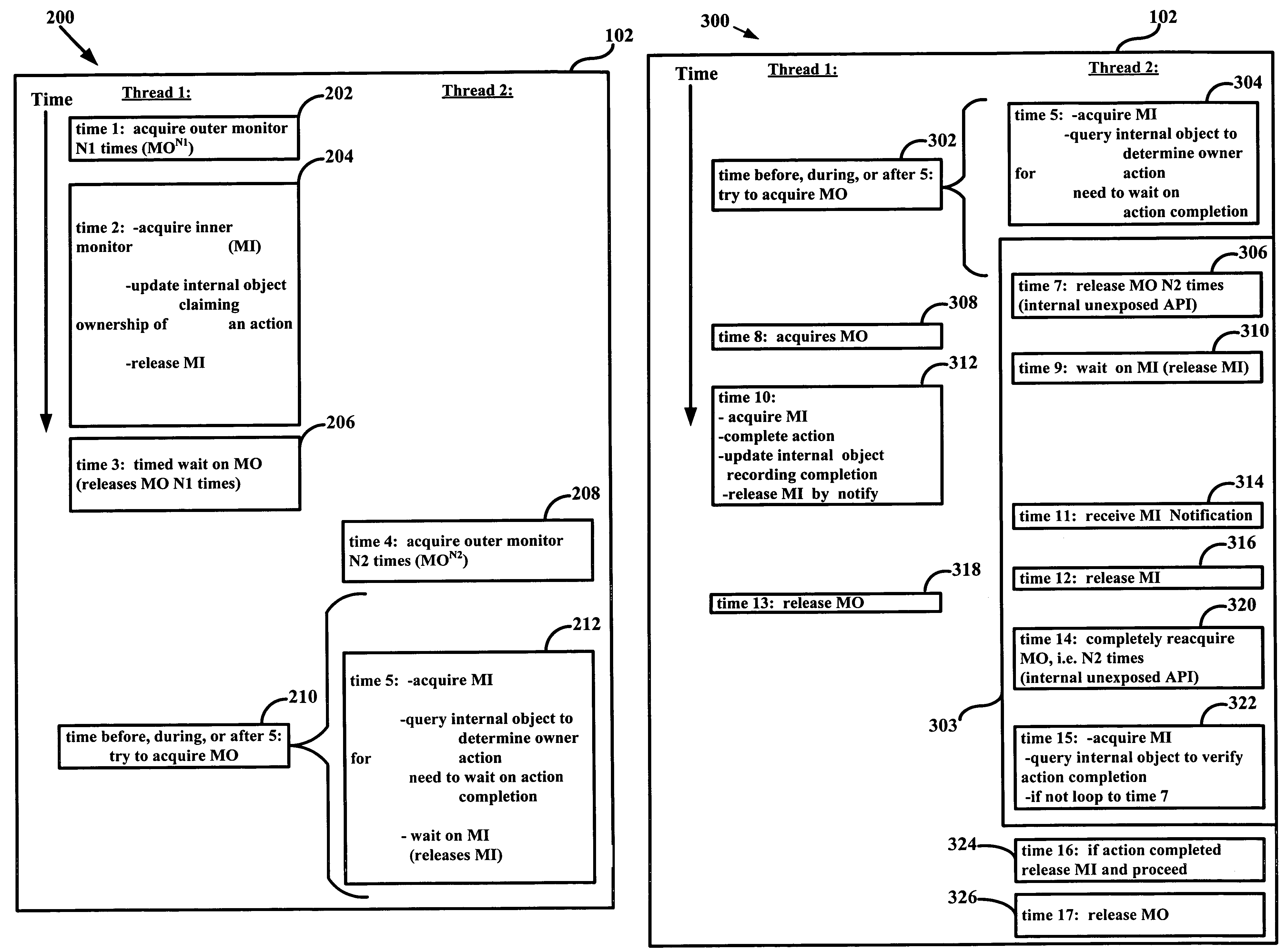

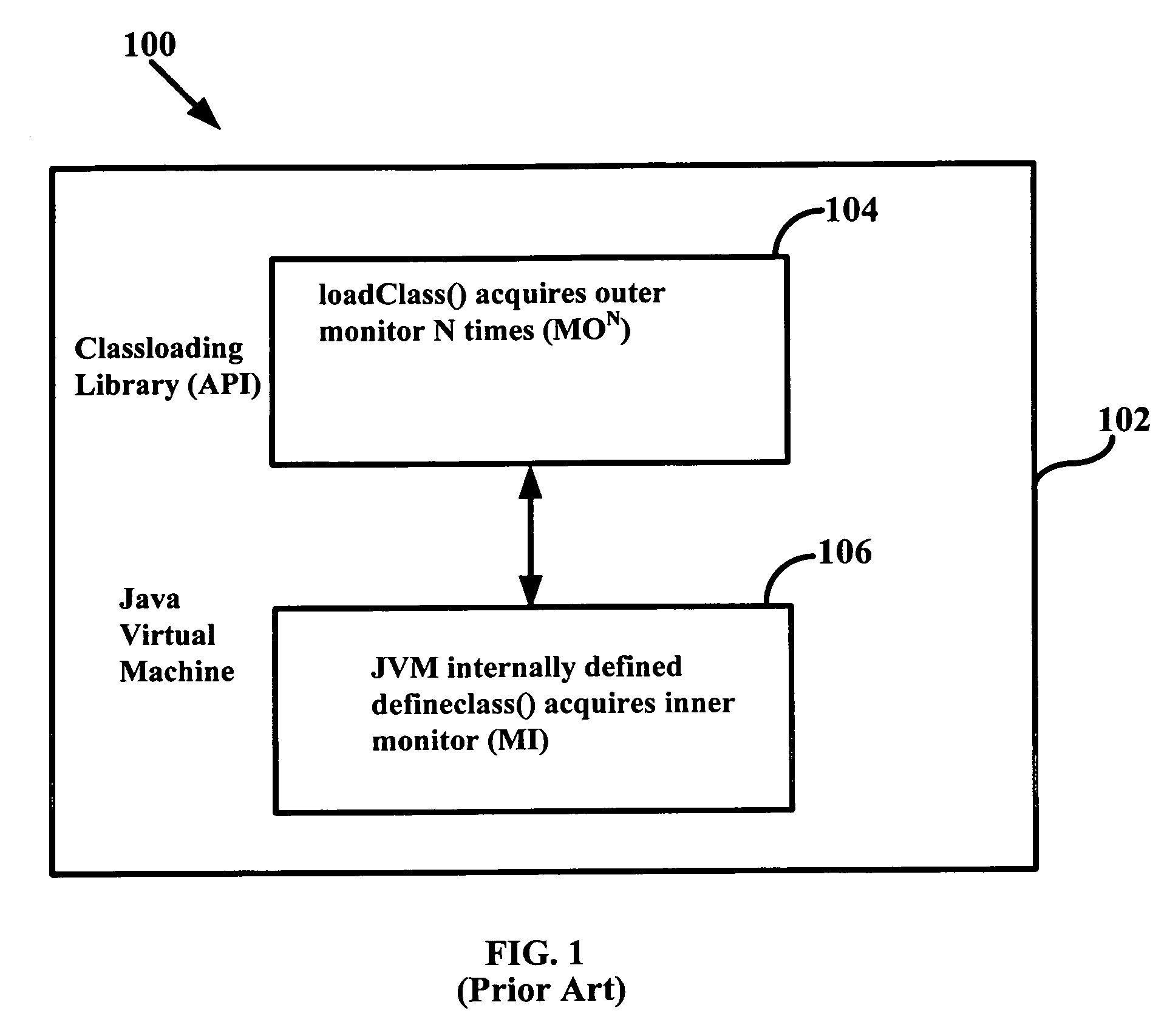

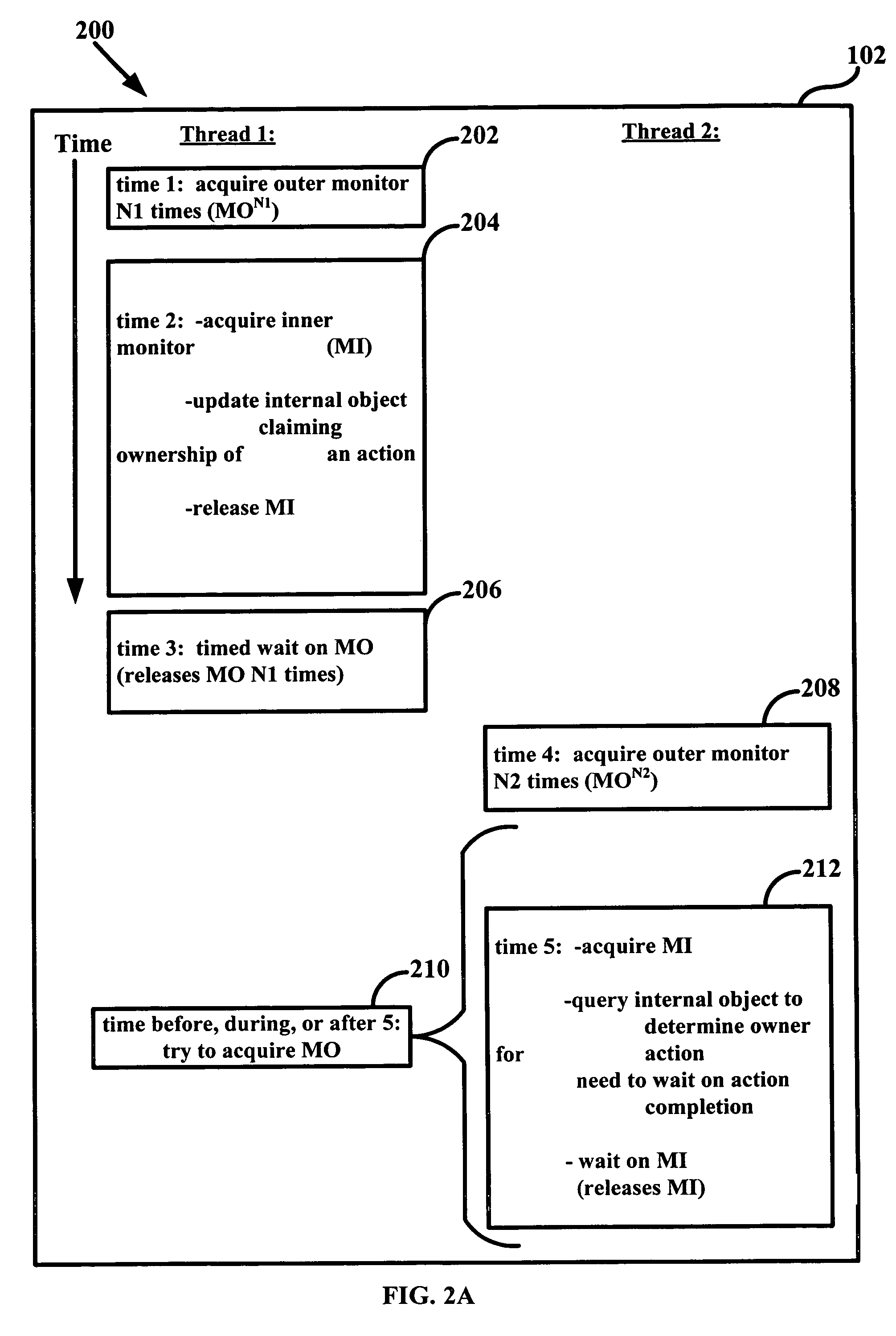

Nested monitor handling processes

ActiveUS7681197B1Digital data processing detailsUnauthorized memory use protectionApplication softwareSoftware modules

A method of managing nested monitor locks in a computer program is provided for an application having at least a first thread and a second thread wherein a non-synchronized procedure is processed by the application. The first thread executes an outer software module while the second thread executes an inner software module. A processing state of the second thread code is preserved before the second thread is configured to release an outer monitor of the outer software module. The first thread acquires the outer monitor of the outer software module so that actions may be completed. Upon completion of actions by the first thread, the outer monitor of the outer software module is released. The processing state of the second thread is restored, such that, actions of the second thread are allowed to be completed.

Owner:ORACLE INT CORP

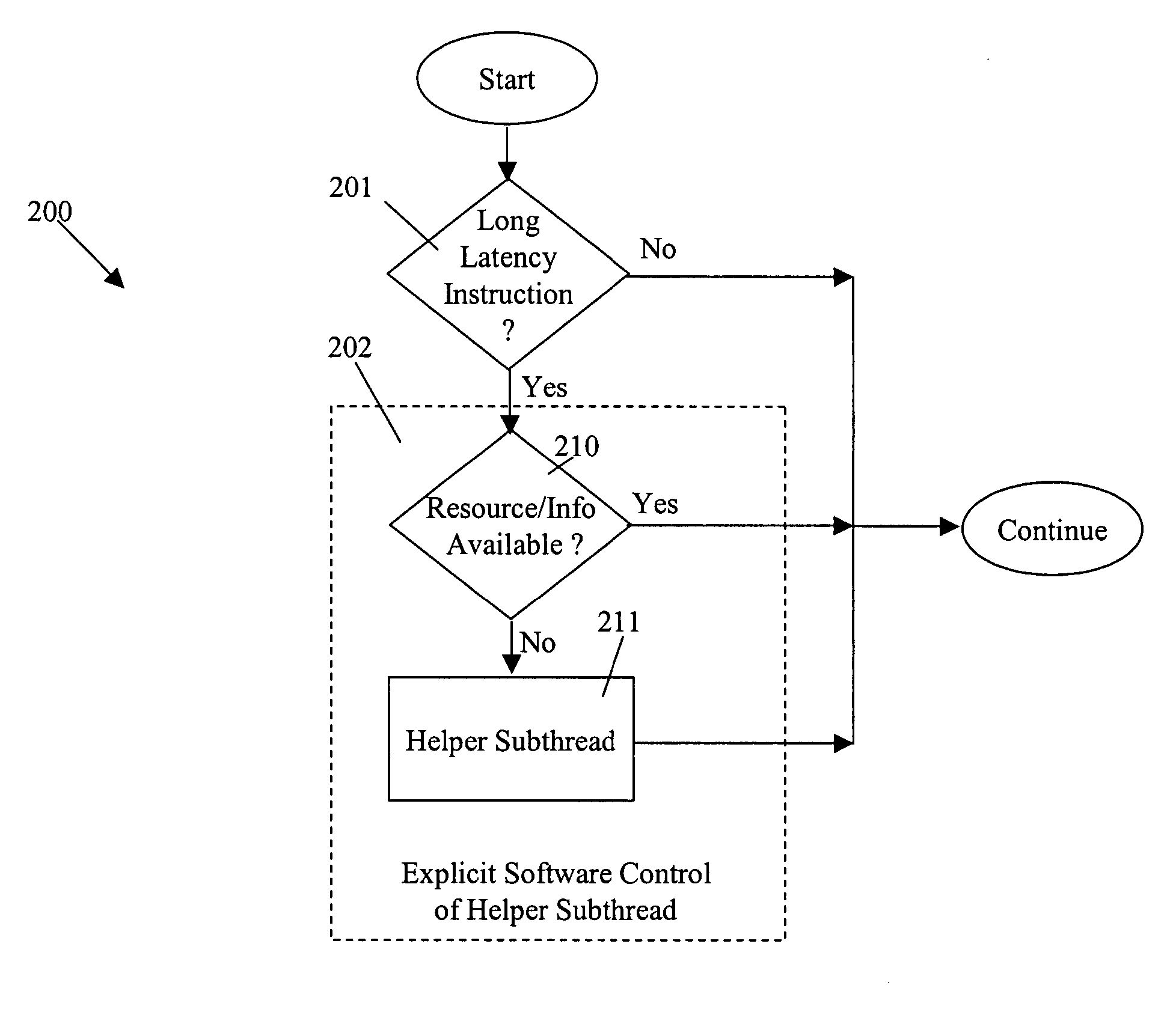

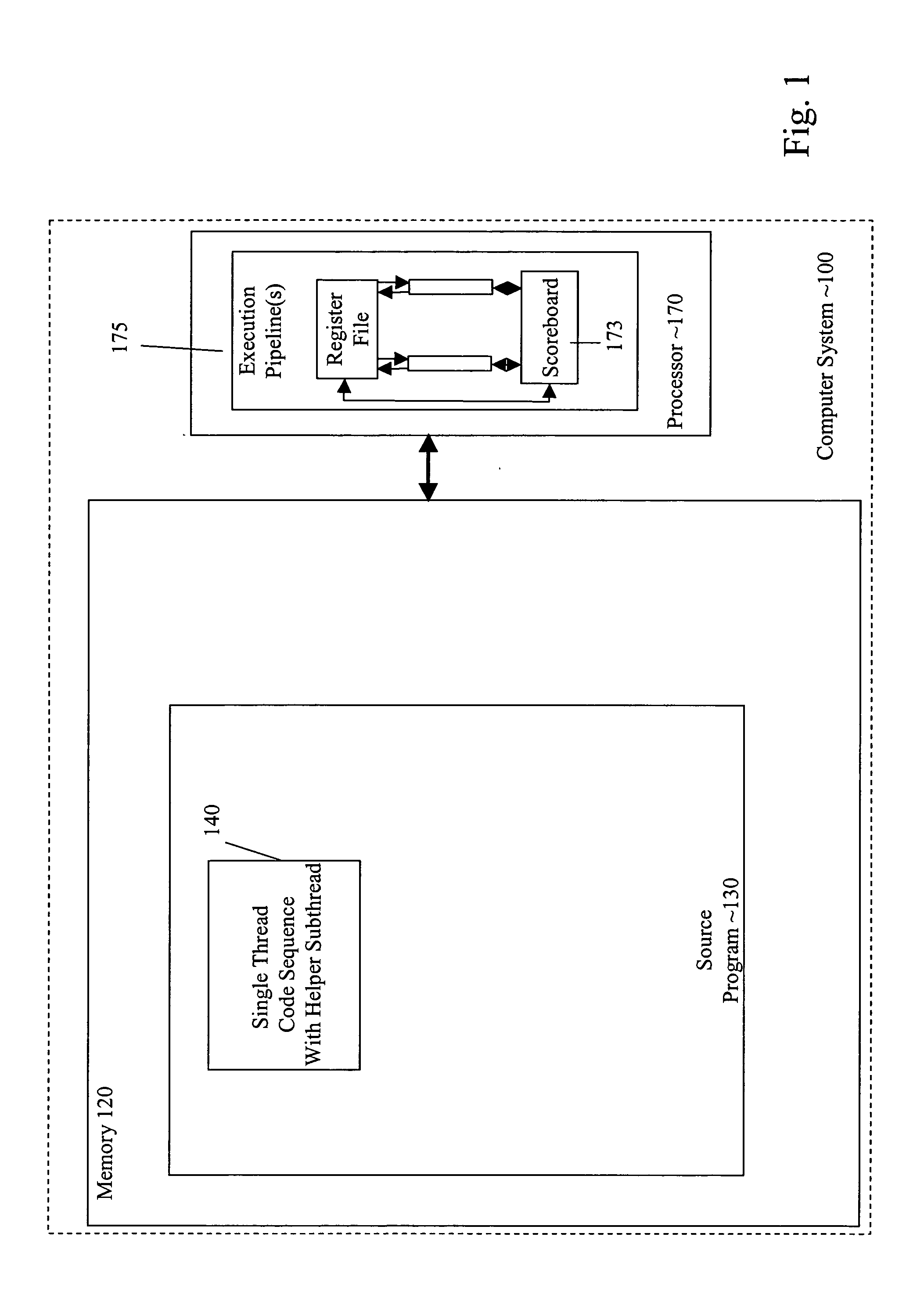

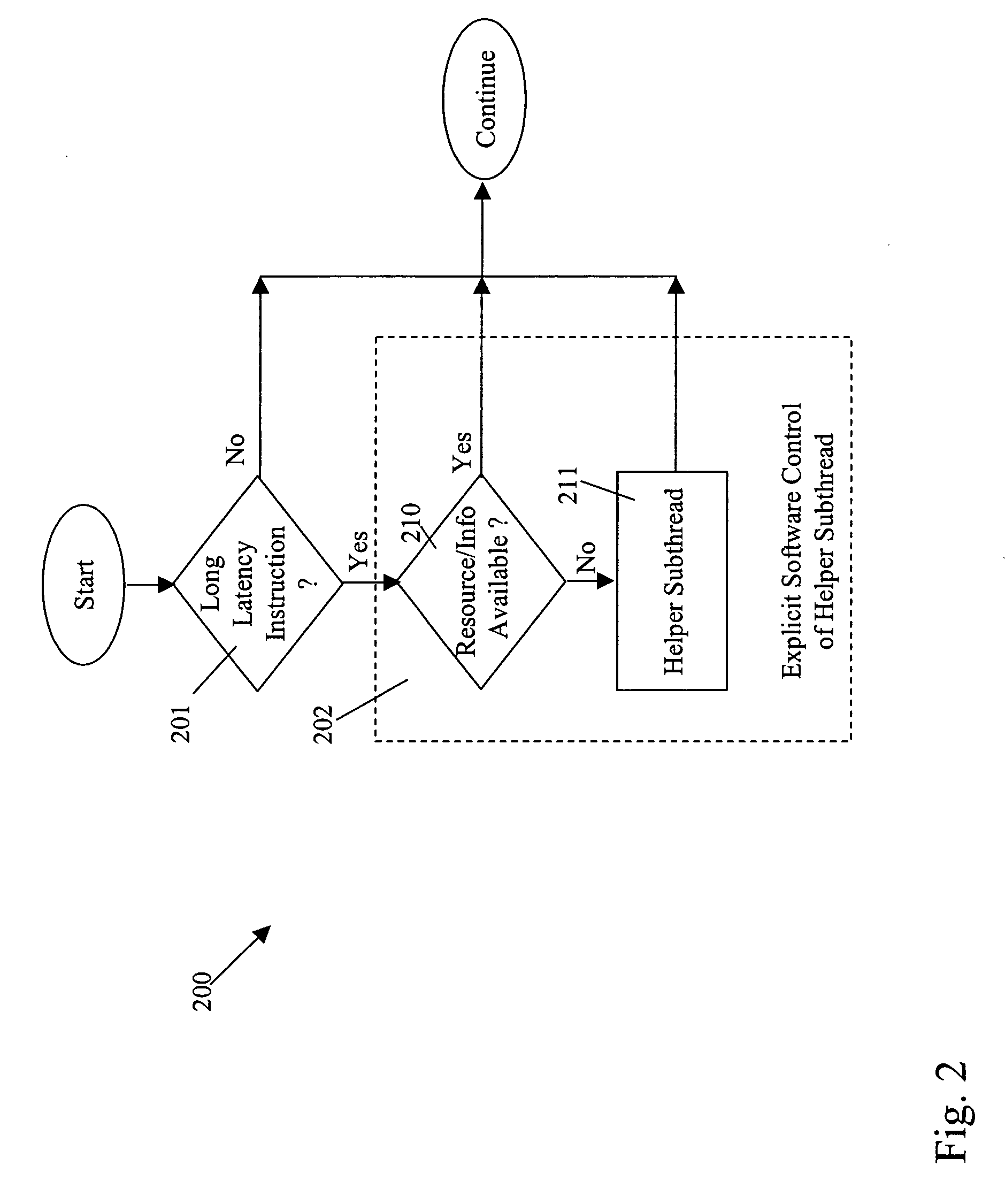

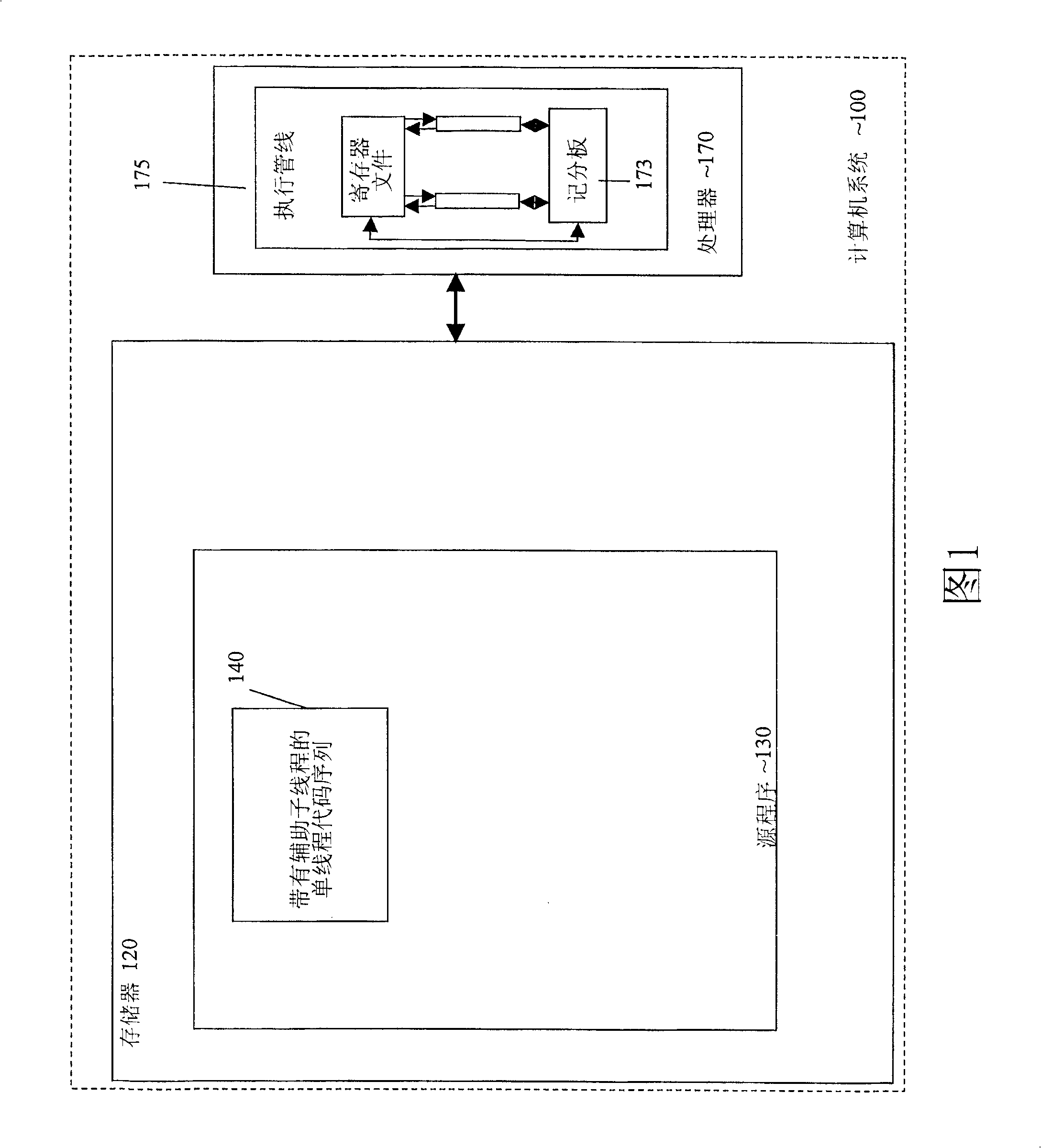

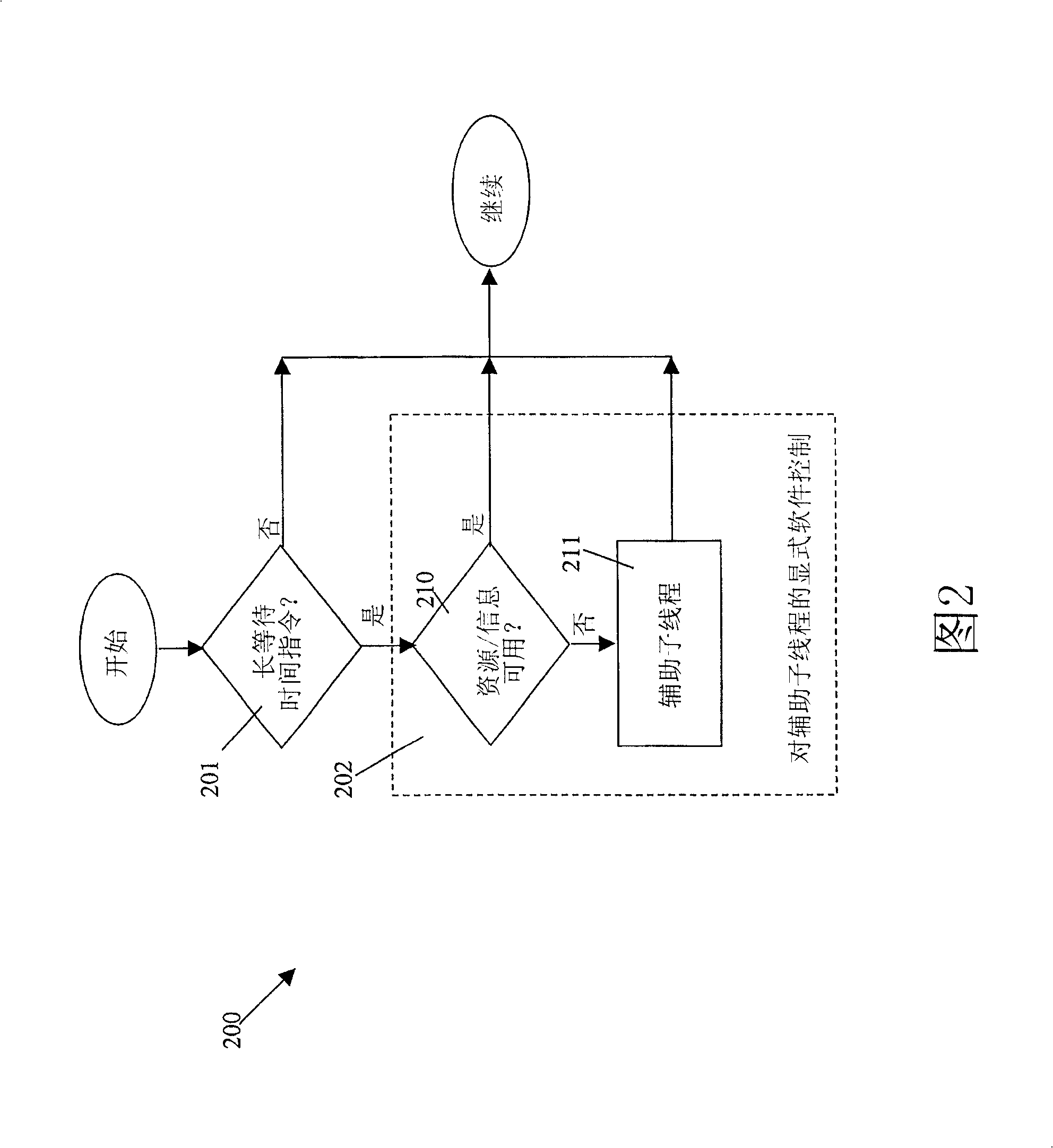

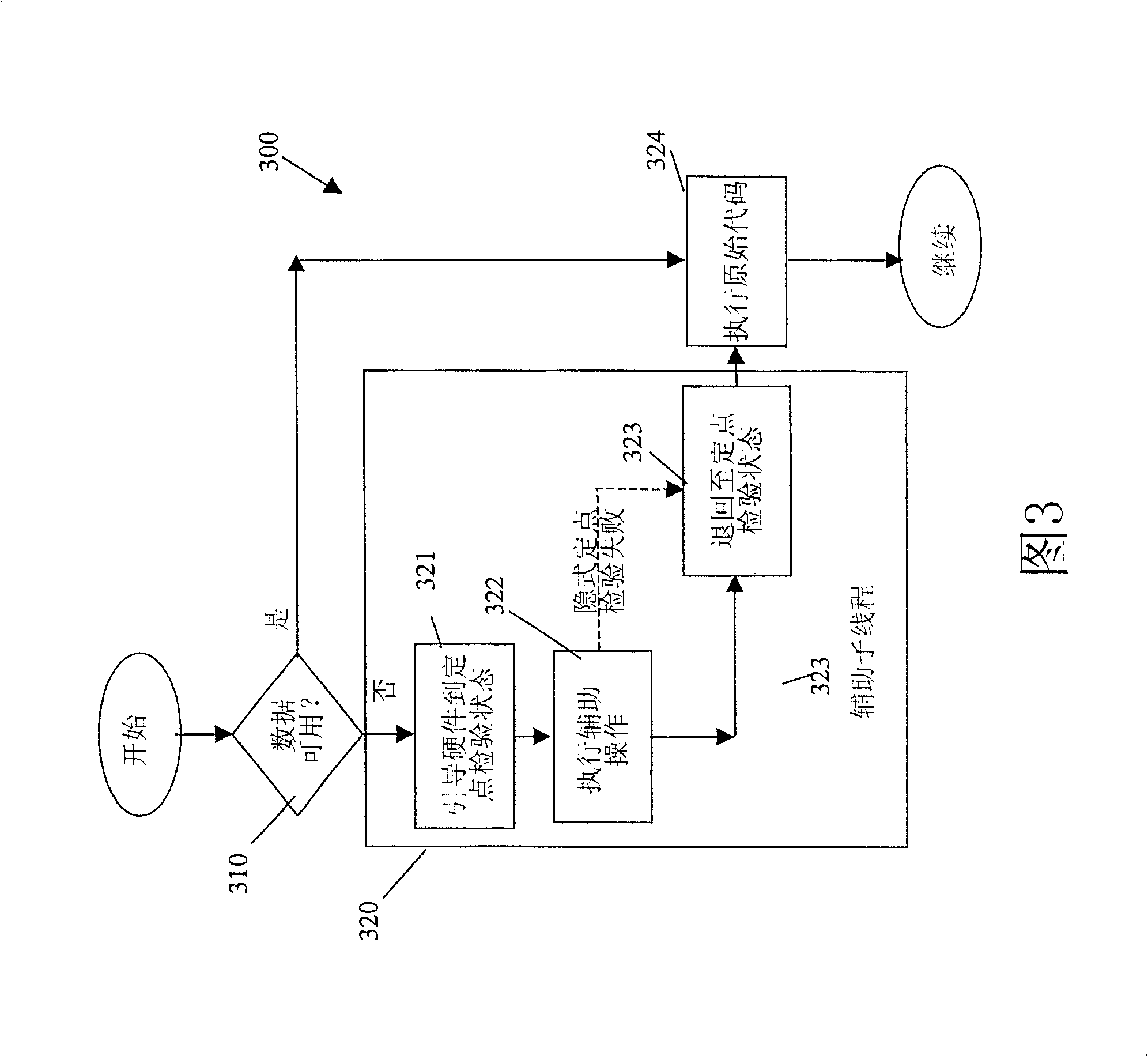

Method and structure for explicit software control of execution of a thread including a helper subthread

InactiveUS20050223385A1General purpose stored program computerMemory systemsLong latencyProgram instruction

Software instructions in a single thread code sequence with a helper subthread are executed on a processor of a computer system. The execution causes the computer system, for example, to (i) determine whether information associated with a long latency instruction is available, and when the data is unavailable, to (ii) snapshot a state of the computer system and maintain a capability to roll back to that snapshot state, (iii) execute the helper instruction in the helper subthread, and (iv) roll back to the snapshot state upon completion of execution of the helper instructions in the helper subthread and continue execution. The helper subthread, for example prefetches data while waiting for the long latency instruction to complete.

Owner:SUN MICROSYSTEMS INC

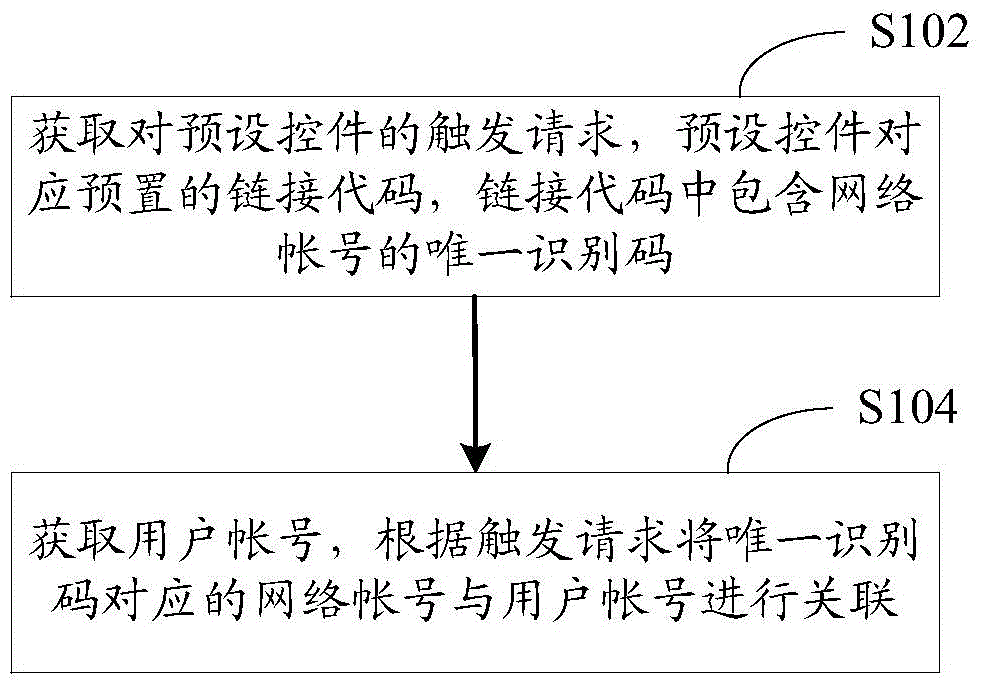

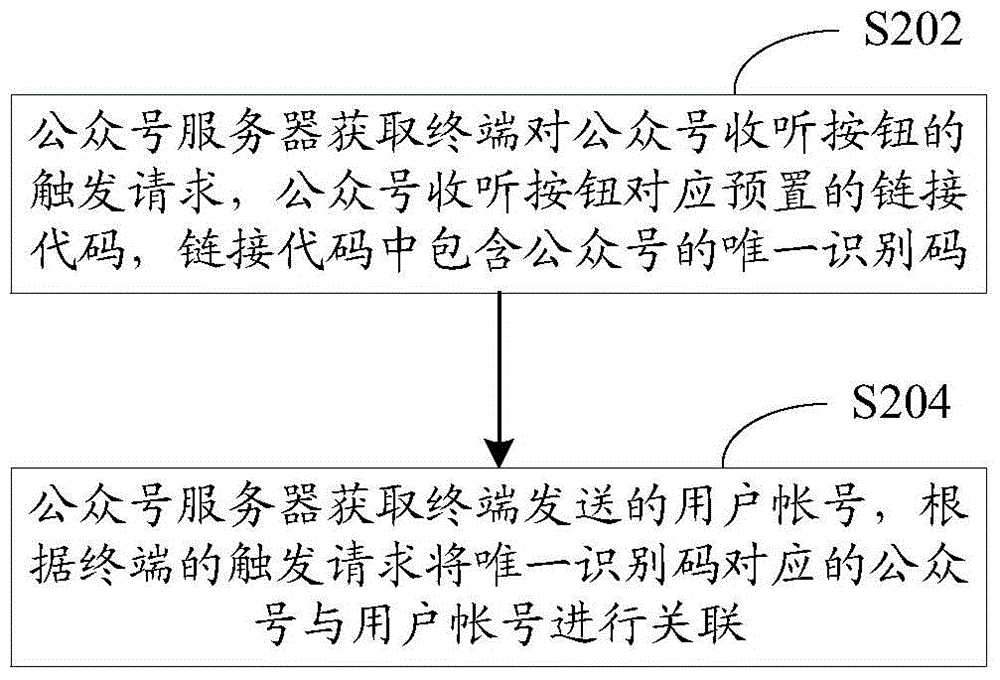

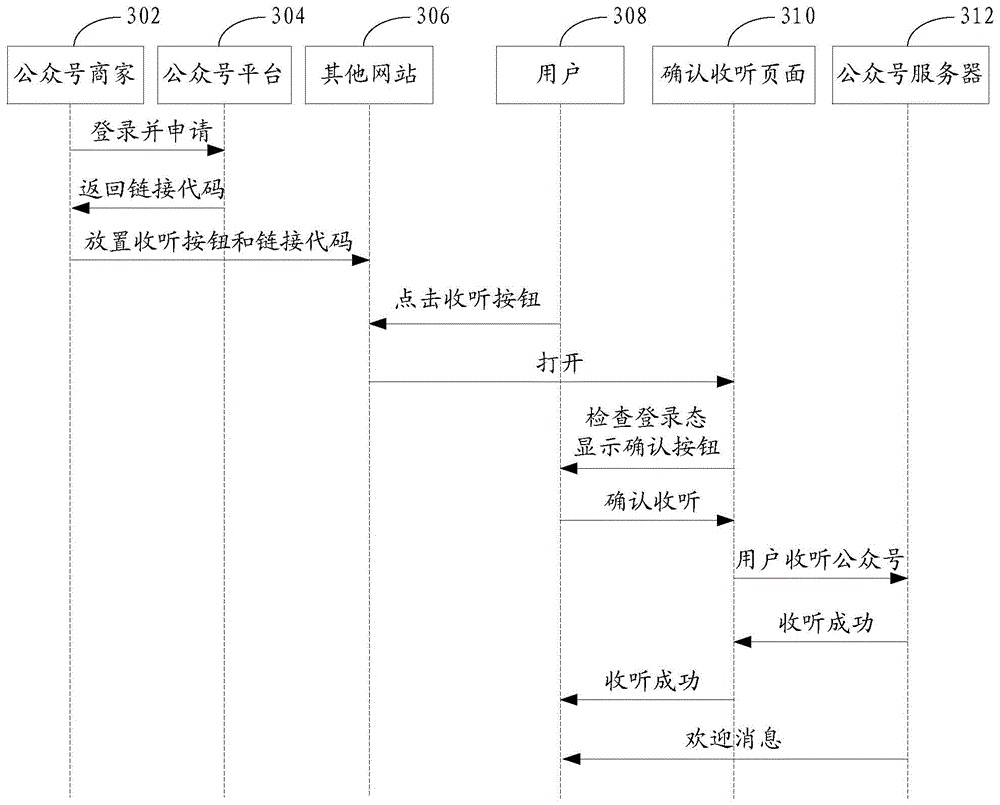

Method and system for associating network account

The invention provides a method for associating a network account. The method comprises the following steps of acquiring a triggering request on an interface element corresponding to a preset threaded code which comprises a unique identification code of the network account; acquiring a user account; and associating the network account corresponding to the unique identification code to the user account according to the triggering request. In addition, the invention also provides a system for associating the network account and a method and a system for associating a public number. By the method for associating the network account, the network account associating efficiency can be improved effectively.

Owner:TENCENT TECH (SHENZHEN) CO LTD

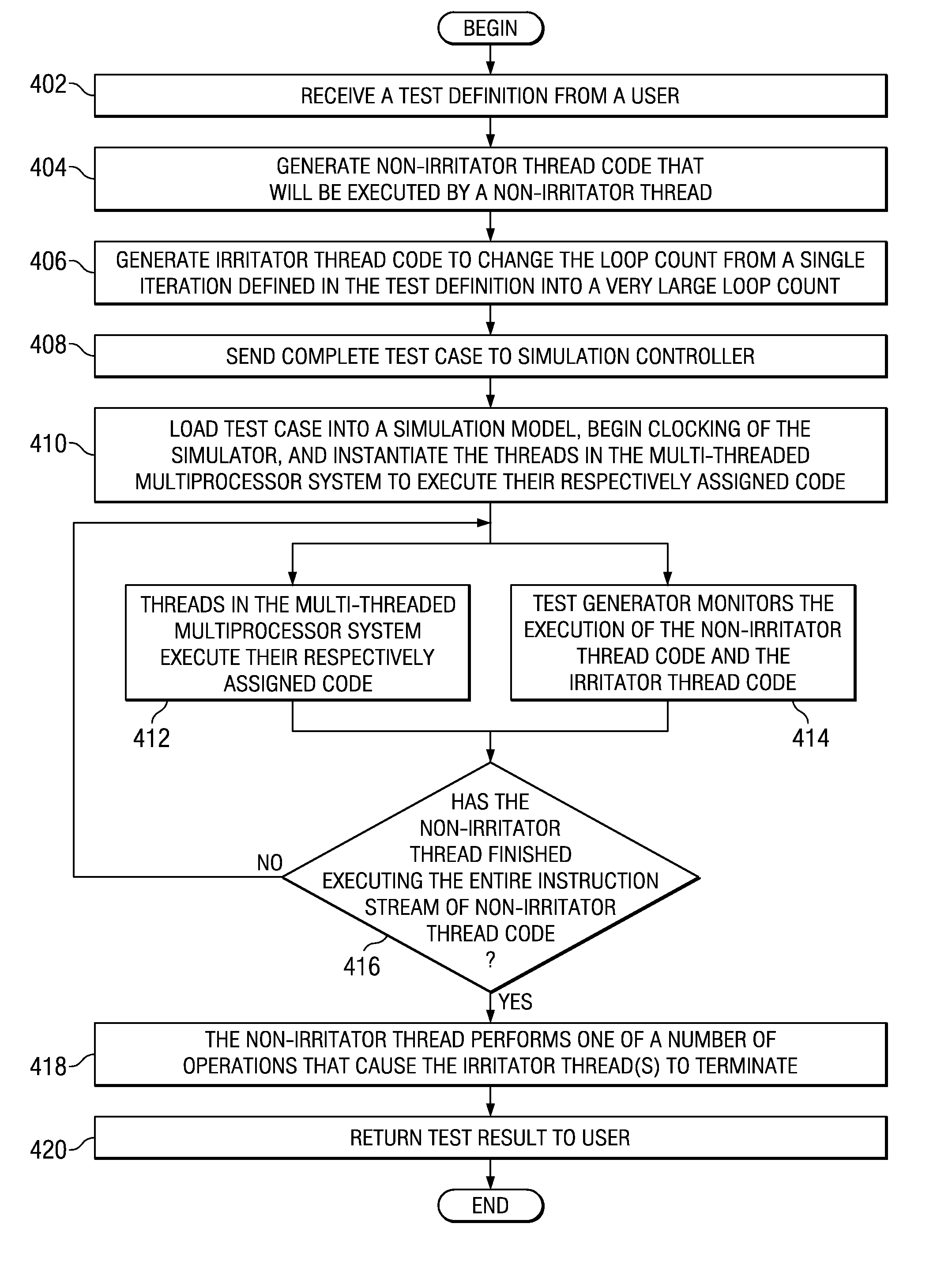

Efficient and self-balancing verification of multi-threaded microprocessors

ActiveUS8479173B2Error detection/correctionSpecific program execution arrangementsData processing systemIrritator

Owner:INT BUSINESS MASCH CORP

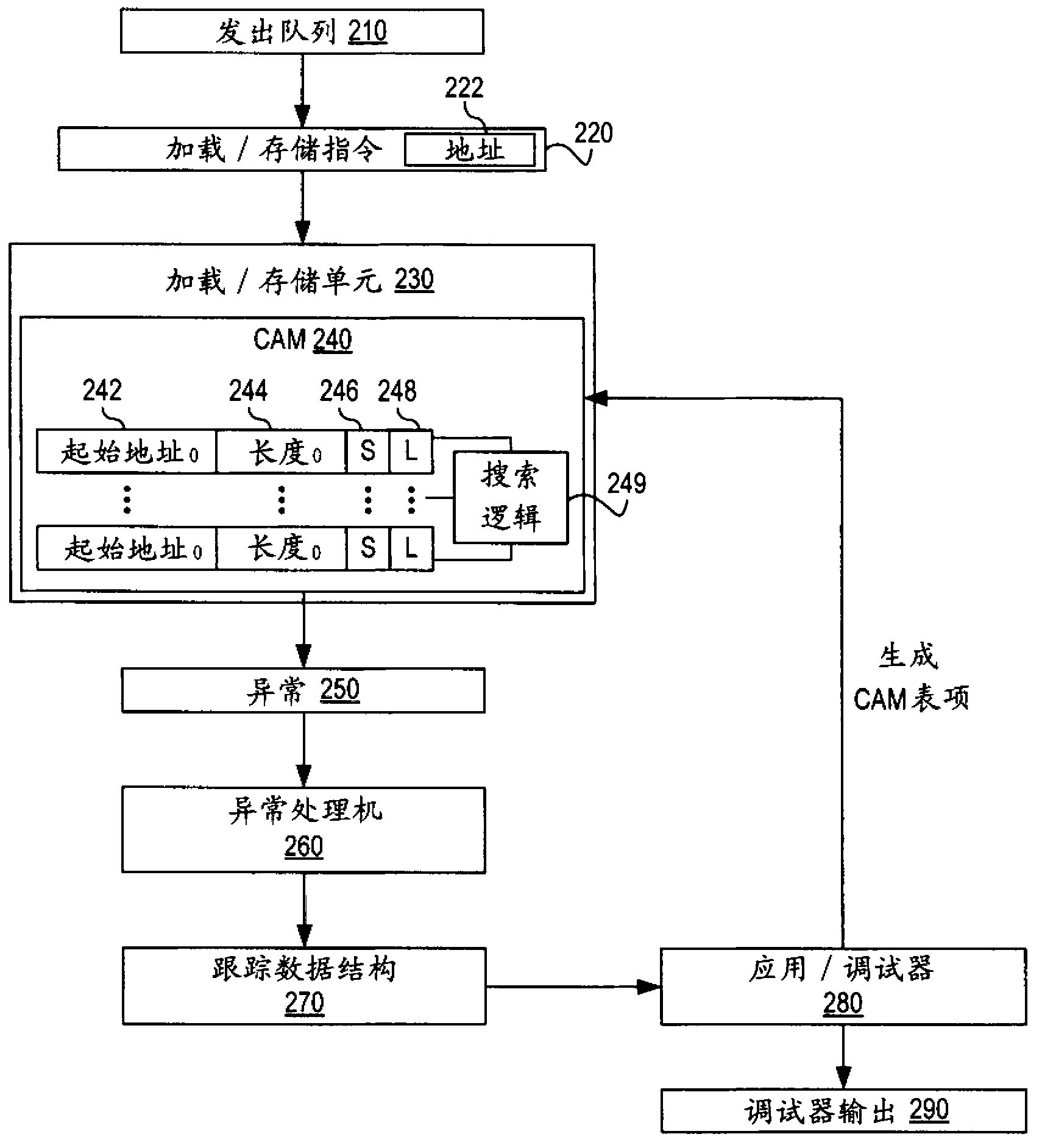

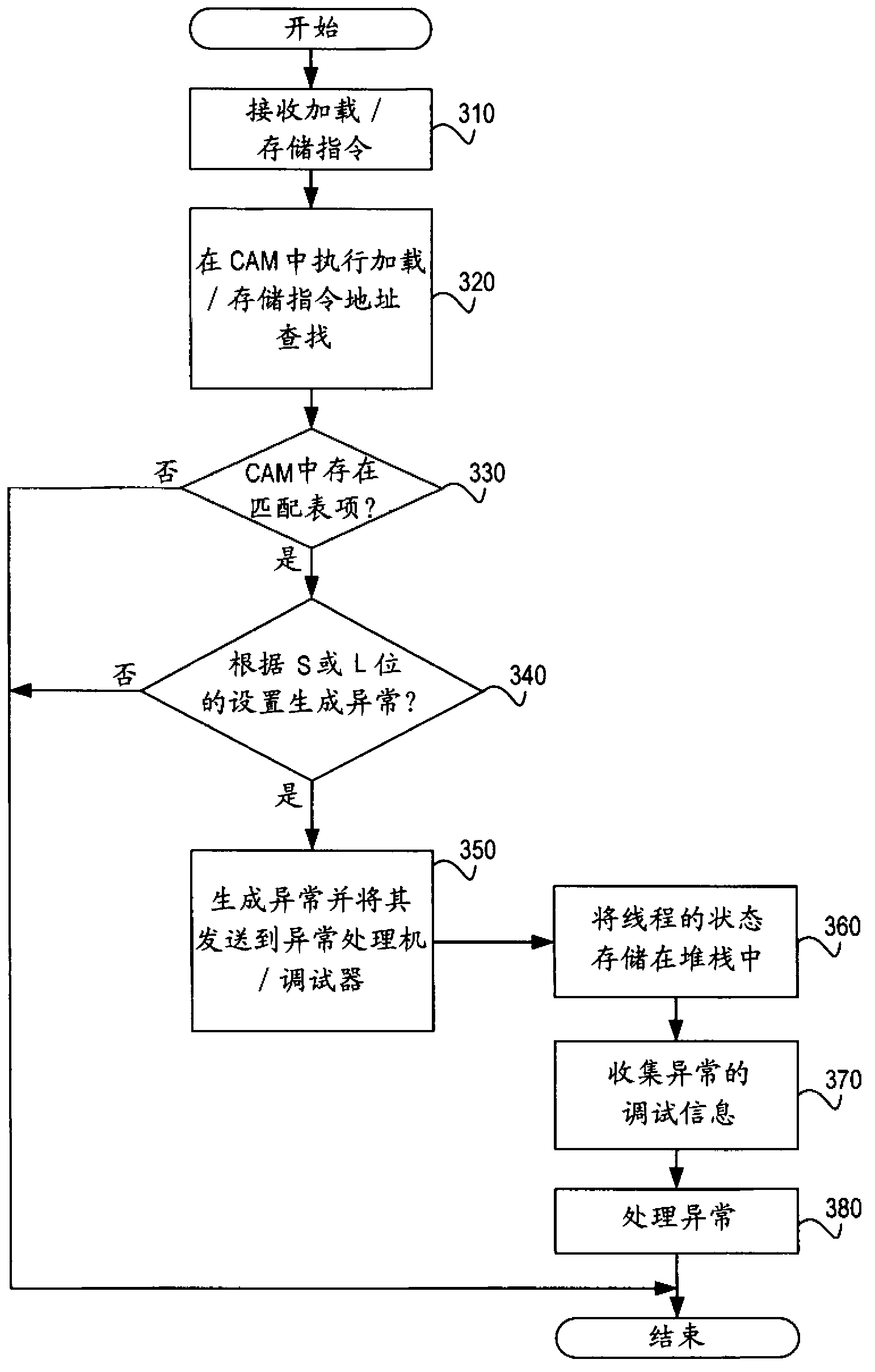

Debugging multithreaded code

Mechanisms are provided for debugging application code using a content addressable memory. The mechanisms receive an instruction in a hardware unit of a processor of the data processing system, the instruction having a target memory address that the instruction is attempting to access. A content addressable memory (CAM) associated with the hardware unit is searched for an entry in the CAM corresponding to the target memory address. In response to an entry in the CAM corresponding to the target memory address being found, a determination is made as to whether information in the entry identifies the instruction as an instruction of interest. In response to the entry identifying the instruction as an instruction of interest, an exception is generated and sent to one of an exception handler or a debugger application. In this way, debugging of multithreaded applications may be performed in an efficient manner.

Owner:IBM CORP

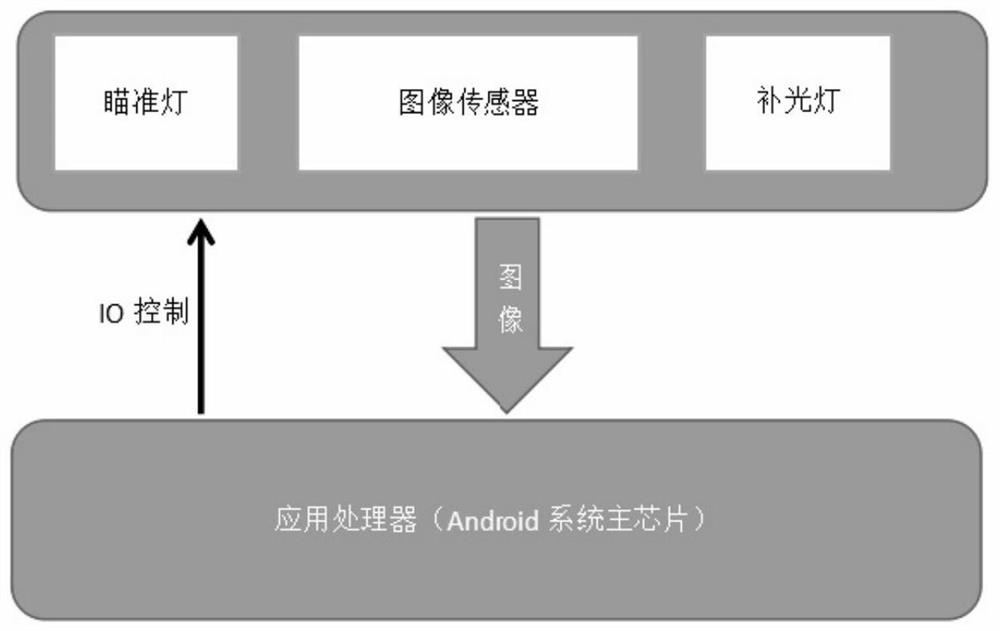

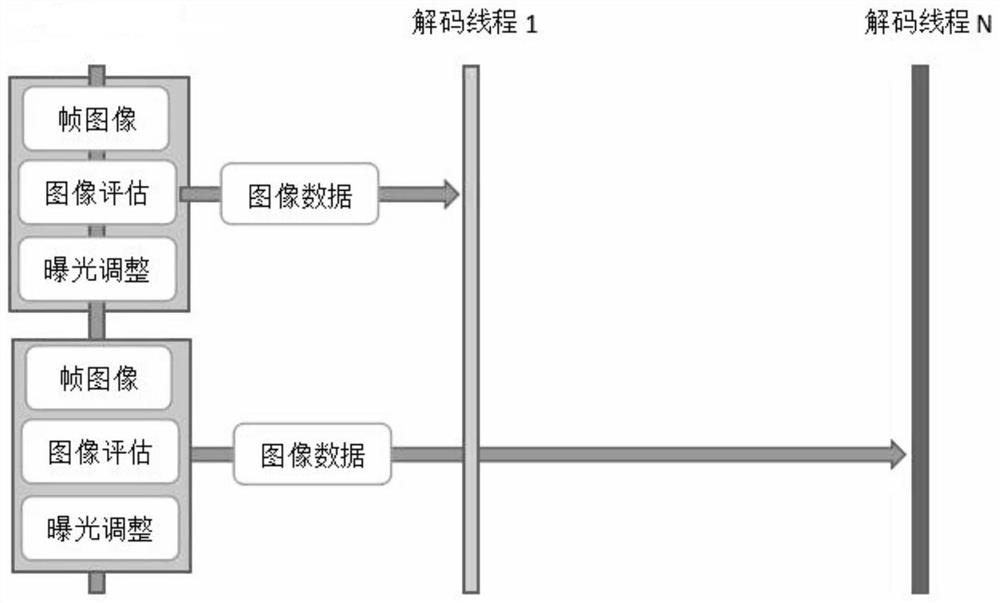

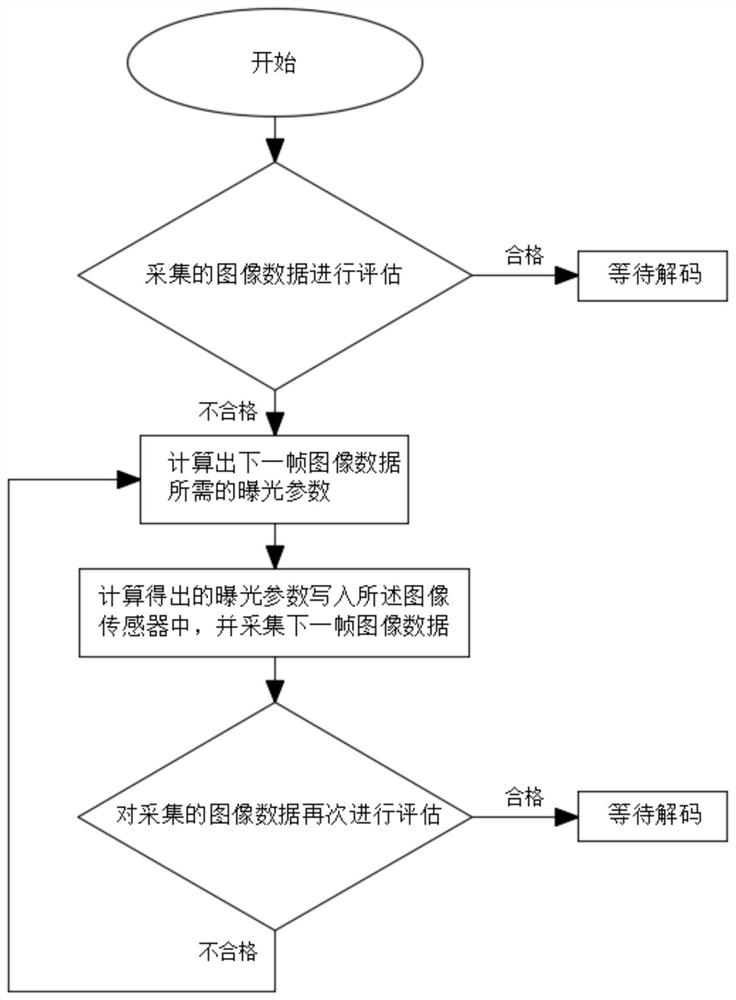

Android system-based multi-thread code scanning processing method for code scanning head module

PendingCN111881698AImprove decoding efficiencyTake advantage ofMultiprogramming arrangementsLogisticsElectronic informationEmbedded system

The invention relates to the technical field of electronic information communication, in particular to an Android system-based multi-thread code scanning processing method for a code scanning head module, which comprises an application processor, a sighting lamp, an image sensor and a light supplementing lamp, wherein the code scanning head module is driven by the application processor and the image sensor; the sighting lamp and the light supplementing lamp are controlled through the application processor and the image sensor, and the application processor is used for receiving image data output by the image sensor through multi-thread processing. According to the invention, multi-thread code scanning processing of the image sensor is achieved through the application processor, the decoding efficiency of the code scanning head module is improved, the built-in application processor of the Android system replaces a controller in the code scanning head module, the cost is reduced, and theoperation efficiency is higher; the performance is fully utilized, and the use is convenient.

Owner:上海祥承通讯技术有限公司

Method and apparatus for efficient helper thread state initialization using inter-thread register copy

This disclosure describes a method and system that may enable fast, hardware-assisted, producer-consumer style communication of values between threads. The method, in one aspect, uses a dedicated hardware buffer as an intermediary storage for transferring values from registers in one thread to registers in another thread. The method may provide a generic, programmable solution that can transfer any subset of register values between threads in any given order, where the source and target registers may or may not be correlated. The method also may allow for determinate access times, since it completely bypasses the memory hierarchy. Also, the method is designed to be lightweight, focusing on communication, and keeping synchronization facilities orthogonal to the communication mechanism. It may be used by a helper thread that performs data prefetching for an application thread, for example, to initialize the upward-exposed reads in the address computation slice of the helper thread code.

Owner:INT BUSINESS MASCH CORP

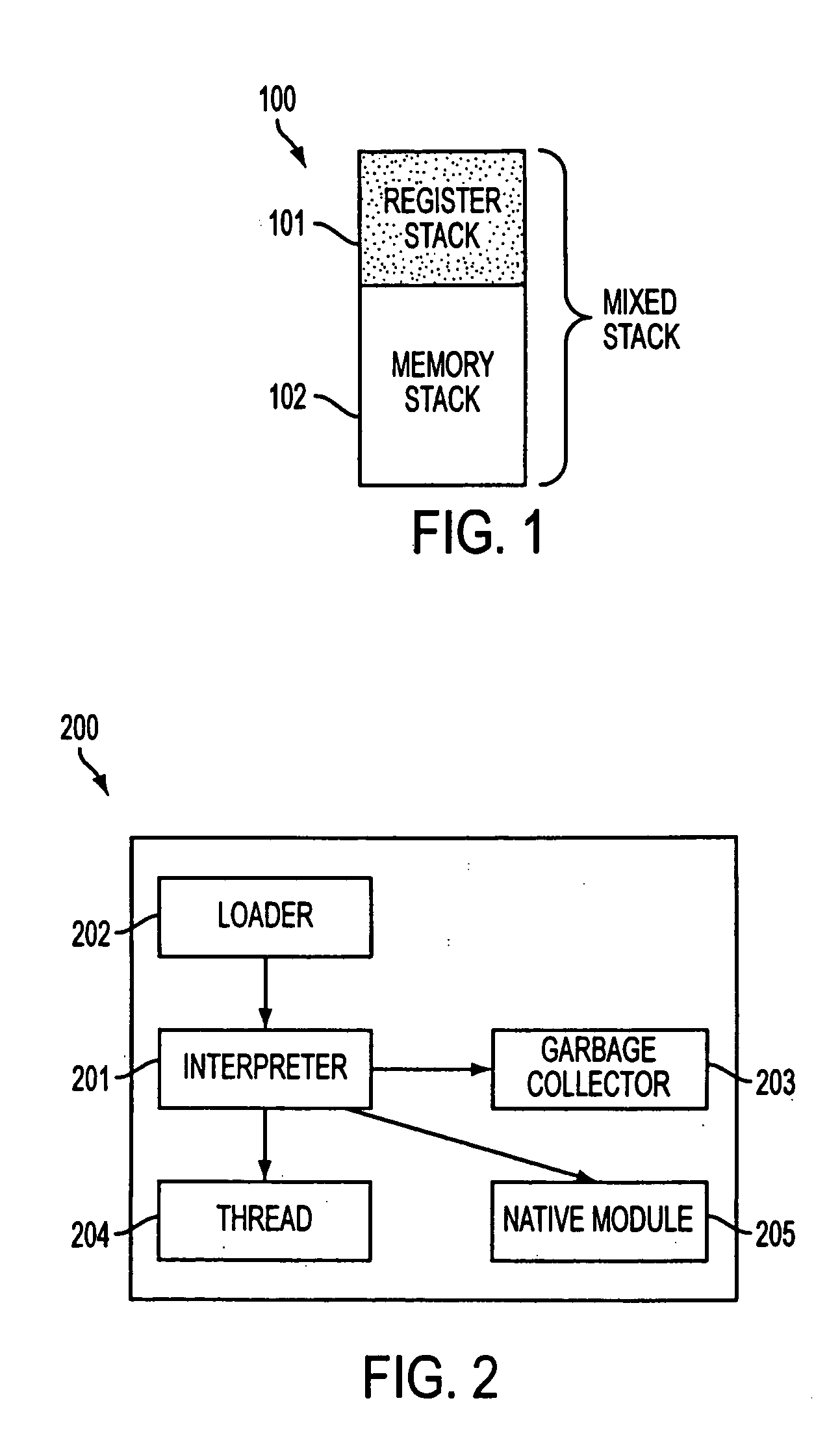

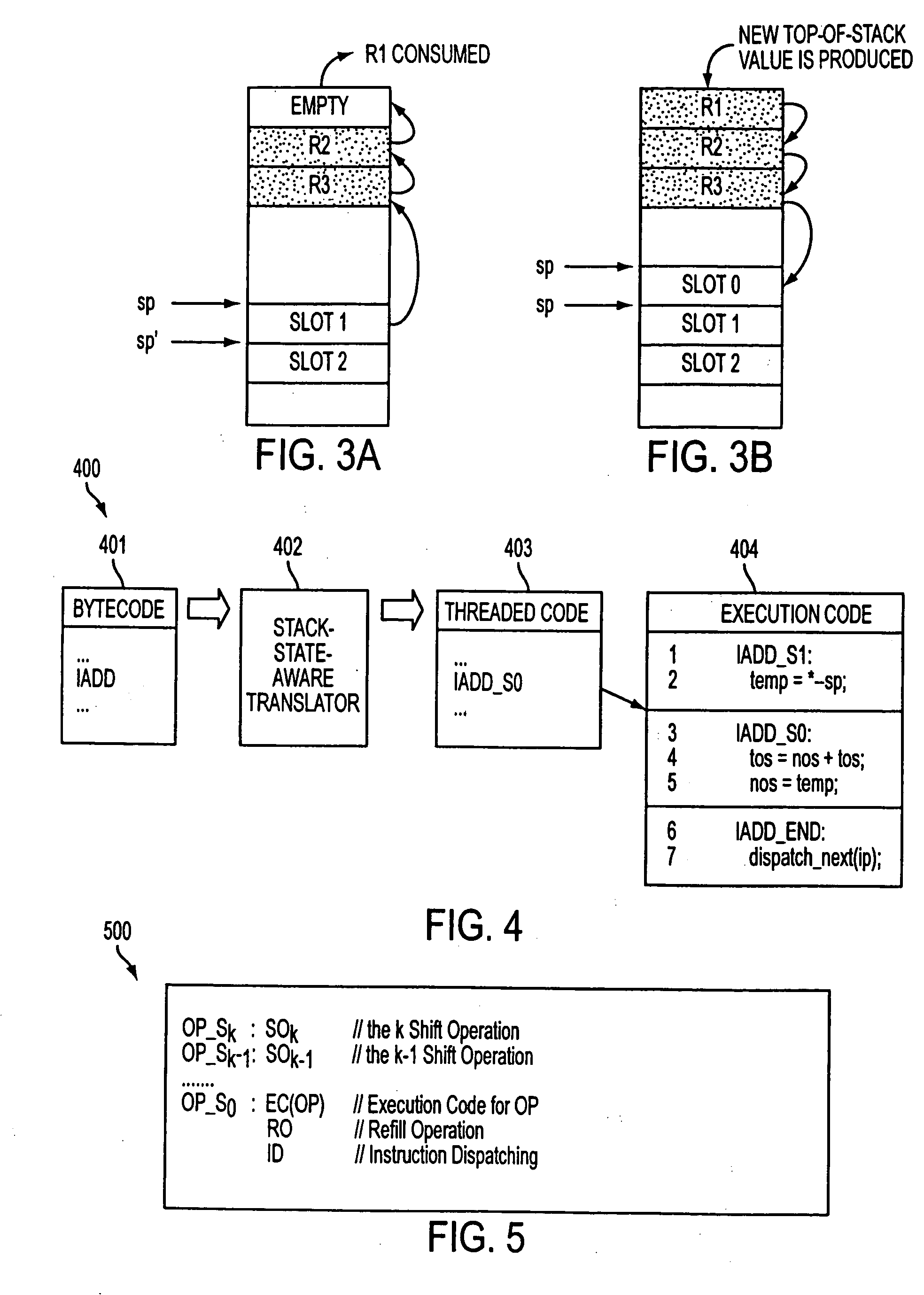

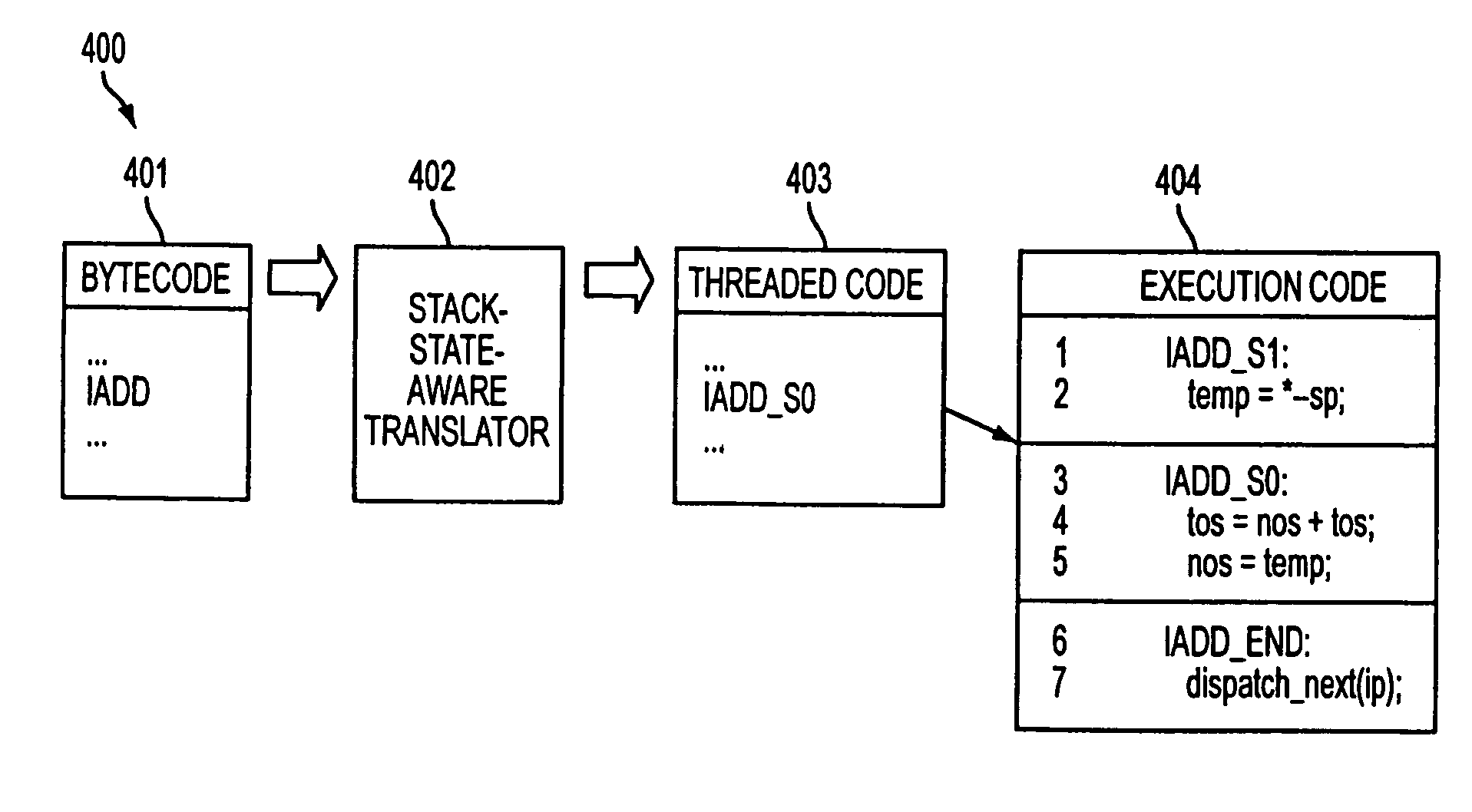

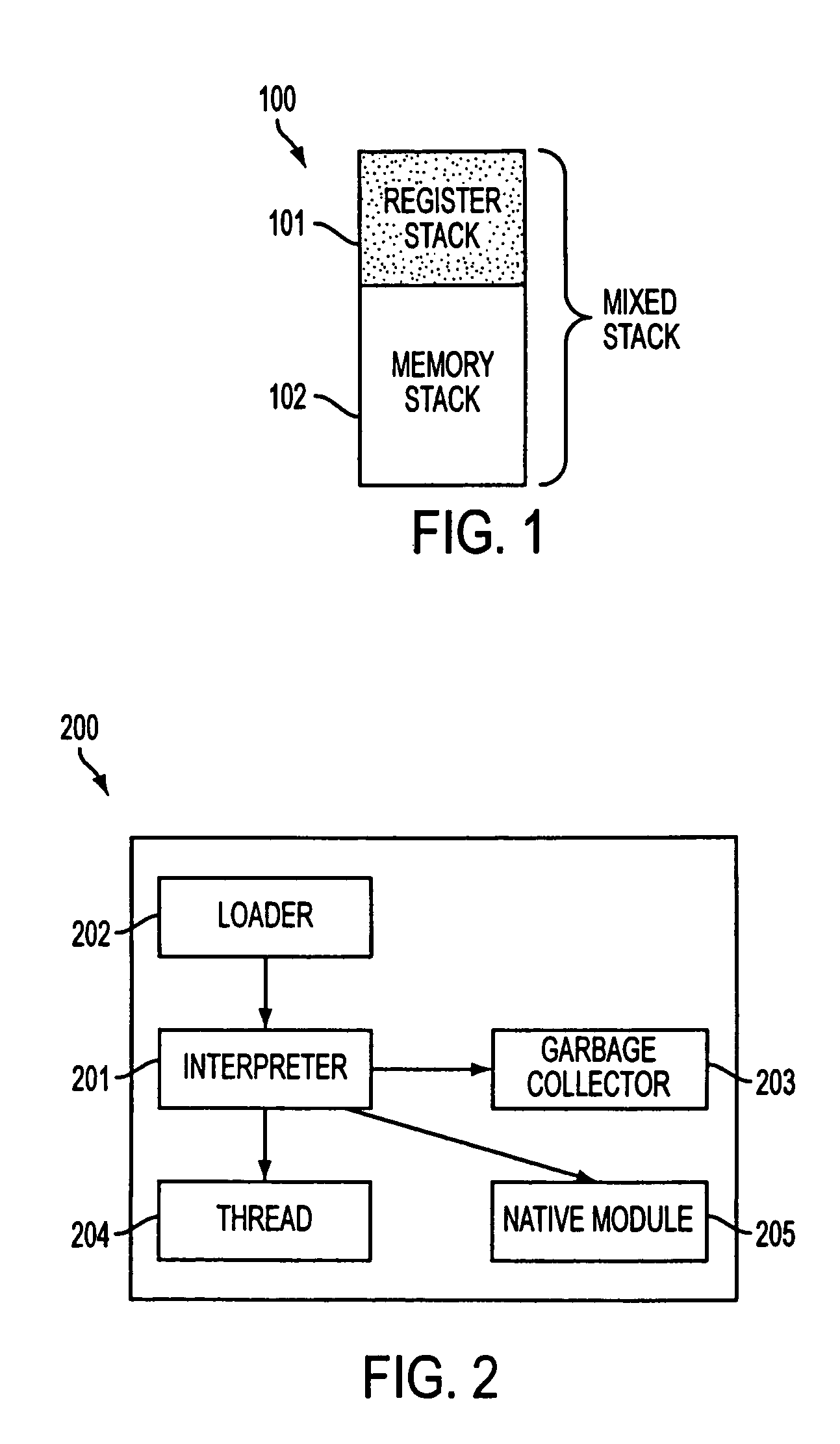

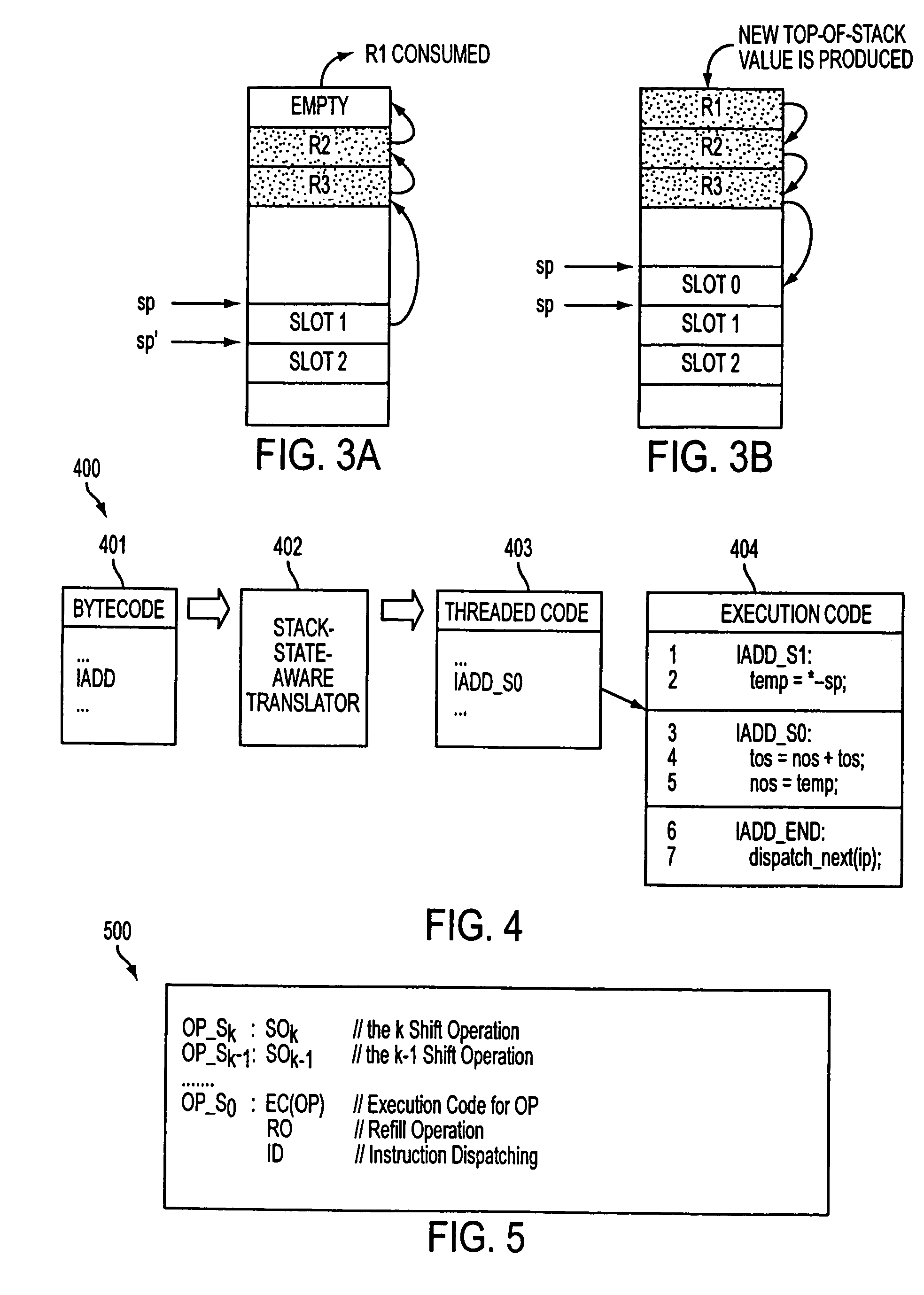

Stack caching using code sharing

InactiveUS20050223370A1Memory architecture accessing/allocationDigital computer detailsCode sharingOperand

Executing an instruction on an operand stack, including performing a stack-state aware translation of the instruction to threaded code to determine an operand stack state for the instruction, dispatching the instruction according to the operand stack state for the instruction, and executing the instruction.

Owner:INTEL CORP +1

Method and structure for explicit software control of execution of a thread including a helper subthread

InactiveCN101263452ADigital computer detailsSpecific program execution arrangementsLong latencyComputerized system

Software instructions in a single thread code sequence with a helper subthread are executed on a processor of a computer system. The execution causes the computer system, for example, to (i) determine whether information associated with a long latency instruction is available, and when the data is unavailable, to (ii) snapshot a state of the computer system and maintain a capability to roll back to that snapshot state, (iii) execute the helper instruction in the helper subthread, and (iv) roll back to the snapshot state upon completion of execution of the helper instructions in the helper subthread and continue execution. The helper subthread, for example prefetches data while waiting for the long latency instruction to complete.

Owner:SUN MICROSYSTEMS INC

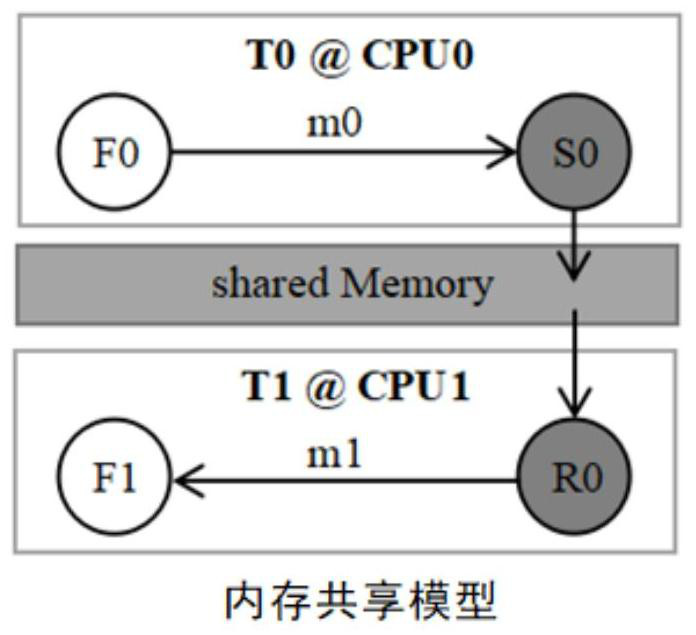

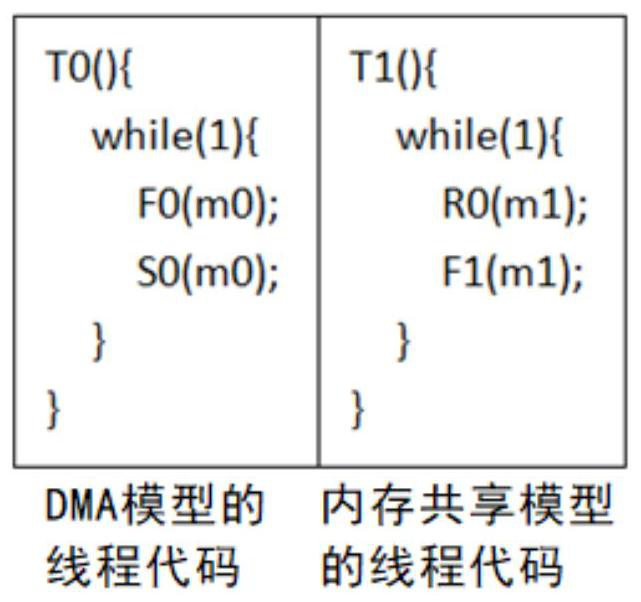

Inter-core communication optimization method oriented to Simulink and capable of automatically generating multi-thread codes

PendingCN112015692AIncrease profitEffective distributionInterprogram communicationDigital computer detailsCode generationGeneration process

The invention provides an inter-core communication optimization method for Simulink-oriented automatic generation of multi-thread codes, and the method employs a technology combining static analysis and dynamic simulation to effectively distribute a communication cache region, so as to further reduce the synchronization cost and improve the utilization rate of a processor. FPGA simulation is introduced into an inter-processor cache region distribution process. Moreover, under the condition of fixed memory overhead, a proper number of entrances are allocated to different communication cache regions, so that the synchronous waiting time and the thread switching time are minimized. According to the method, an optimization method is introduced into a Simulink-based code generation process andis combined with a communication pipeline technology, so that the communication overhead is reduced. The system performance is improved. For the problem of distributing the communication cache region,a technology of combining static analysis and dynamic simulation is adopted, so that the synchronization cost is further reduced, and the utilization rate of a processor is improved.

Owner:EAST CHINA UNIV OF SCI & TECH +1

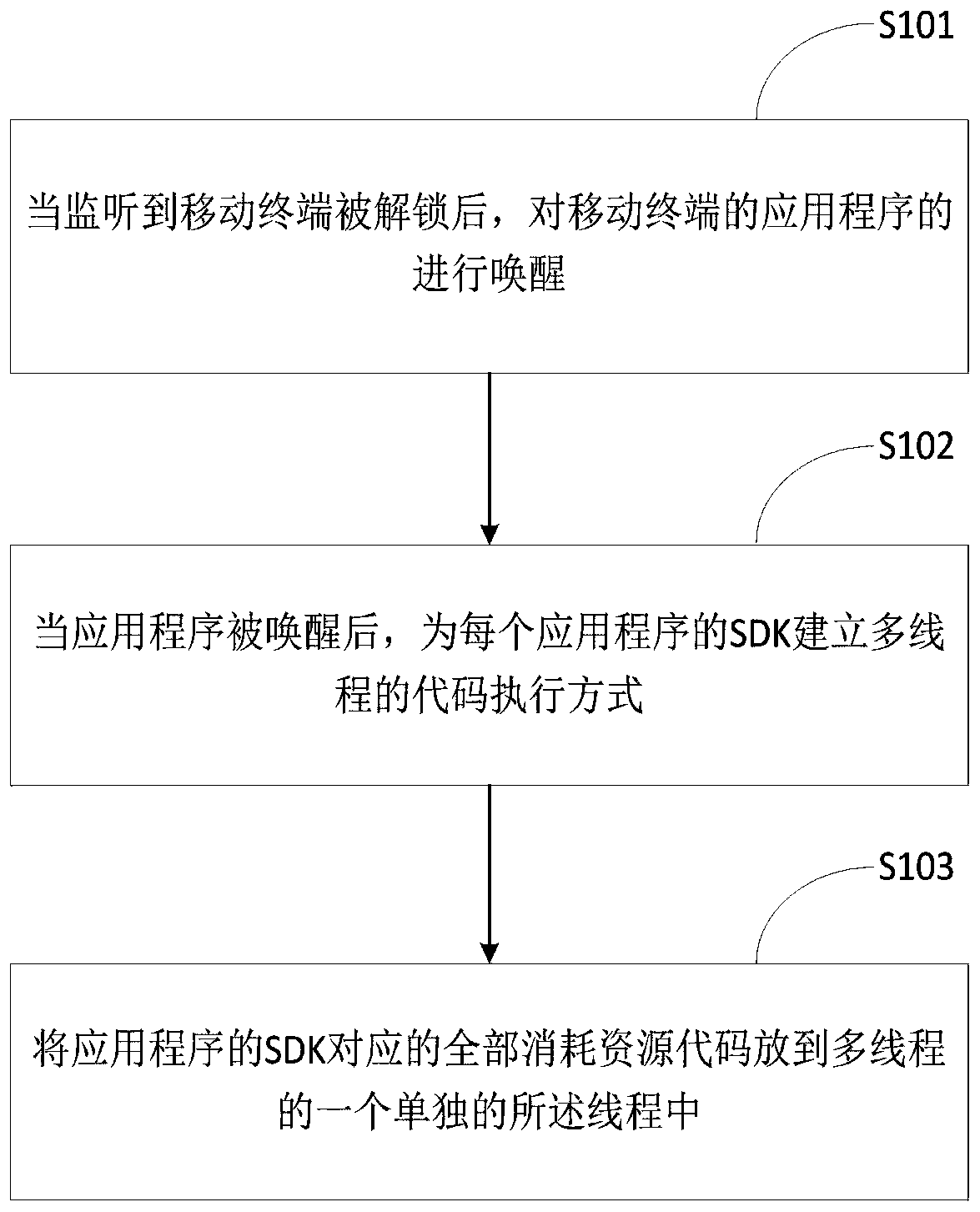

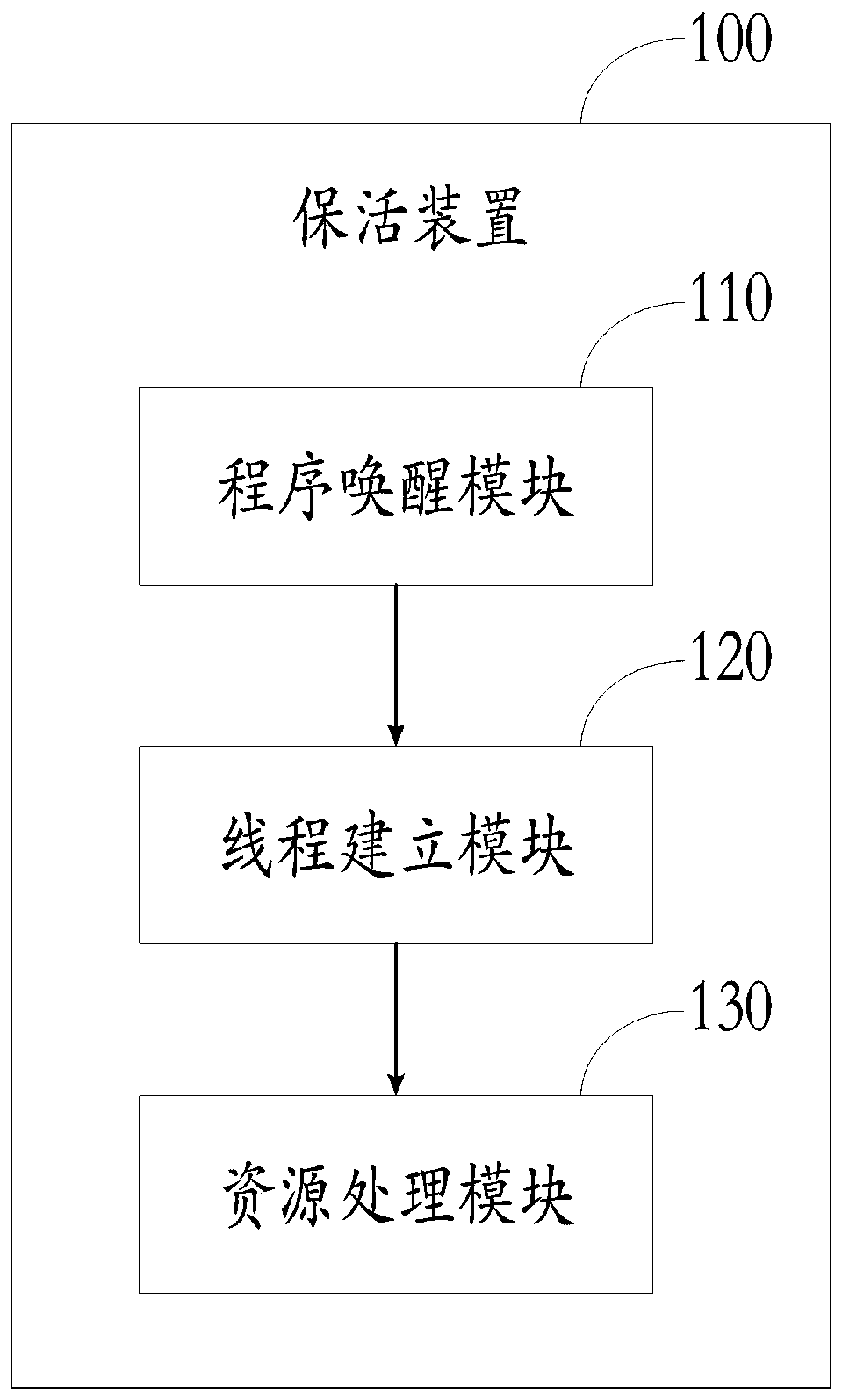

Keep-alive method and device for mobile terminal application program

The invention discloses a keep-alive method and a device for an application program of a mobile terminal, and the method comprises the steps: awakening the application program of the mobile terminal after monitoring that the mobile terminal is unlocked; after the application programs are awakened, establishing a multi-thread code execution mode for the SDK of each application program; and puttingall the consumed resource codes corresponding to the SDK of the application program into one single thread of the multiple threads. Compared with the prior art, the SDK of the application program is optimized under the system mechanism, the behavior of cheating the system is not involved, the keep-alive capacity of the SDK is improved, and the keep-alive method does not depend on the third-party SDK, so that the SDK is not influenced by the third-party SDK, and the compatibility of the SDK is improved.

Owner:SHENZHEN SHUWEI MEDIA TECH CO LTD

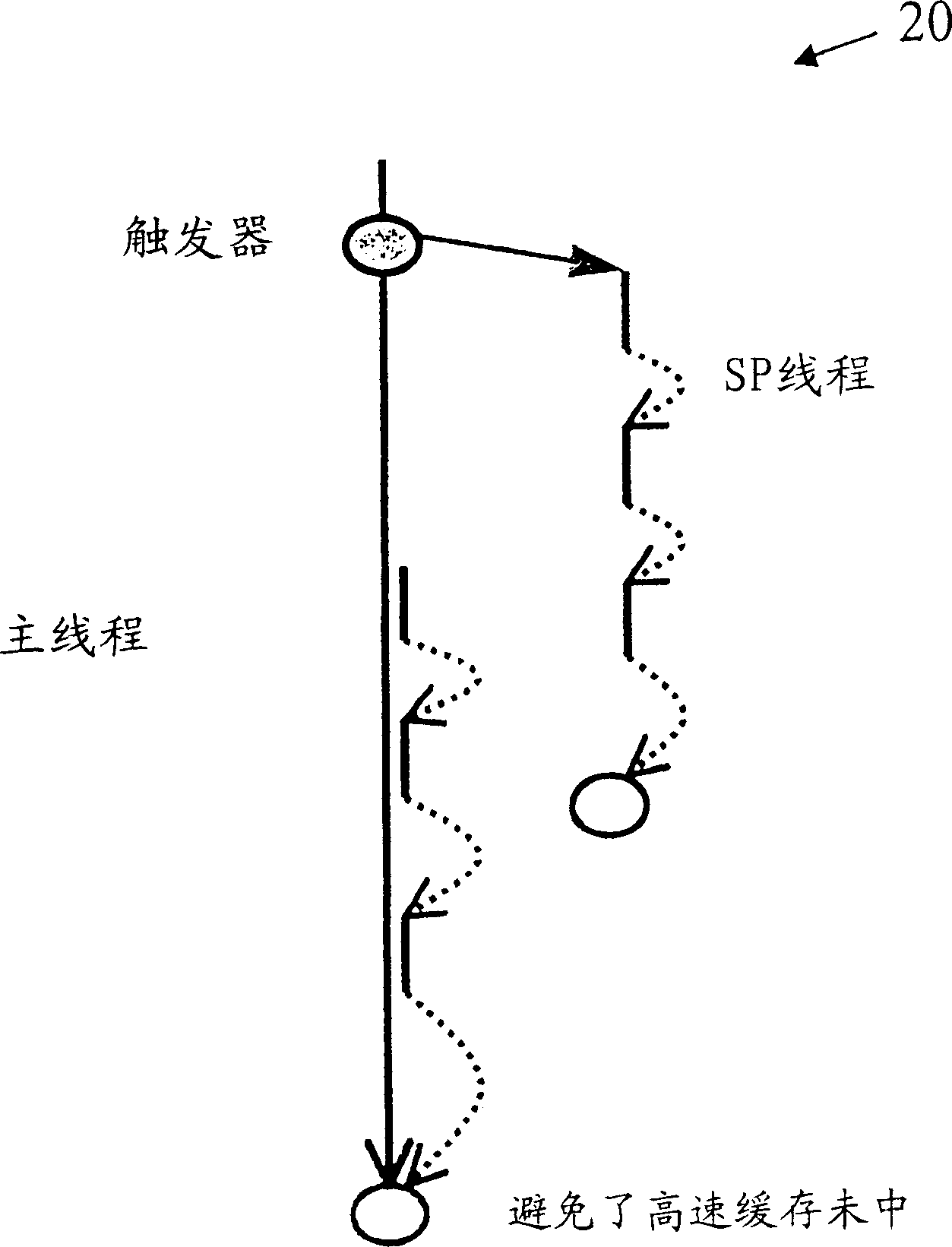

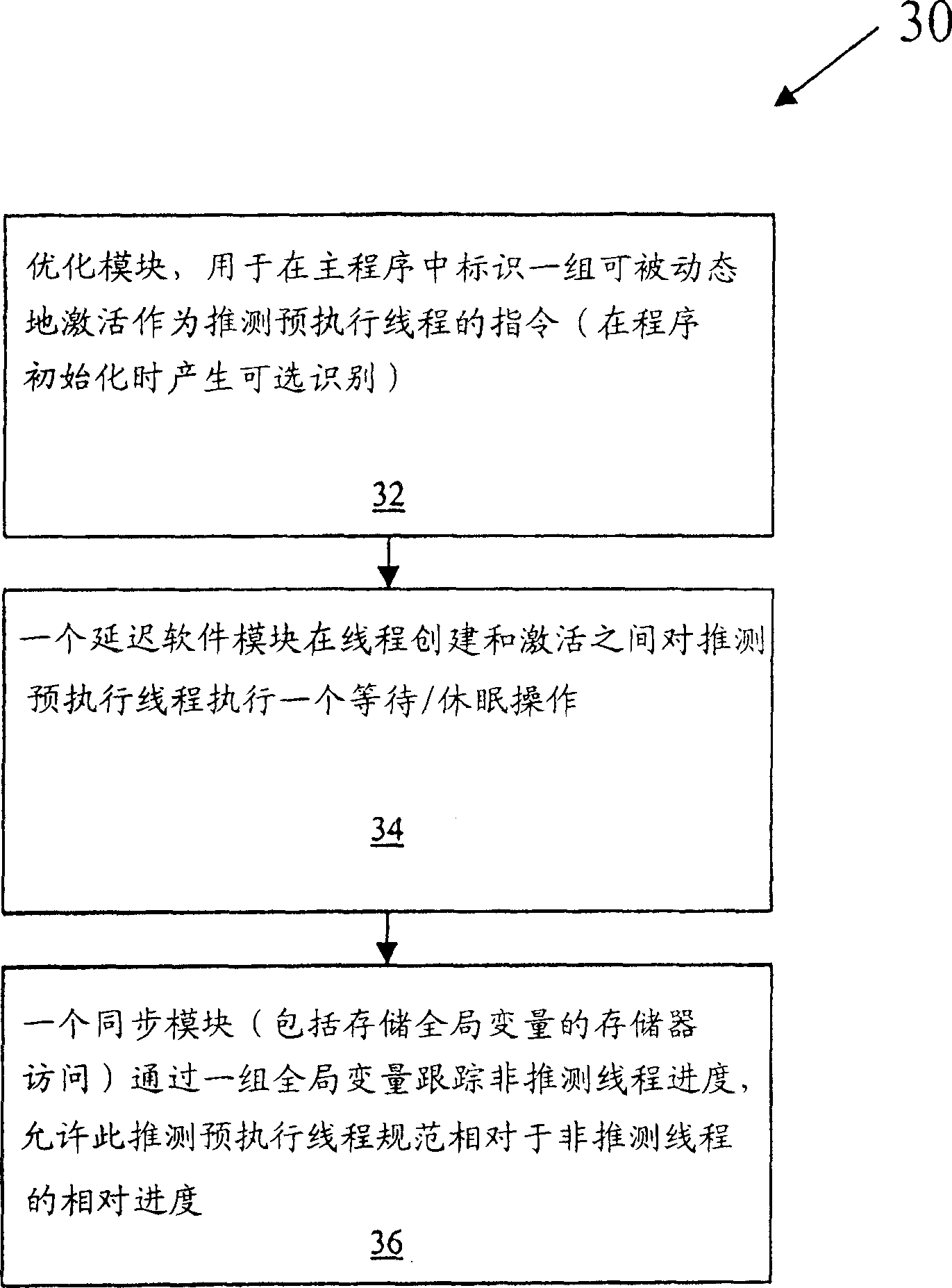

Transform of single line routine code to conjecture preexecute starting code

In one embodiment a thread management method identifies in a main program a set of instructions that can be dynamically activated as speculative precomputation threads. A wait / sleep operation is performed on the speculative precomputation threads between thread creation and activation, and progress of non-speculative threads is gauged through monitoring a set of global variables, allowing the speculative precomputation threads to determine its relative progress with respect to non-speculative threads.

Owner:INTEL CORP

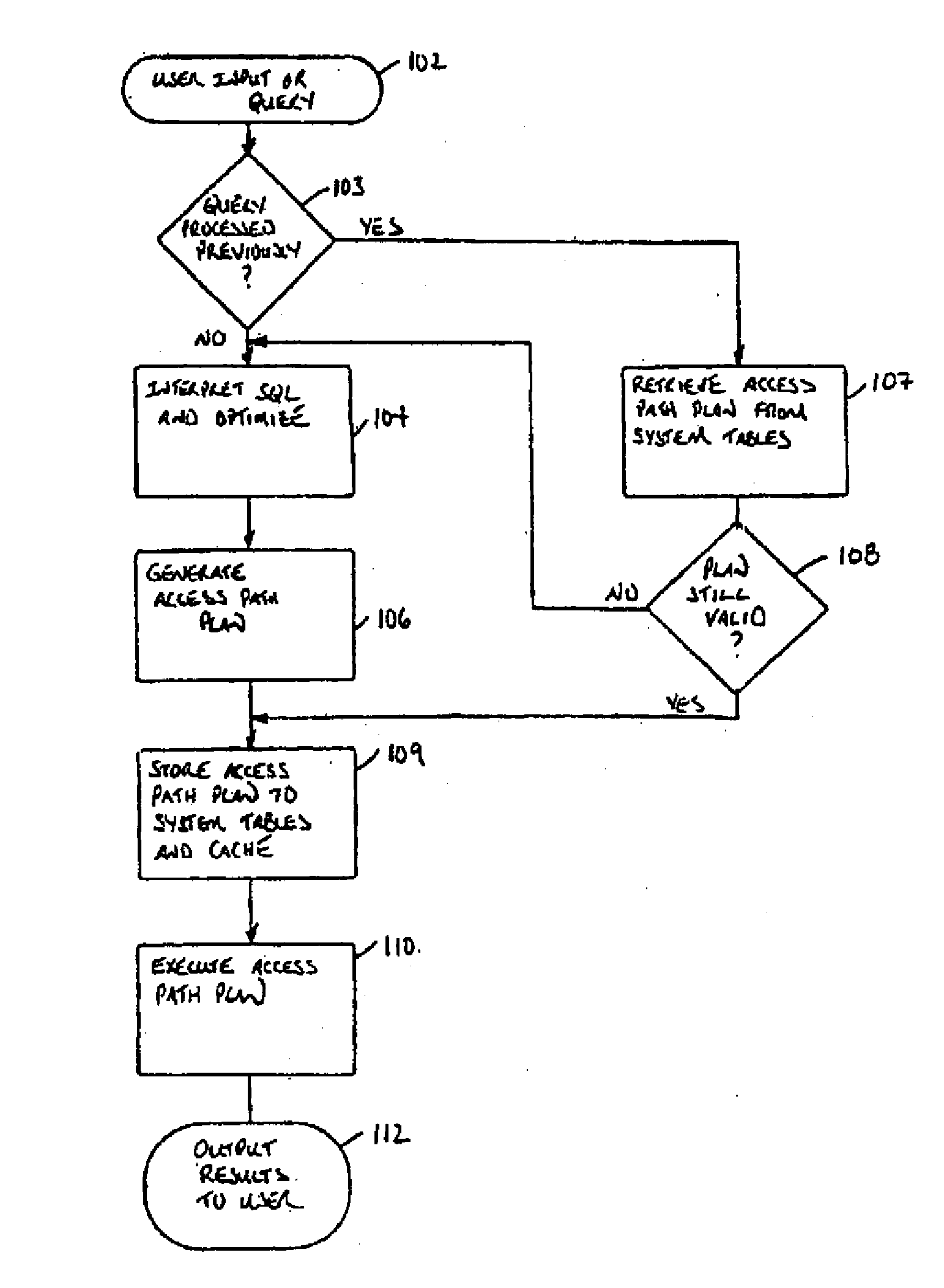

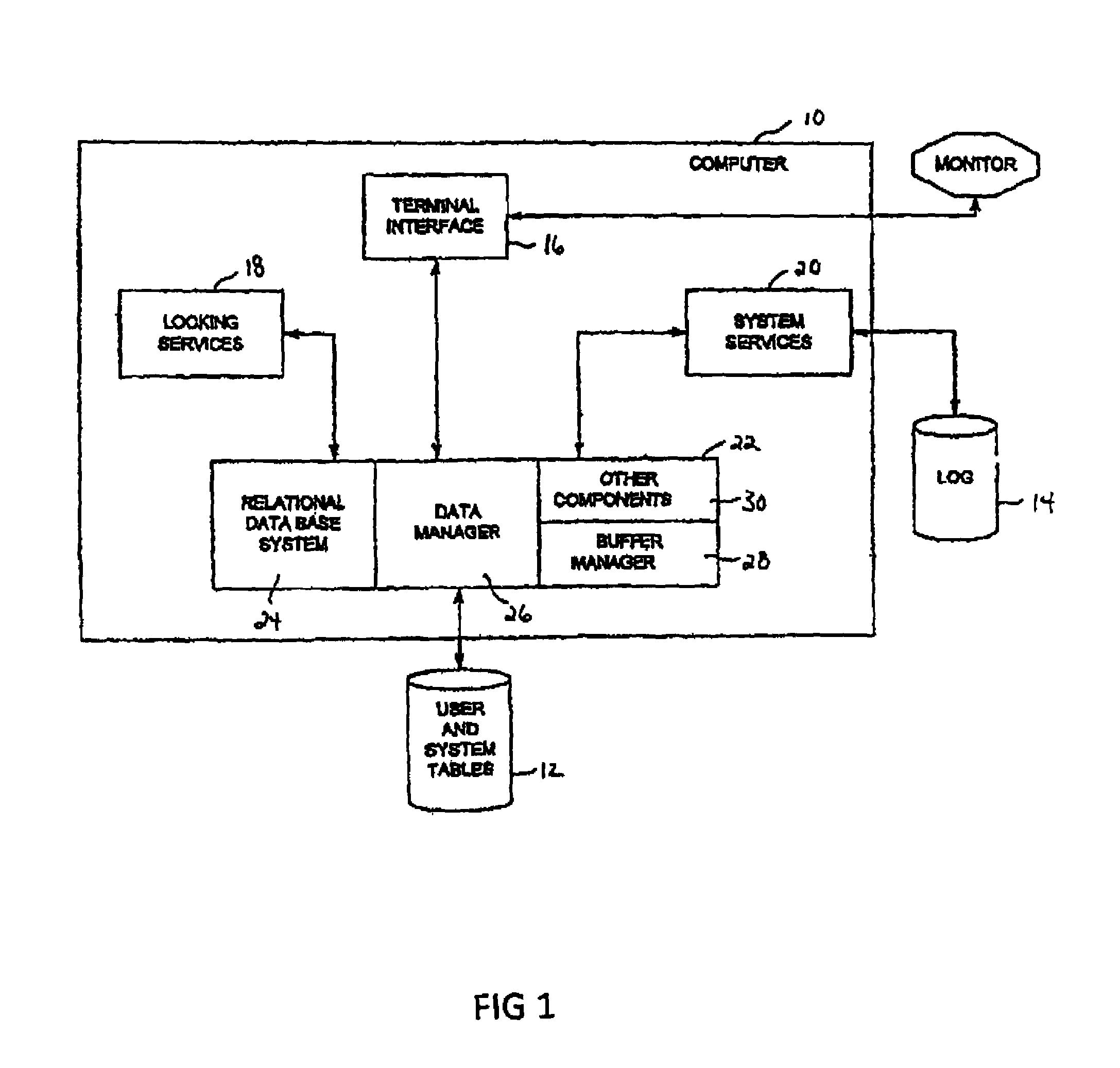

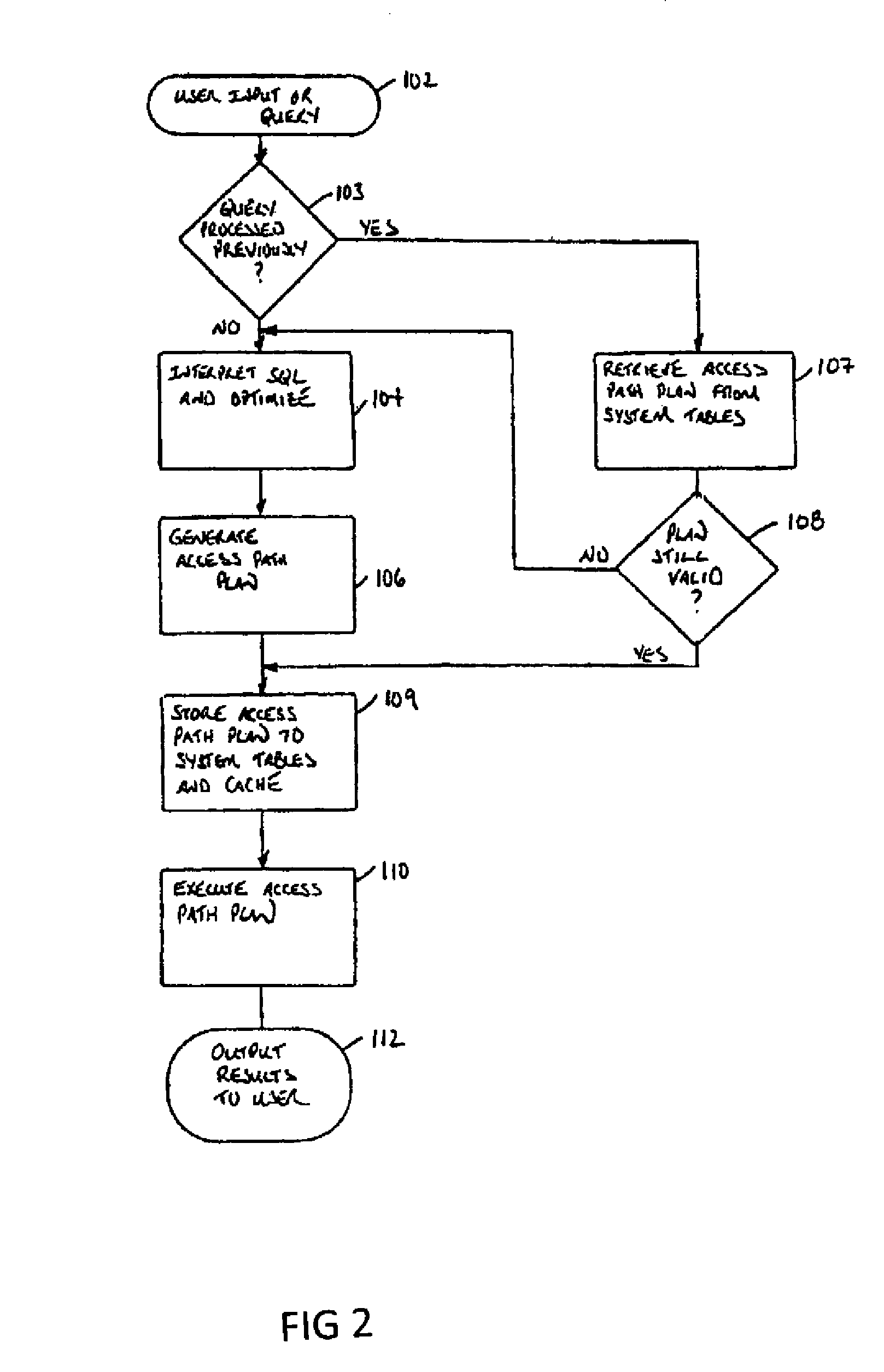

Direct call threaded code

InactiveUS7974968B2Improve performanceReduce overheadData processing applicationsDigital data information retrievalProgramming languageProgram planning

A pre-pass and direct call mechanism which replaces the interpreter. The mechanism moves static decisions out of the repeated runtime path, into a pre-pass operation. Advantageously, the mechanism reduces runtime overhead, and improves overall performance of the DBMS during runtime, while maintaining the considerable investment in opcode generation and plan representation, already invested in the implementation of the DBMS.

Owner:INT BUSINESS MASCH CORP

Code interpretation using stack state information

InactiveUS7424596B2Memory architecture accessing/allocationDigital computer detailsOperandThreaded code

Executing an instruction on an operand stack, including performing a stack-state aware translation of the instruction to threaded code to determine an operand stack state for the instruction, dispatching the instruction according to the operand stack state for the instruction, and executing the instruction.

Owner:INTEL CORP +1

A method and device for android anti-retransmission

ActiveCN107133150BPrevent retransmission problemHardware monitoringOperating systemReliability engineering

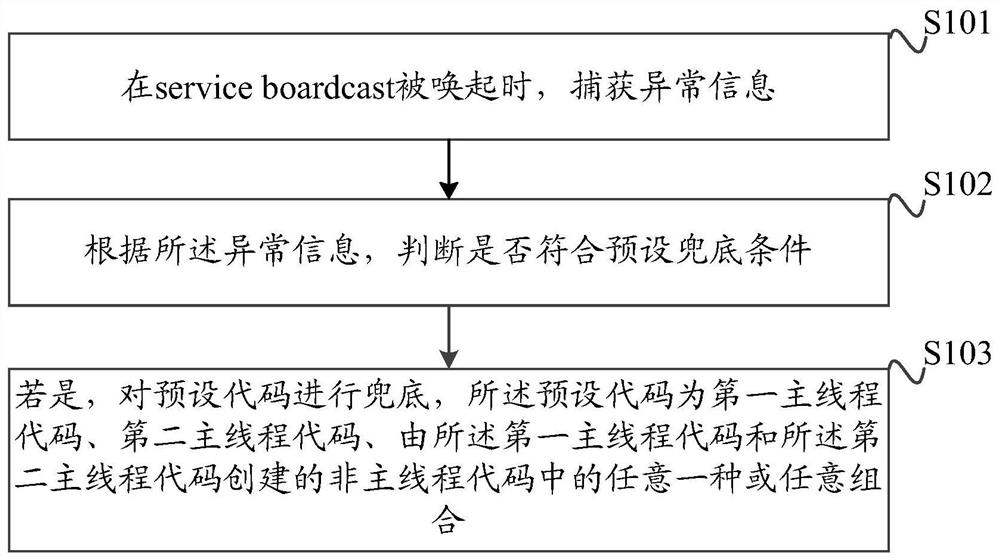

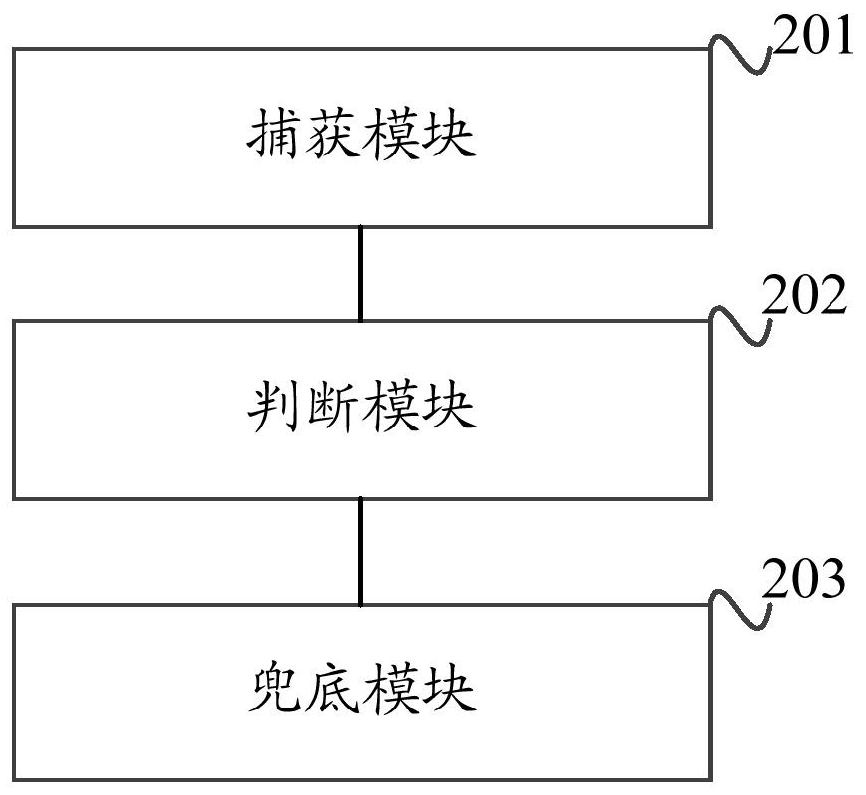

The invention discloses an Android retransmission preventing method. The method comprises the following steps: acquiring abnormality information when service boardcast is aroused; determining whether preset revealing conditions are met according to the abnormality information; and if so, revealing a preset code, wherein the preset code includes any one or any combination of a first main thread code, a second main thread code, and non-main-thread codes constructed through the first main thread code and the second main thread code. According to the method, whether the retransmission resisting conditions are met is determined according to the acquired abnormality information; if the revealing conditions are met, the corresponding code is revealed, the circumstance that the abnormal code is continuously performed due to some causes is prevented, and further that the retransmission is continuously carried out can be prevented. In addition, the invention also discloses an Android retransmission preventing device which has the advantages of the method.

Owner:HANGZHOU SHIQU INFORMATION TECH CO LTD

Automatic fine-grained two-stage parallel translation method

PendingCN114398039AIncrease computing densityLogical branches are simpleResource allocationCode compilationComputational scienceTheoretical computer science

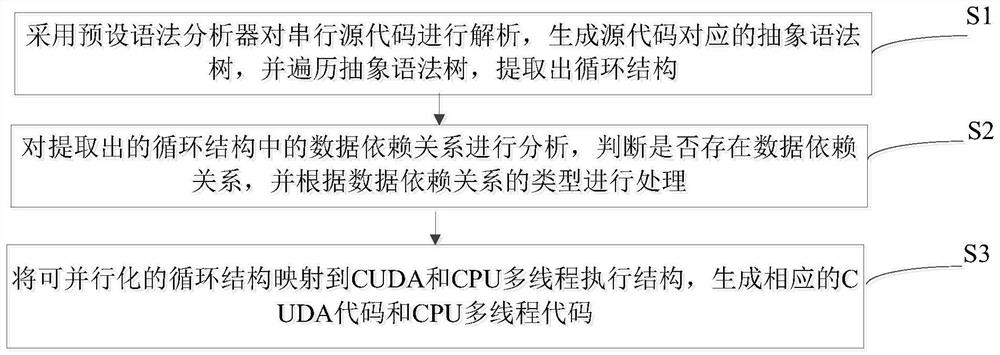

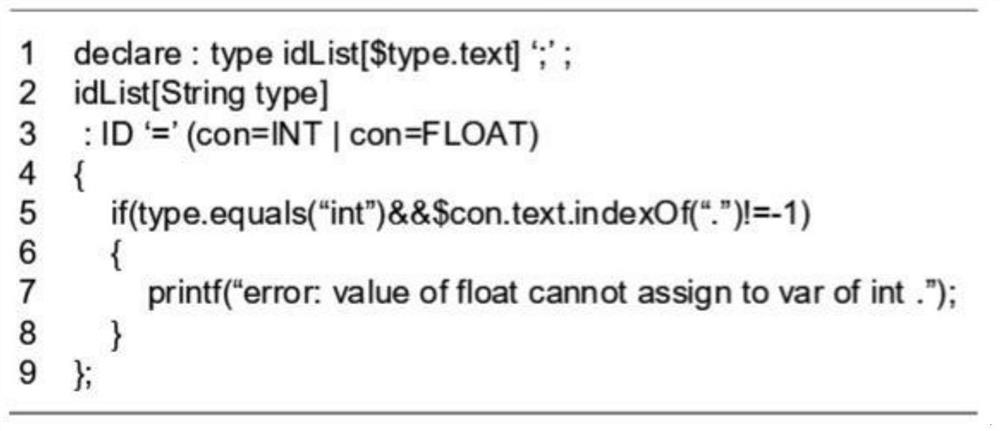

The invention provides an automatic fine-grained two-stage parallel translation method, which comprises the following steps of: firstly, analyzing a source C code through ANTLR, automatically generating an EBNF grammar description, and generating a corresponding lexical and grammar analyzer; secondly, loop information extracted from the analyzer is analyzed, and if flow dependency relationships are found, loop statements containing the dependency relationships cannot be parallelized; and if the anti-dependency relationship and the output dependency relationship between the data are found, eliminating the dependency relationship. And if the data dependency relationship does not exist, the loop statement is parallelizable. According to the method, the parallel loop structure is mapped to a structure suitable for CUDA and CPU multi-thread execution, then corresponding CUDA codes and CPU multi-thread codes are generated, computing resources can be saved, and computing efficiency can be improved.

Owner:WUHAN UNIV

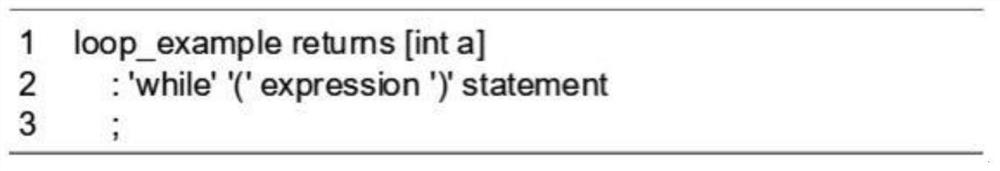

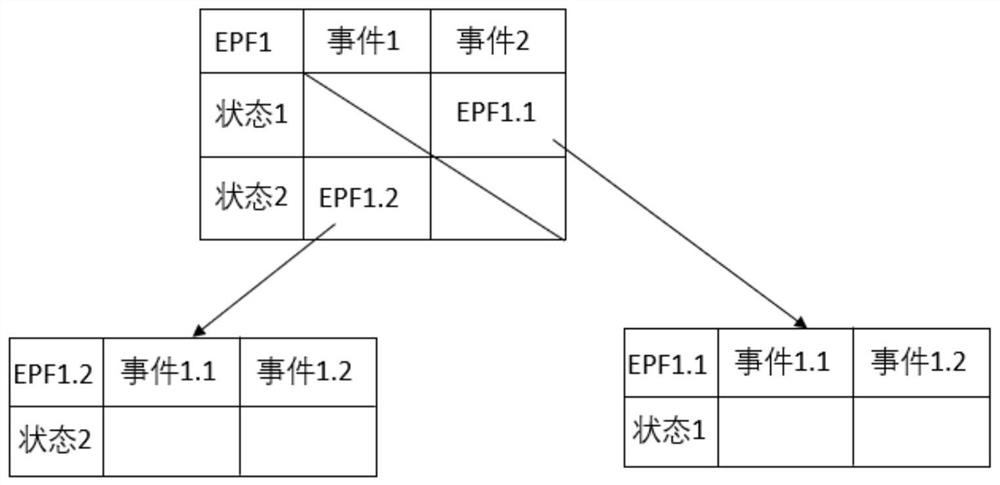

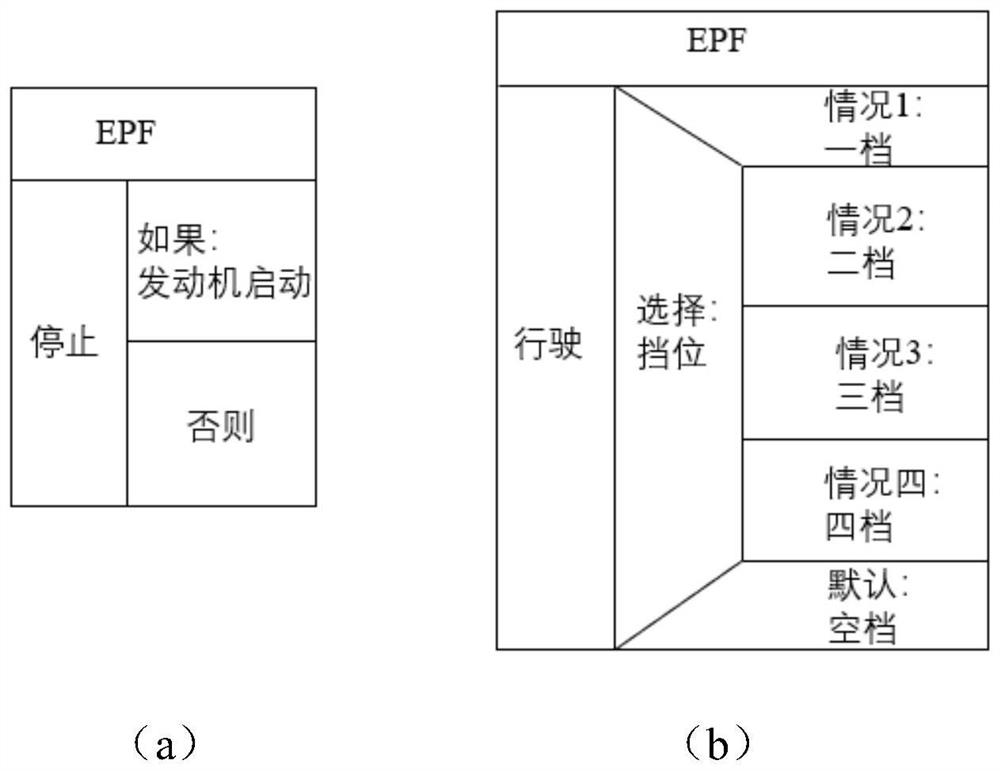

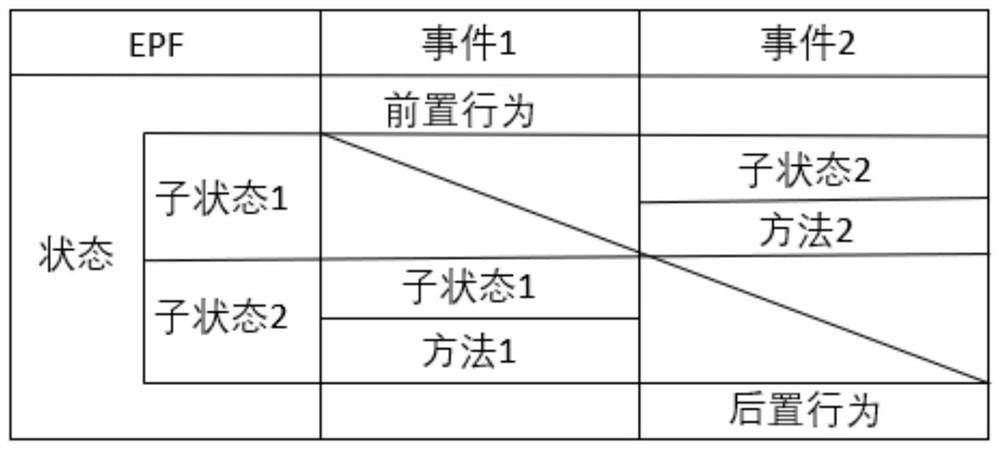

JAVA code generation tool based on EPF

The invention belongs to the field of software development, and discloses a JAVA code generation tool based on EPF. The JAVA code generation tool is based on an event processing table, supports concurrent modeling, supports generation of concurrent codes, and comprises a formalized modeling tool EPF and an algorithm for automatically generating JAVA codes; according to the method, a simple and understandable modeling tool is provided while the formalized semantics of the software are reserved; concurrent modeling is supported, and a multi-thread JAVA code is generated; software design defects can be explicitly represented; formalized verification can be conveniently carried out; a plurality of logic judgment units are included so as to adapt to complex design requirements; code quality can be improved by automatically generating codes, and workload of workers is reduced; and the model and the code are decoupled, so that the cost of software iteration is reduced.

Owner:DALIAN UNIV OF TECH

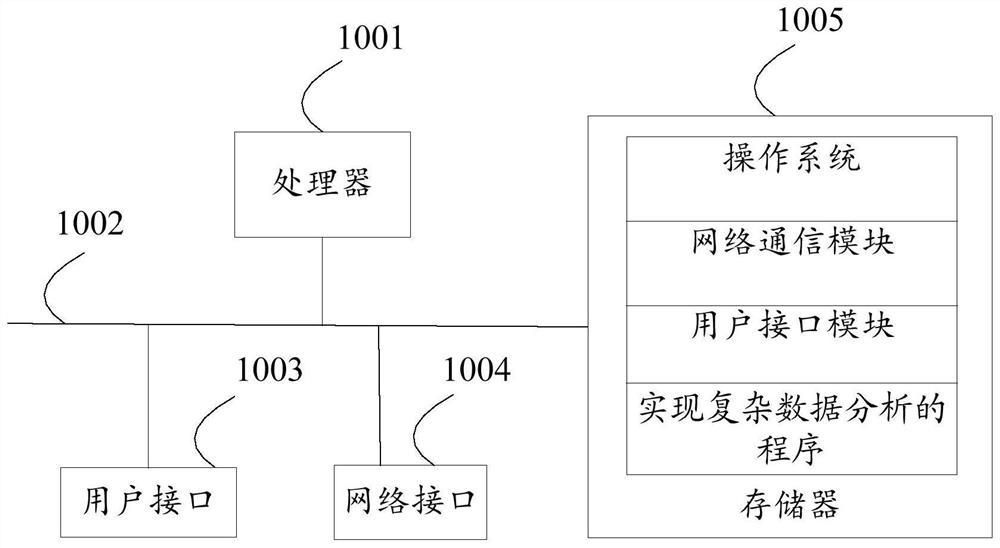

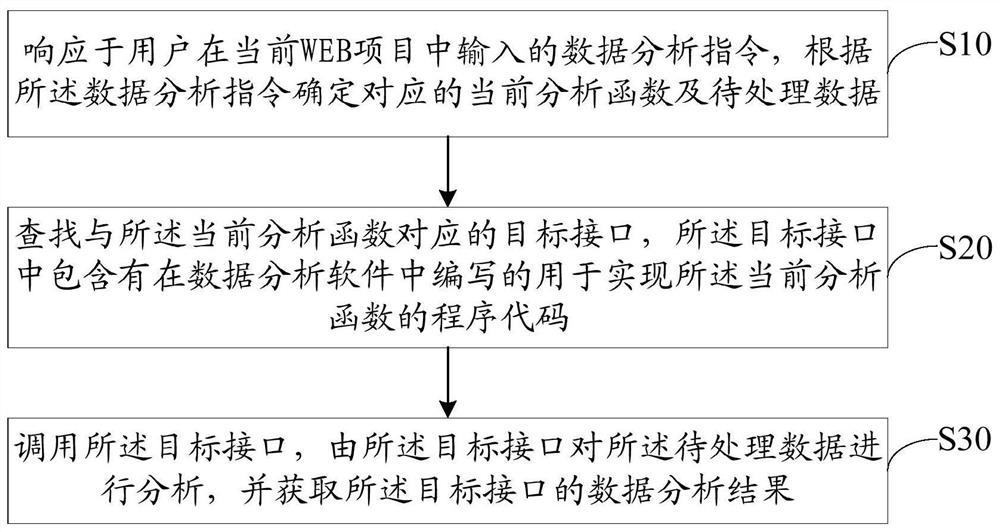

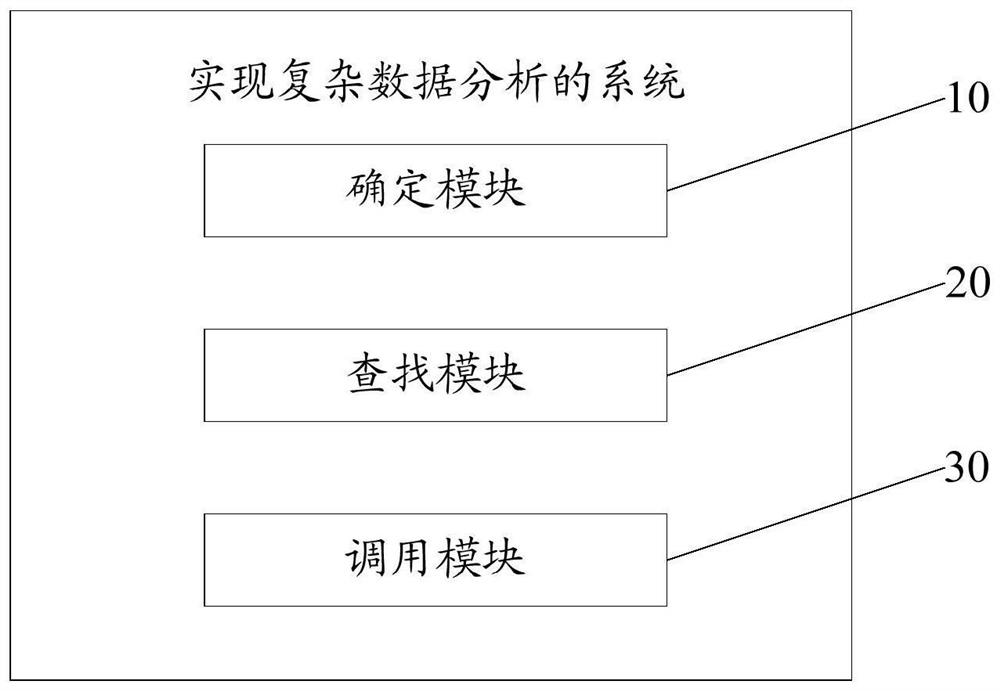

Method, device, system and storage medium for realizing complex data analysis

The invention discloses a method, device, system and storage medium for realizing complex data analysis. In response to the data analysis instruction input by the user in the current WEB project, determine the corresponding current analysis function and the data to be processed, and search for the target interface corresponding to the current analysis function, and the target interface includes the data written in the data analysis software. The program code used to implement the current analysis function, calls the target interface, analyzes the data to be processed by the target interface, and obtains the data analysis result of the target interface. The program codes written in the software analyze complex data, and by using the powerful algorithm analysis capabilities of existing data analysis software, WEB projects developed in Java and other languages can also have the function of dealing with complex algorithm problems, thereby avoiding manual processing in projects. Write multi-threaded code and other methods to deal with complex algorithm problems, which improves the efficiency of the program.

Owner:WUHAN POLYTECHNIC UNIVERSITY

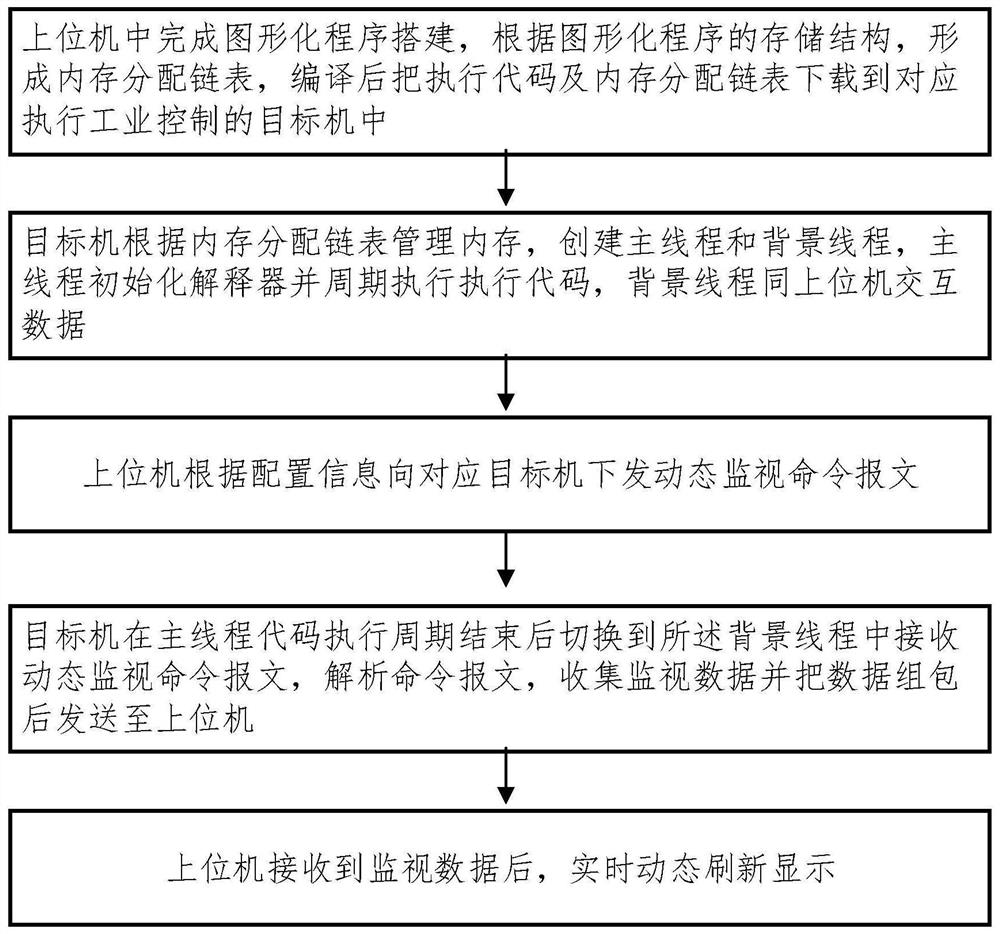

Industrial control graphical programming environment running state data monitoring system and method

ActiveCN113590106BEasy to debugEasy to analyzeHardware monitoringVisual/graphical programmingSoftware engineeringDynamic monitoring

Owner:XJ ELECTRIC +1

Hiding Memory Latency

InactiveUS20080162906A1Memory latencyDigital computer detailsMultiprogramming arrangementsExternal dataParallel computing

Owner:INT BUSINESS MASCH CORP