SRAM cells having landing pad in contact with upper and lower cell gate patterns and methods of forming the same

a technology of sram cells and gate patterns, applied in the field of sram cells having a landing pad in contact with upper and lower cell gate patterns, can solve the problems of weak latch-up immunity and lower integration density of sram cells in bulk cmos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

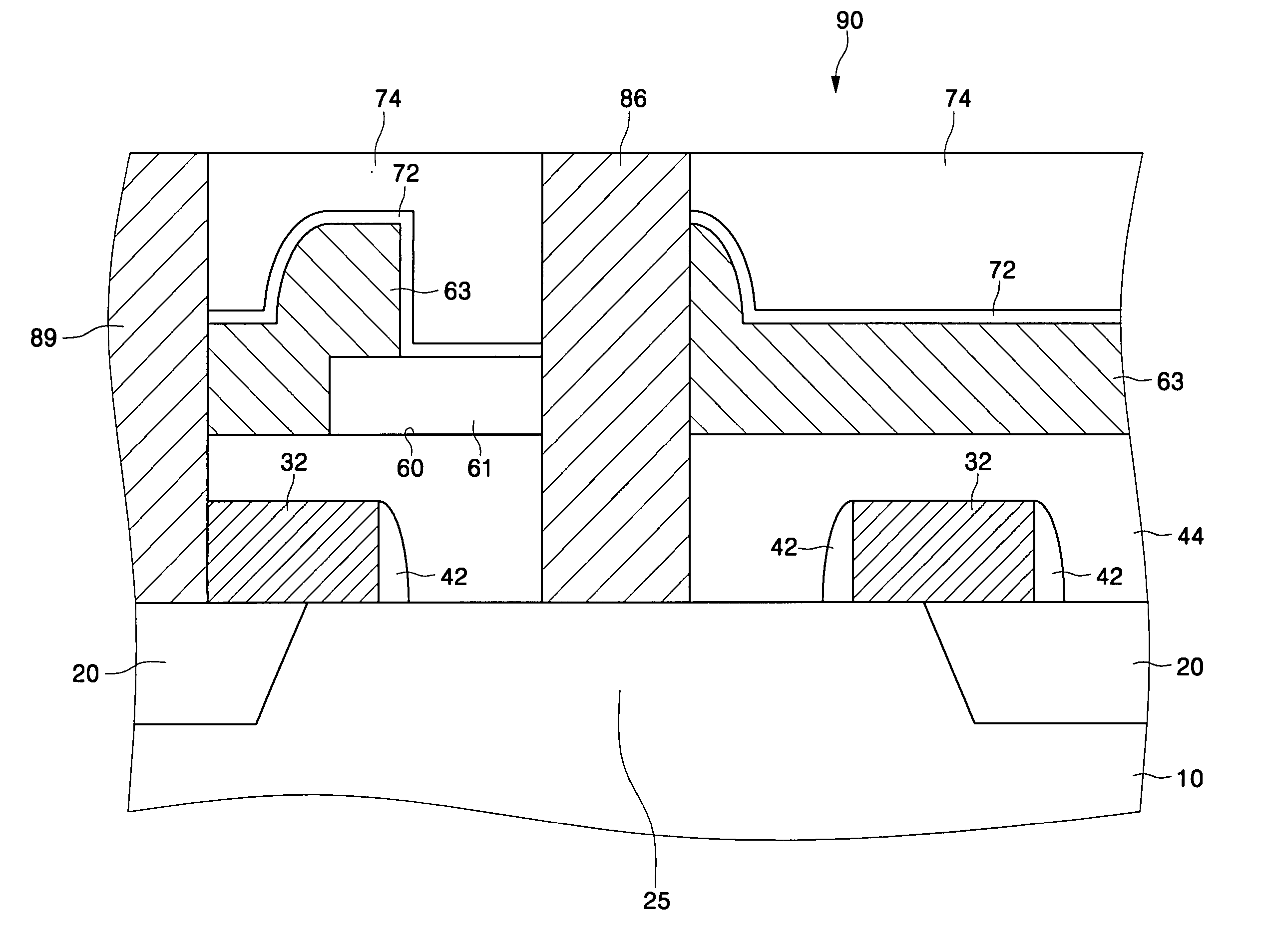

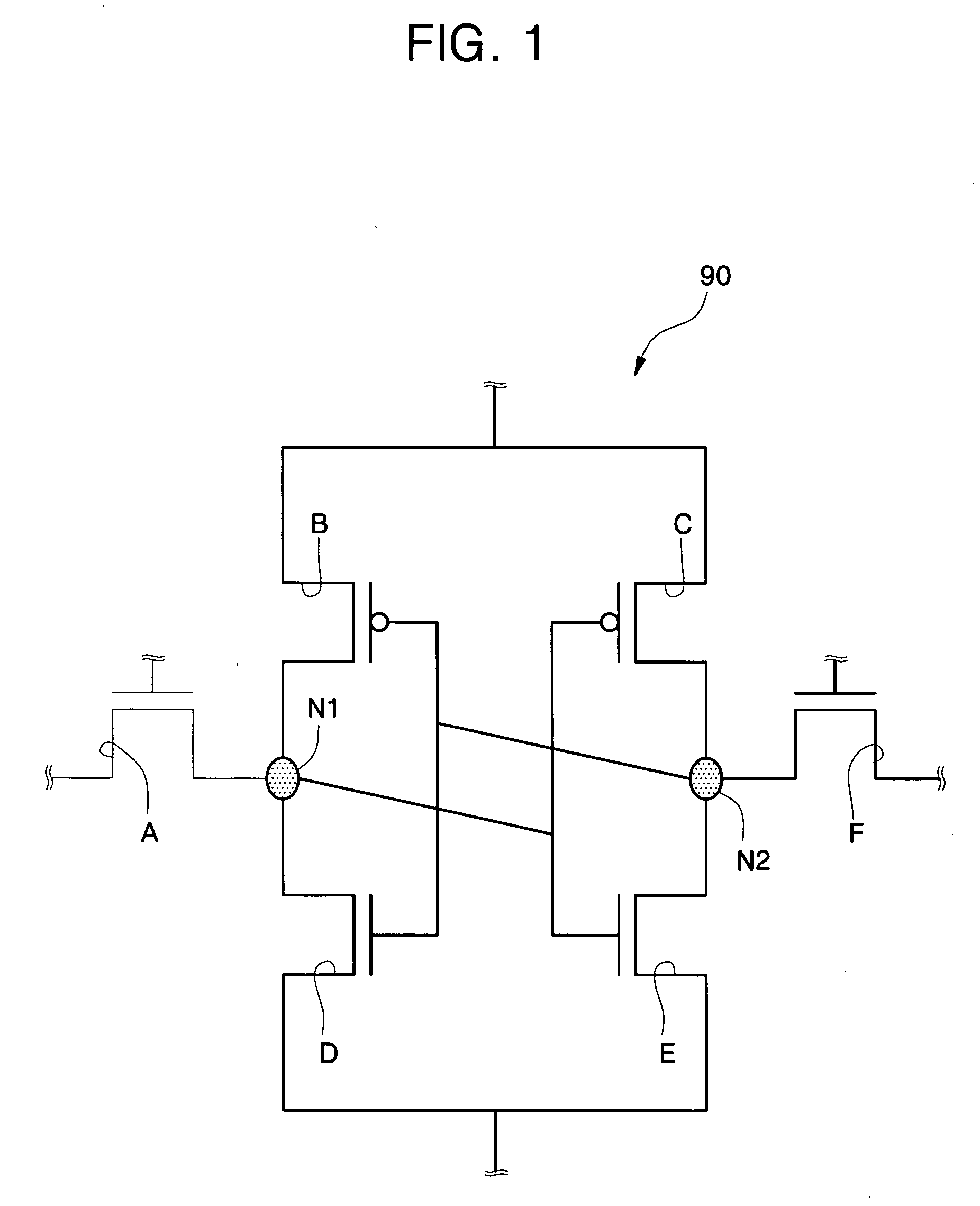

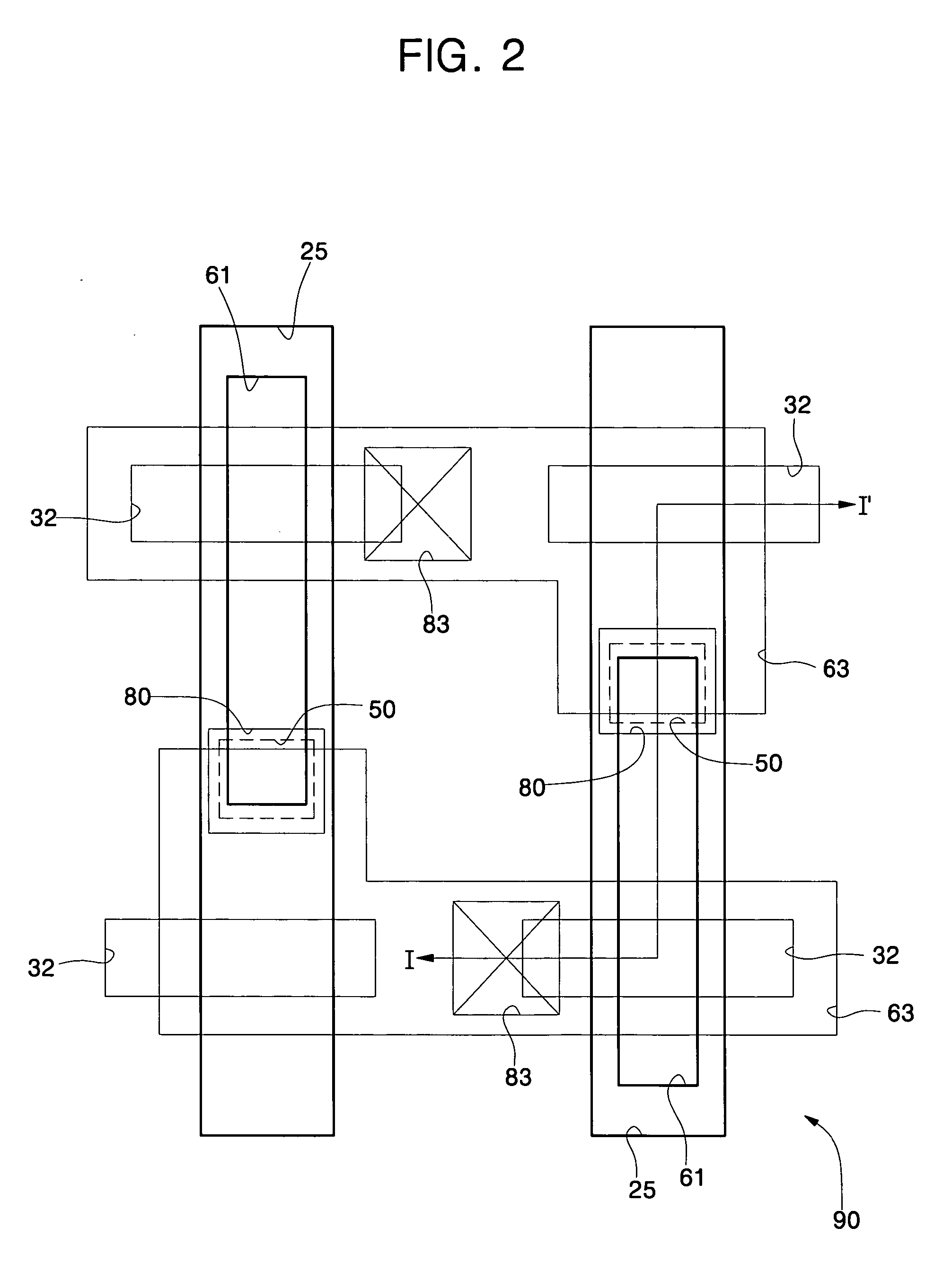

[0020]FIG. 1 is a circuit diagram illustrating an SRAM cell in a cell array region according to the present invention, and FIG. 2 is a layout view illustrating the SRAM cell of FIG. 1. Further, FIG. 3 is a cross sectional view of the SRAM cell taken along line I-I′ of FIG. 2.

[0021] Referring to FIGS. 1 to 3, an SRAM cell normally has six transistors A, B, C, D, E, and F within one cell of a cell array region. The transistors A, B, C, D, E, and F constitute a latch structure and show electrical characteristics of the latch structure. That is, two transistors B and D among the transistors A, B, C, D, E, and F are connected to one electrical node N2 together with three opposite transistors C, E, and F. And two transistors C and E among the transistors A, B, C, D, E, and F are connected to the other electrical node N1 together with three opposite transistors A, B, and D. At this time, two transistors B and C among the transistors A, B, C, D, E, and F are P-type MOSFET (Metal Oxide Semi...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap