Patents

Literature

67 results about "Body Patterning" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The processes occurring in early development that direct morphogenesis. They specify the body plan ensuring that cells will proceed to differentiate, grow, and diversify in size and shape at the correct relative positions. Included are axial patterning, segmentation, compartment specification, limb position, organ boundary patterning, blood vessel patterning, etc.

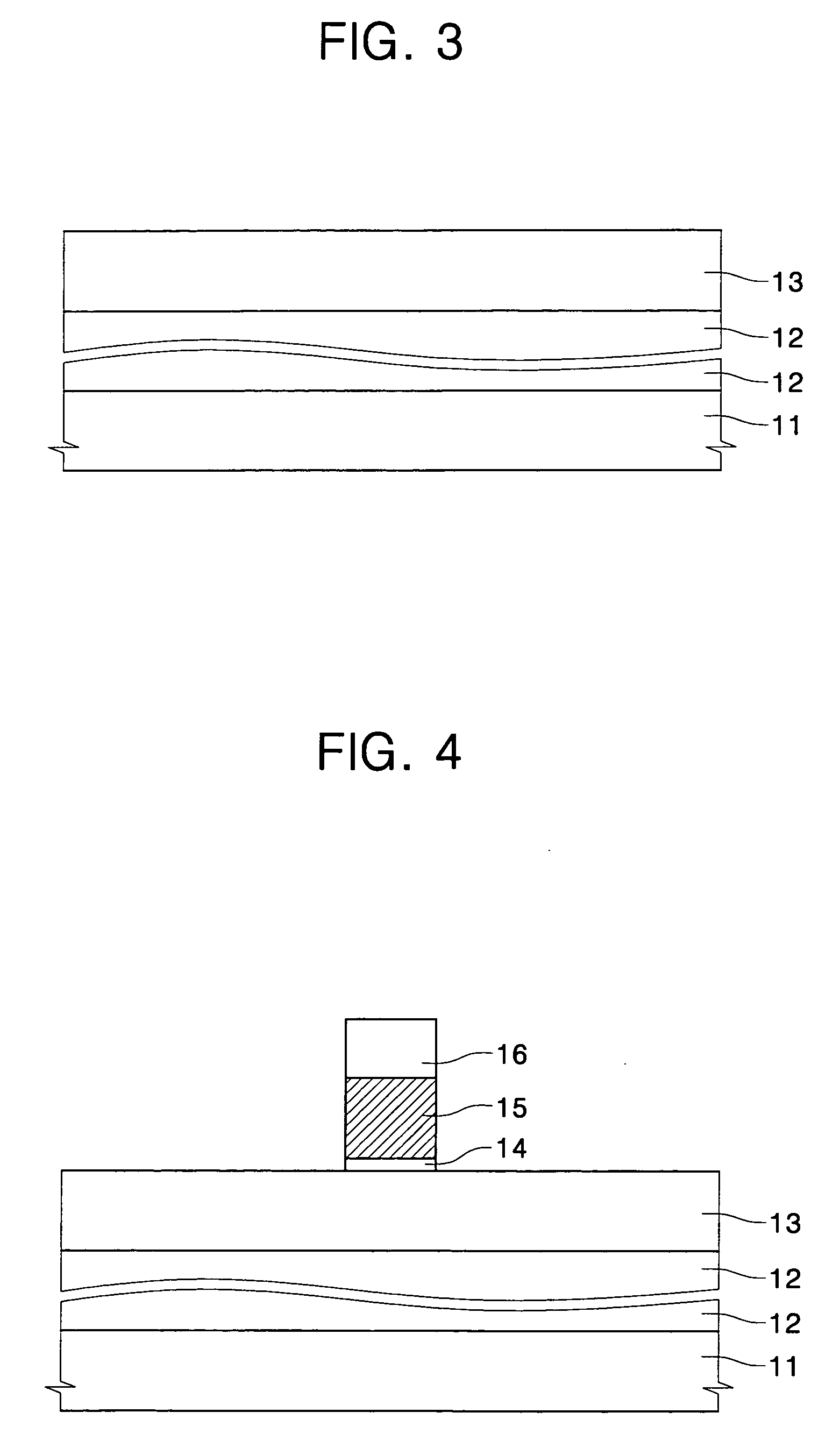

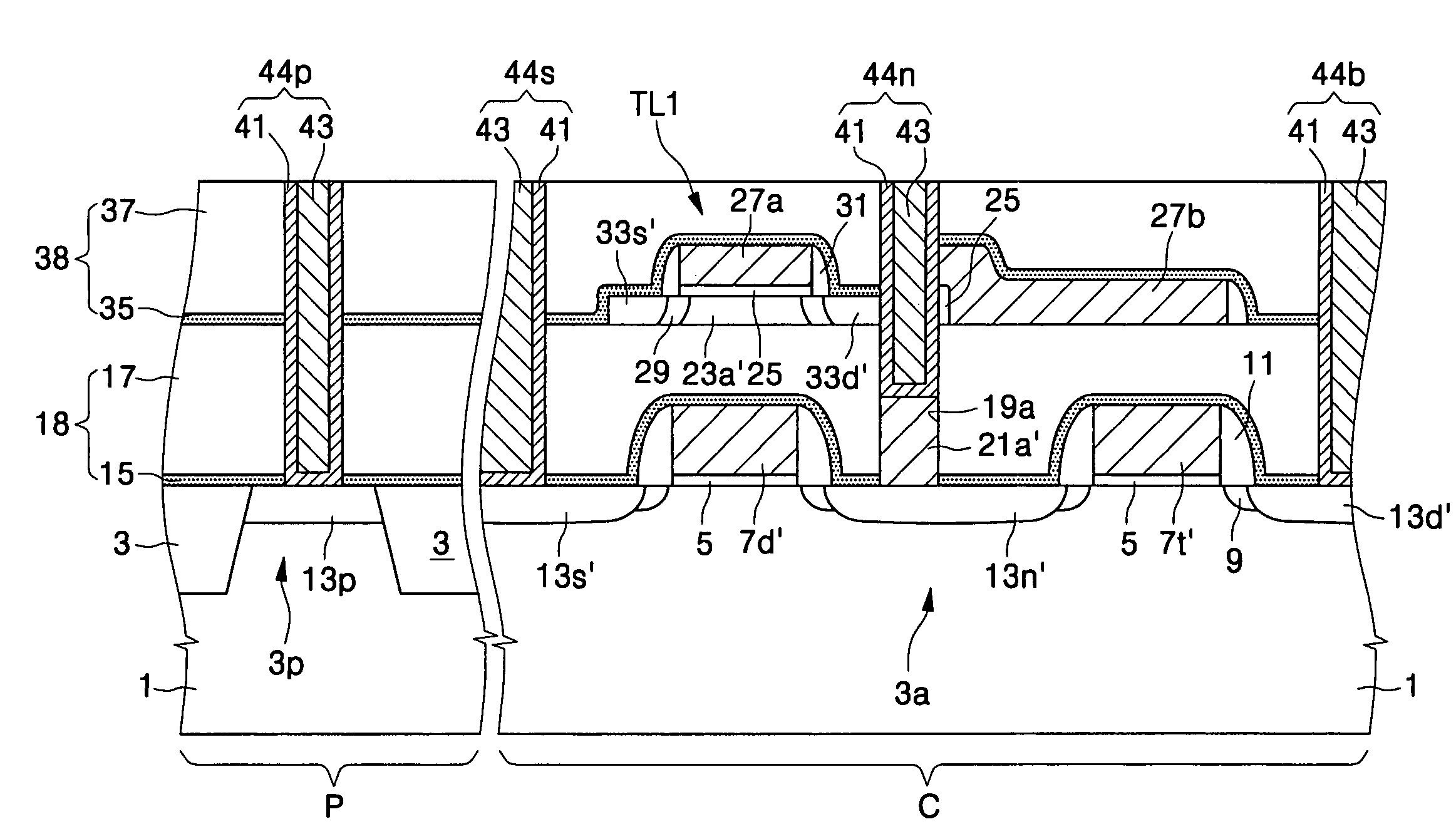

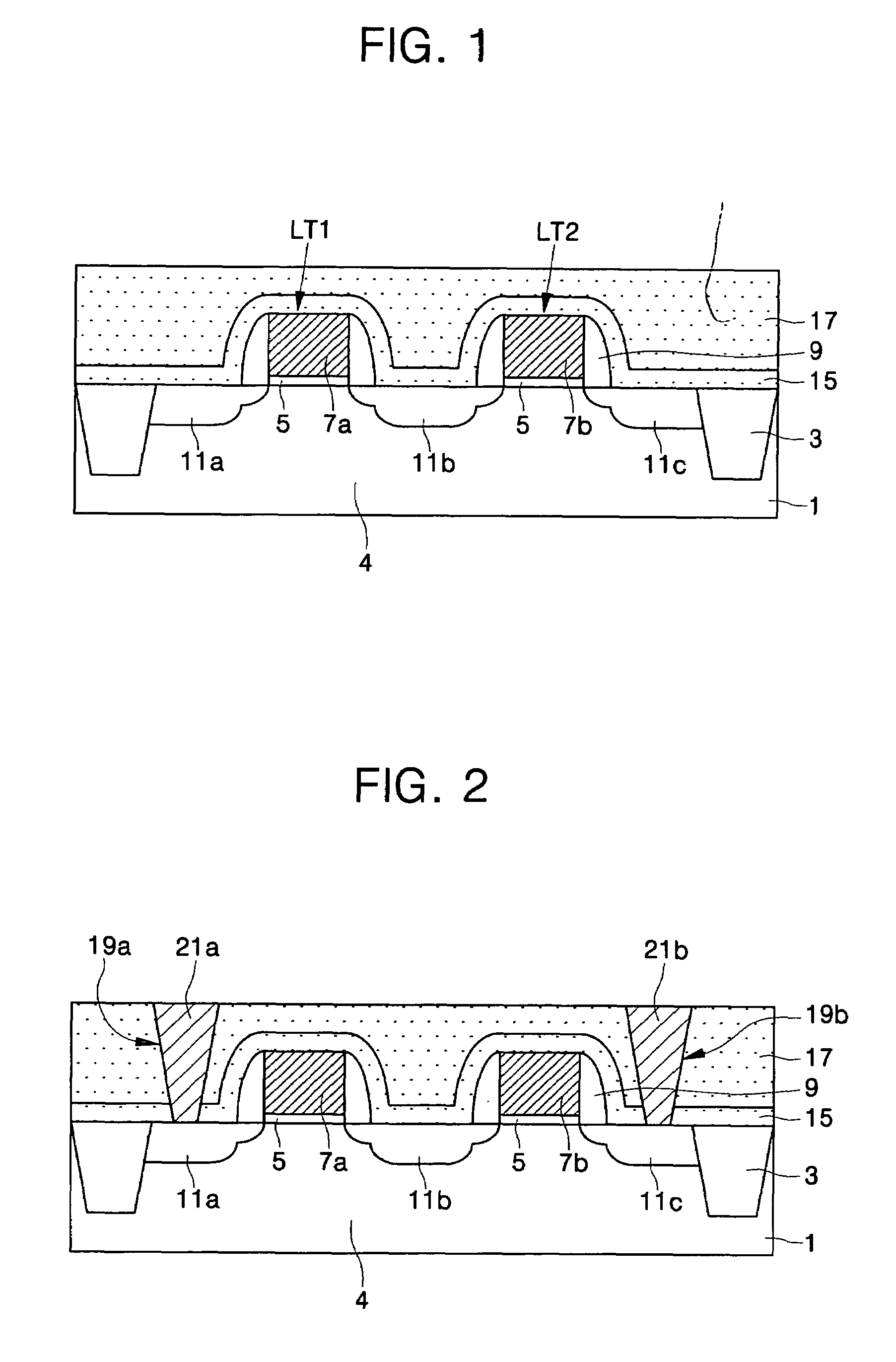

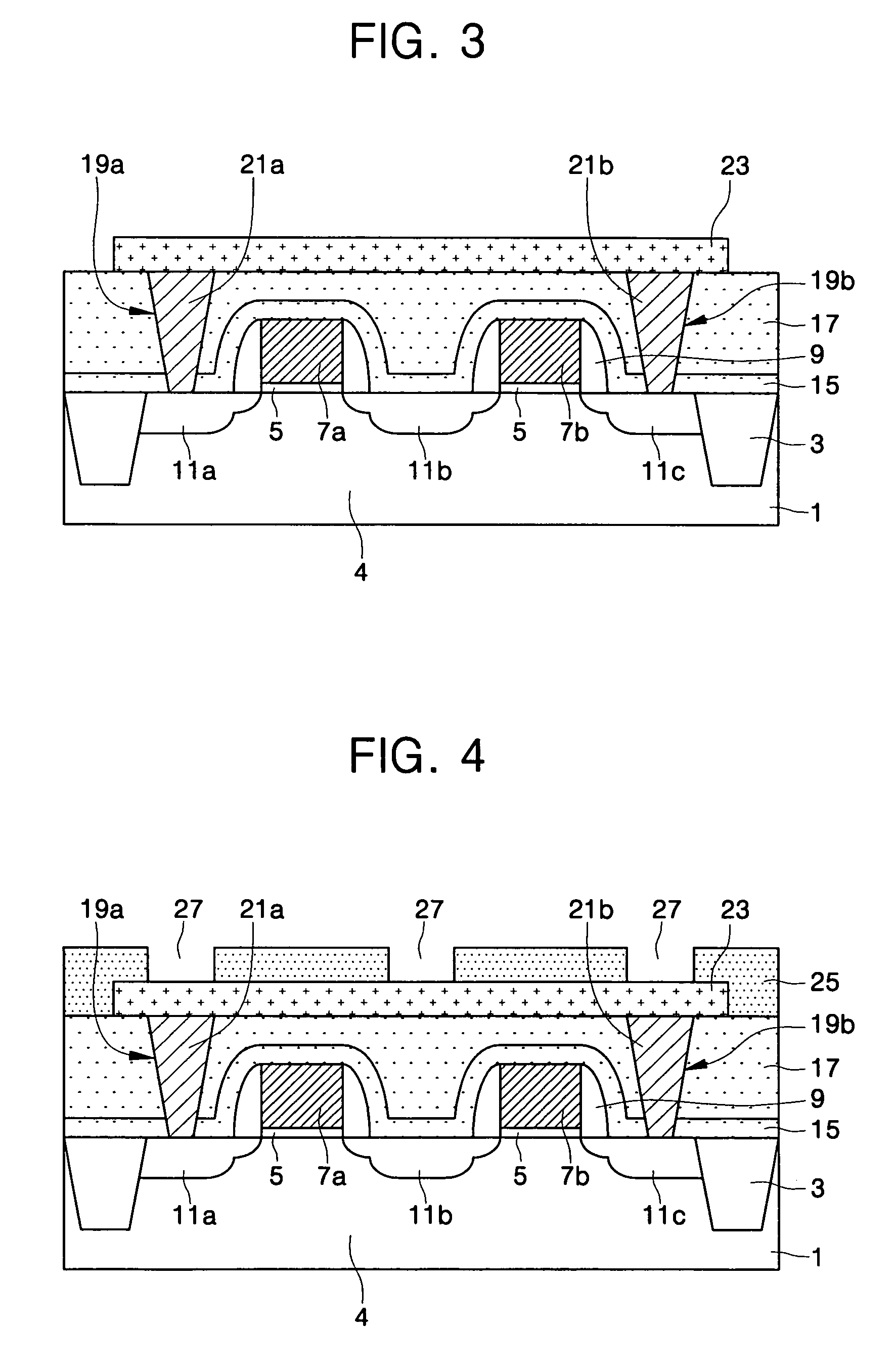

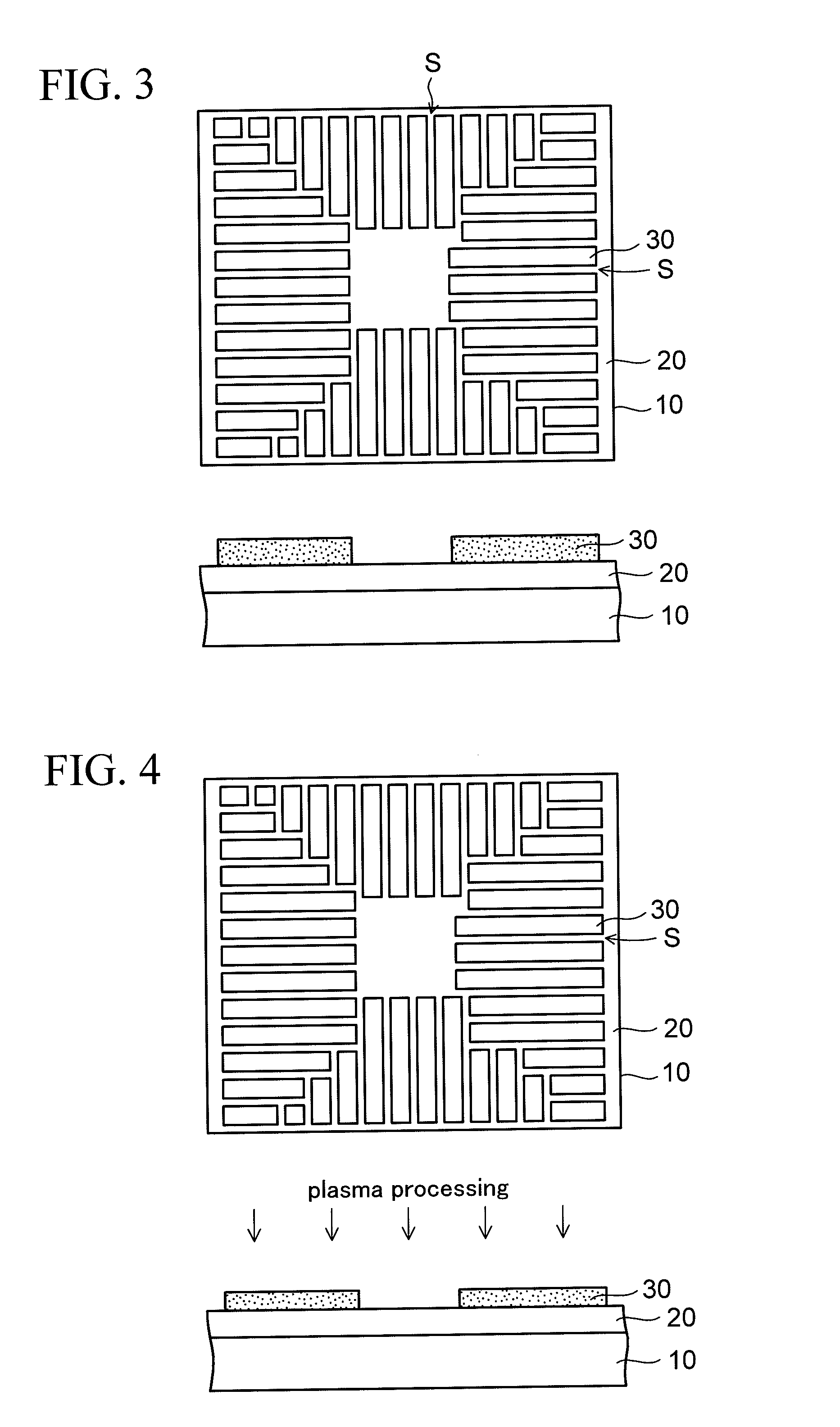

Methods of fabricating semiconductor device having capacitorless one-transistor memory cell

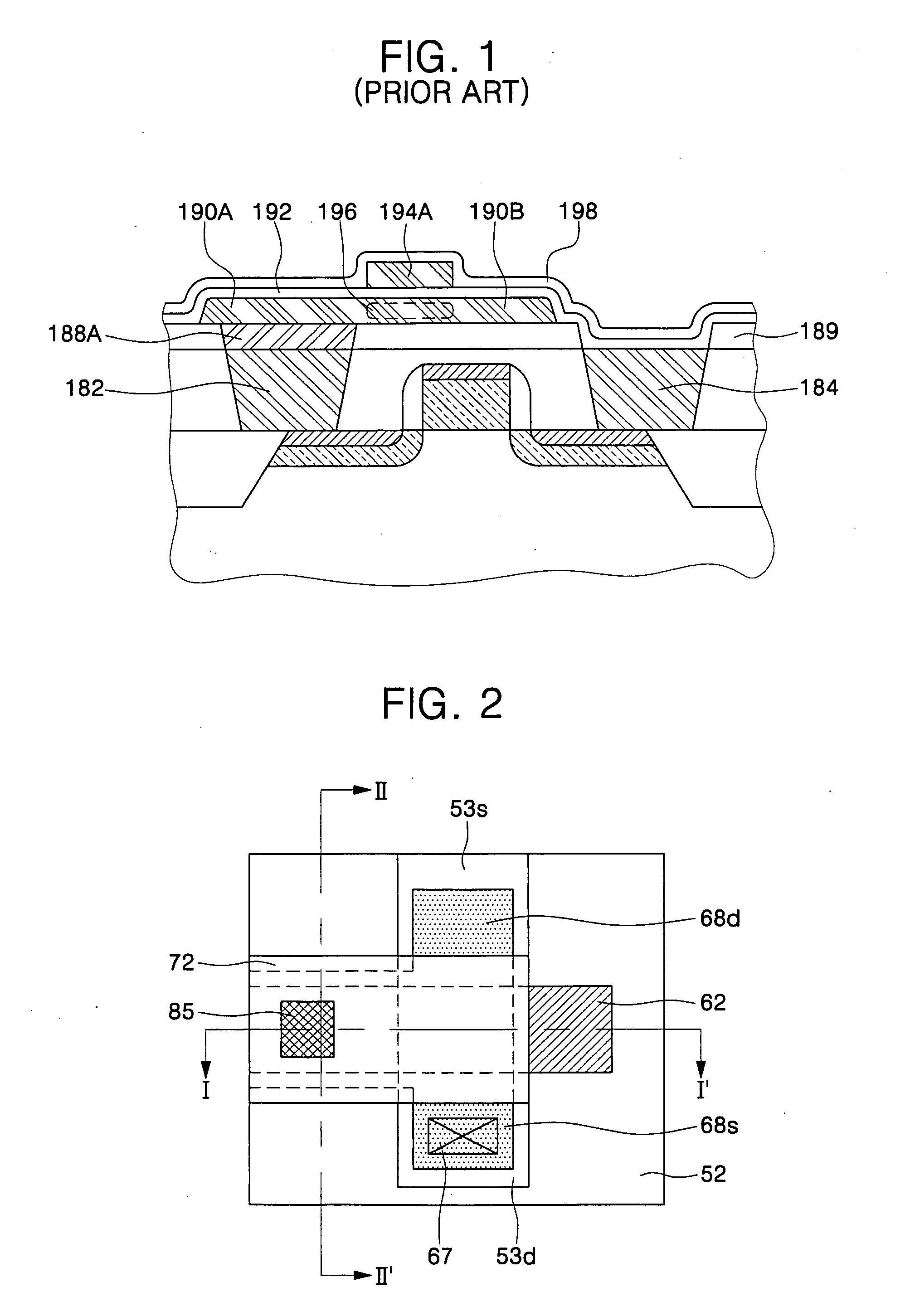

ActiveUS20100159650A1Improve rendering capabilitiesExcellent characteristicsTransistorSolid-state devicesBody PatterningImpurity

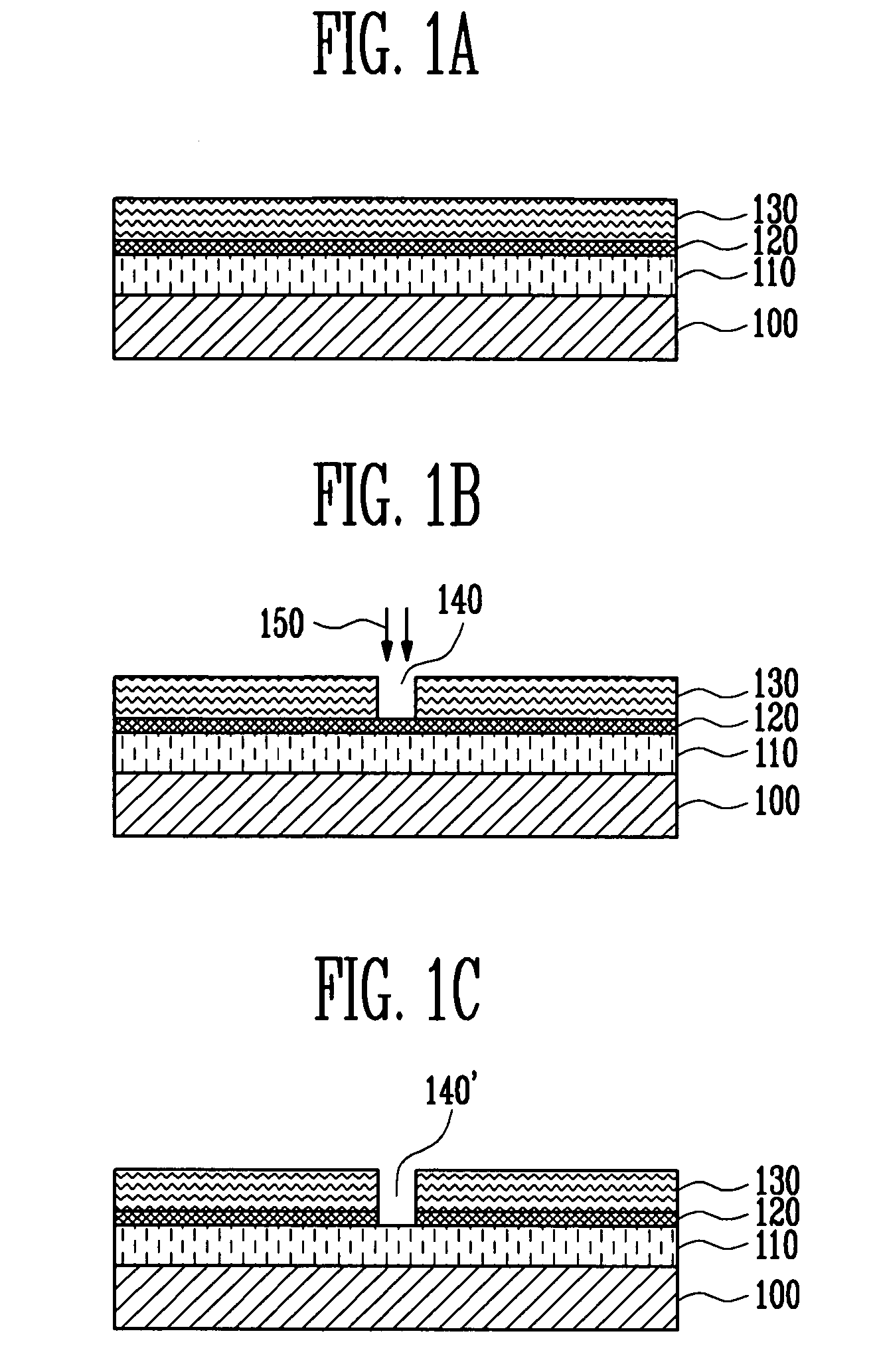

A method of fabricating a semiconductor device having a capacitorless one-transistor memory cell includes forming a first floating body pattern on a lower insulating layer of a substrate and a first gate pattern crossing over the first floating body pattern and covering sidewalls of the first floating body pattern is formed. The first floating body pattern at both sides of the first gate pattern is partially etched to form a protrusion portion extending between and above the partially etched regions, and first impurity regions are formed in the partially etched regions of the first floating body pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

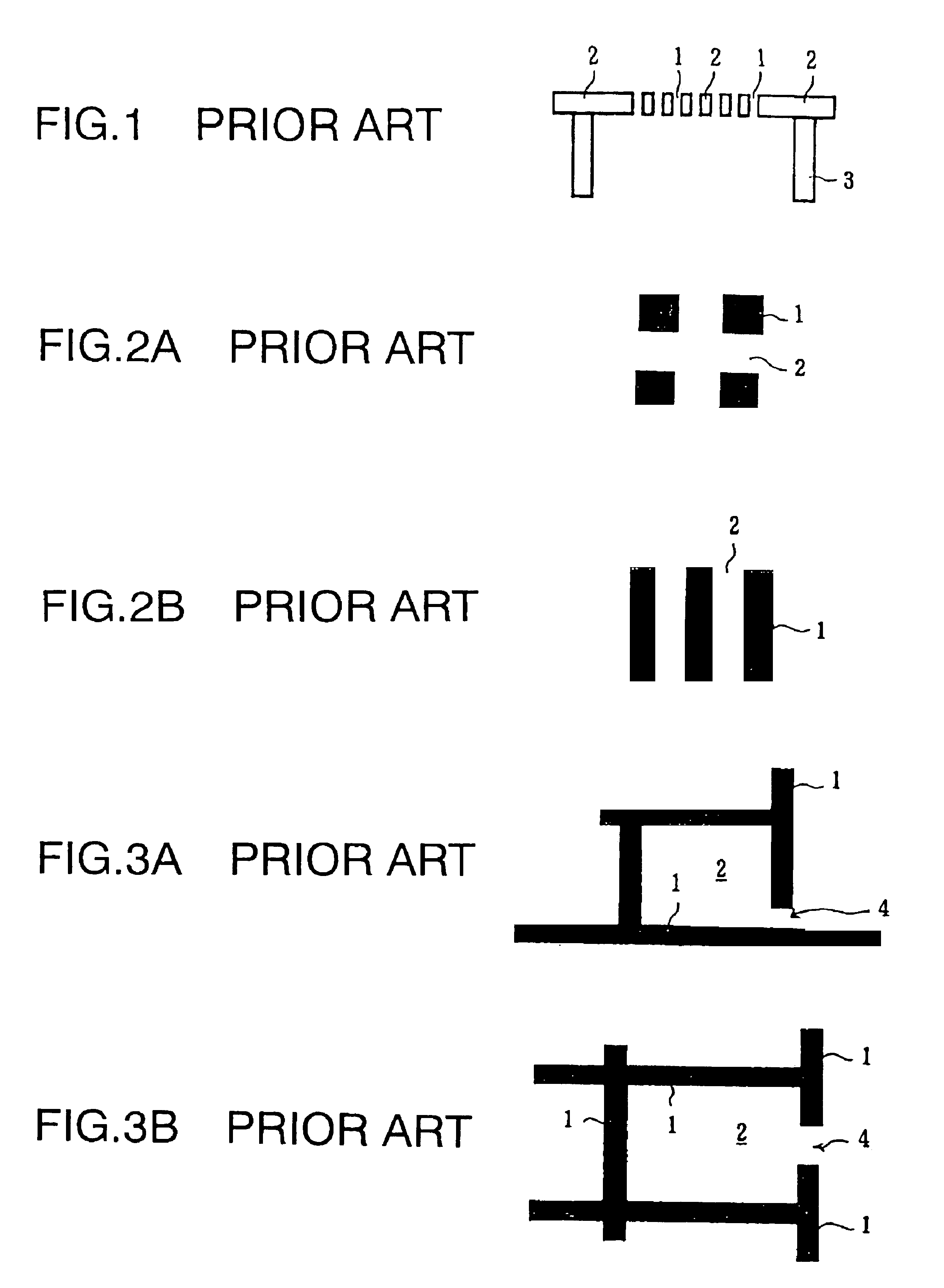

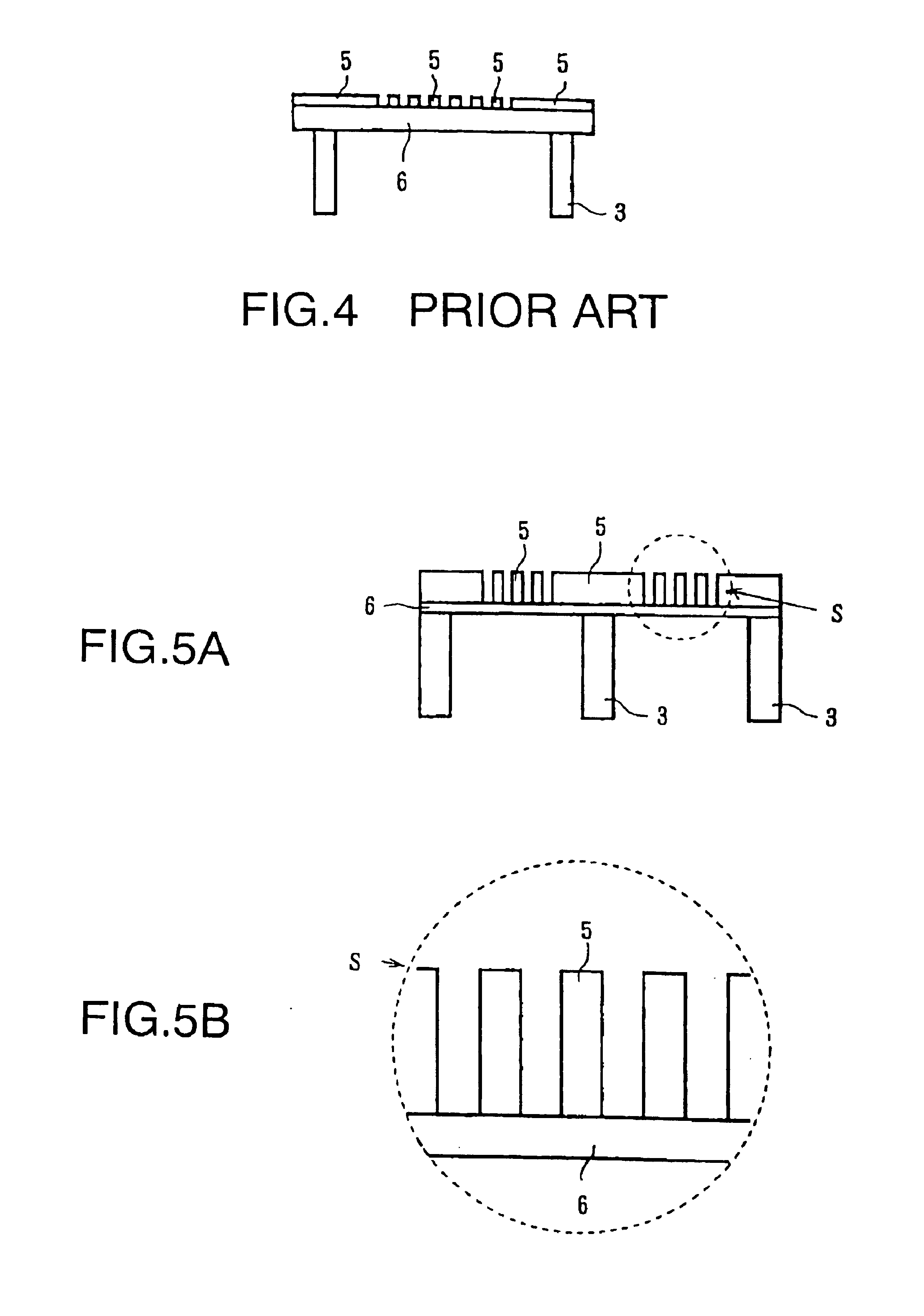

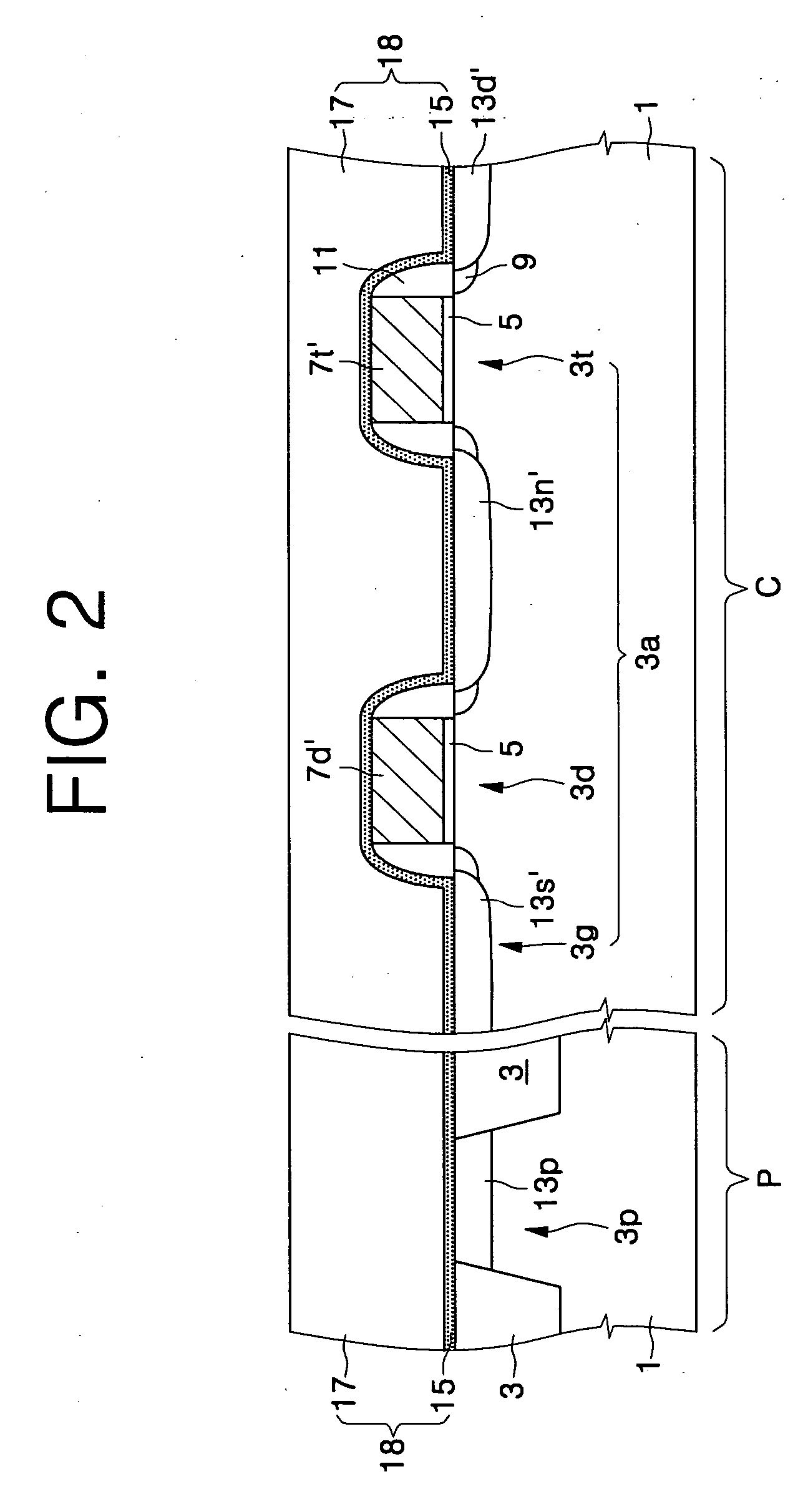

Electron beam drawing mask blank, electron beam drawing mask, and method of manufacturing the same

InactiveUS6812473B1Reduce overall chromatic aberrationReduce exposure timeElectric discharge tubesSemiconductor/solid-state device manufacturingBody PatterningFilm material

An electron beam drawing mask includes a pattern supporting film for transmitting an electron beam therethrough; an electron beam scattering body pattern formed over the pattern supporting film; and a support member for supporting the pattern supporting film and the electron beam scattering body pattern. The pattern supporting film has a film thickness of 0.005 to 0.2 micron, a film material density of 1.0 to 5.0 g / cm<3 >and an elastic modulus of 0.8x10<11 >Pa or higher. The electron beam scattering body pattern has a film thickness of 0.2 to 2 micron, a film material density of 1.0 to 5.0 g / cm<3>, and an elastic modulus of 0.8x10<11 >Pa or higher.

Owner:HOYA CORP

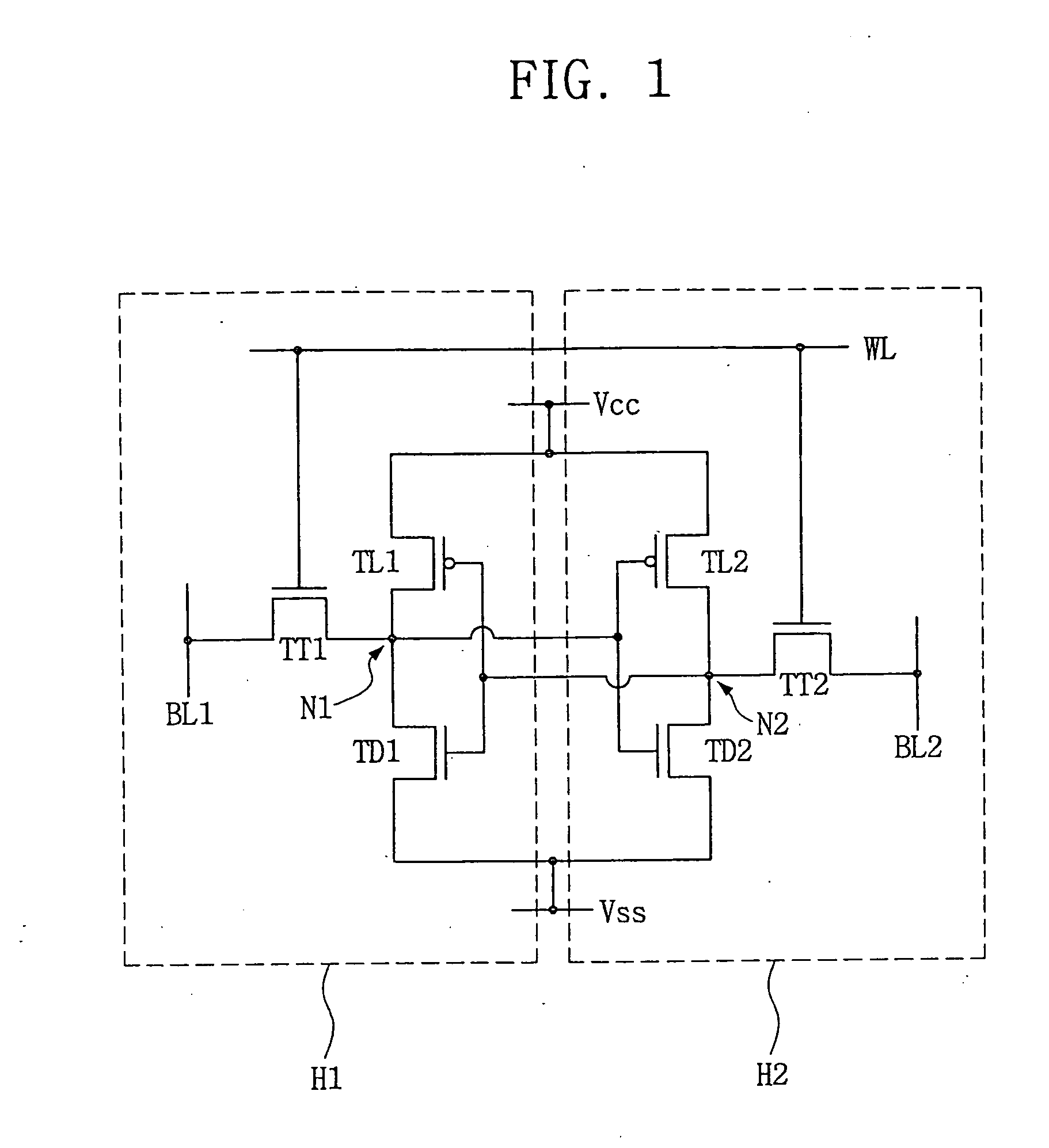

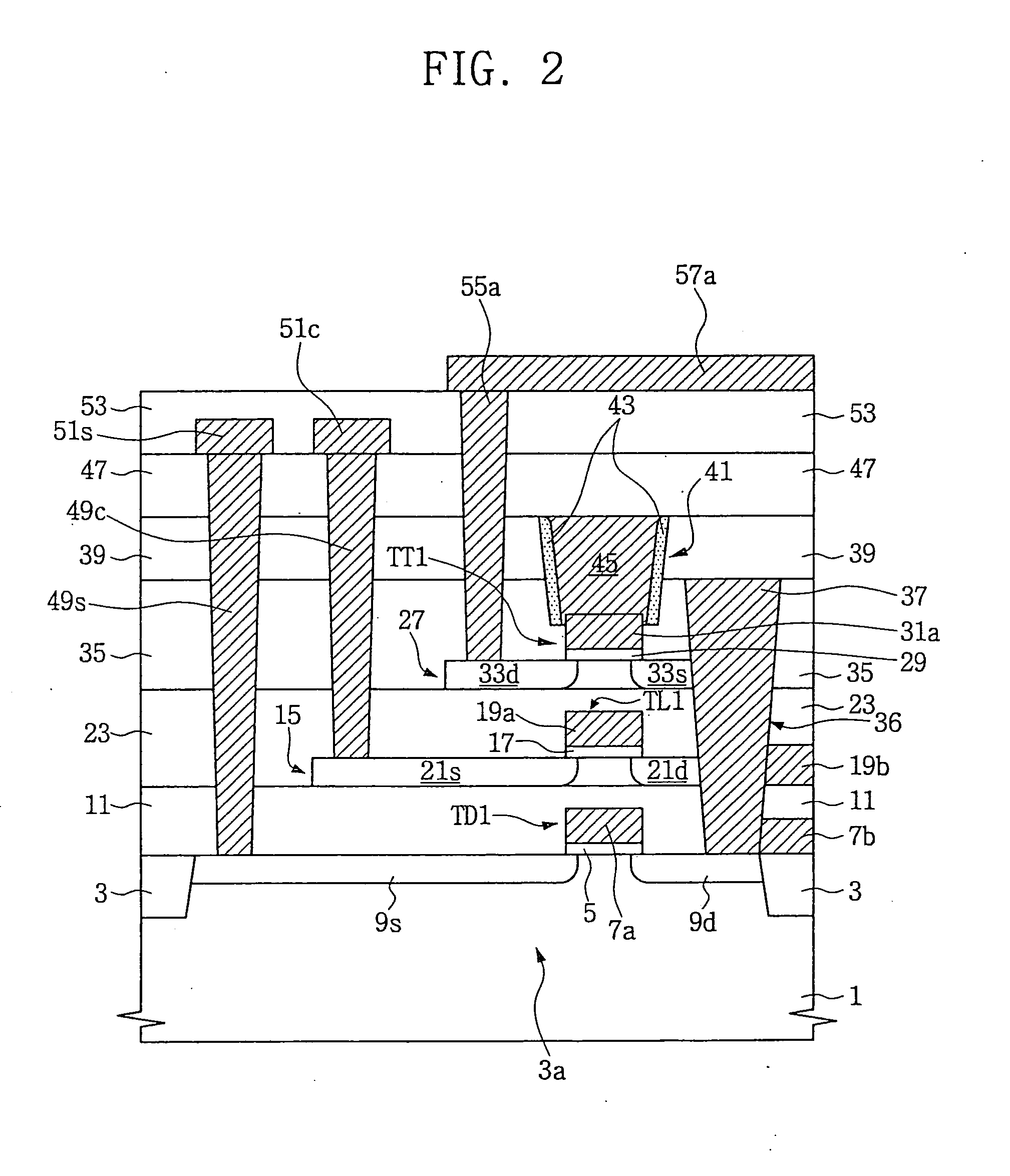

Methods of fabricating a semiconductor device having a node contact structure of a CMOS inverter

In one embodiment, an intrinsic single crystalline semiconductor plug is formed to pass through a lower insulating layer using a selective epitaxial growth process employing a node impurity region as a seed layer, and a single crystalline semiconductor body pattern is formed on the lower insulating layer using the intrinsic single crystalline semiconductor plug as a seed layer. When the recessed single crystalline semiconductor plug is doped with impurities having the same conductivity type as the node impurity region, a peripheral impurity region is prevented from being counter-doped. As a result, it is possible to implement a high performance semiconductor device that requires a single crystalline thin film transistor as well as a node contact structure with ohmic contact.

Owner:SAMSUNG ELECTRONICS CO LTD

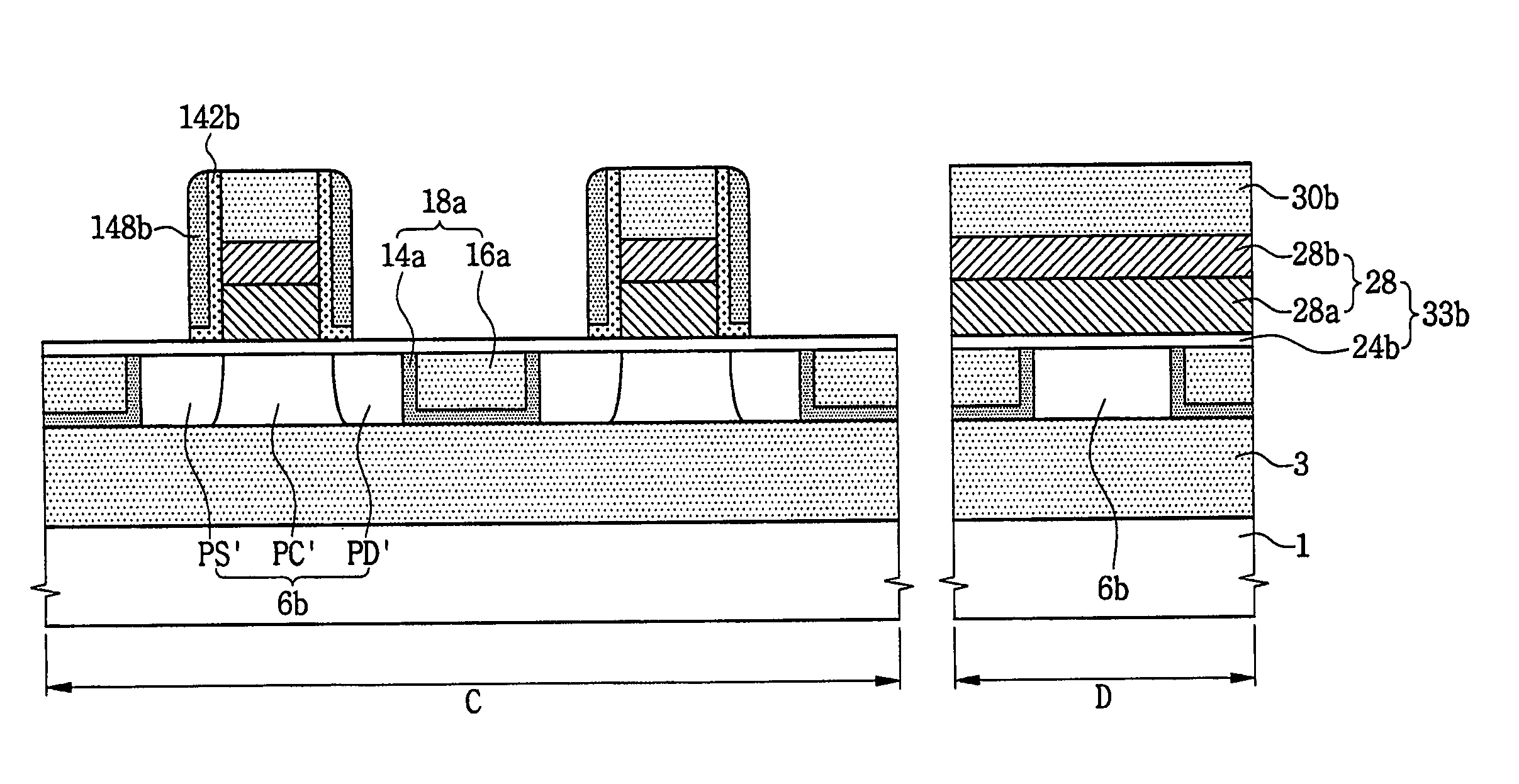

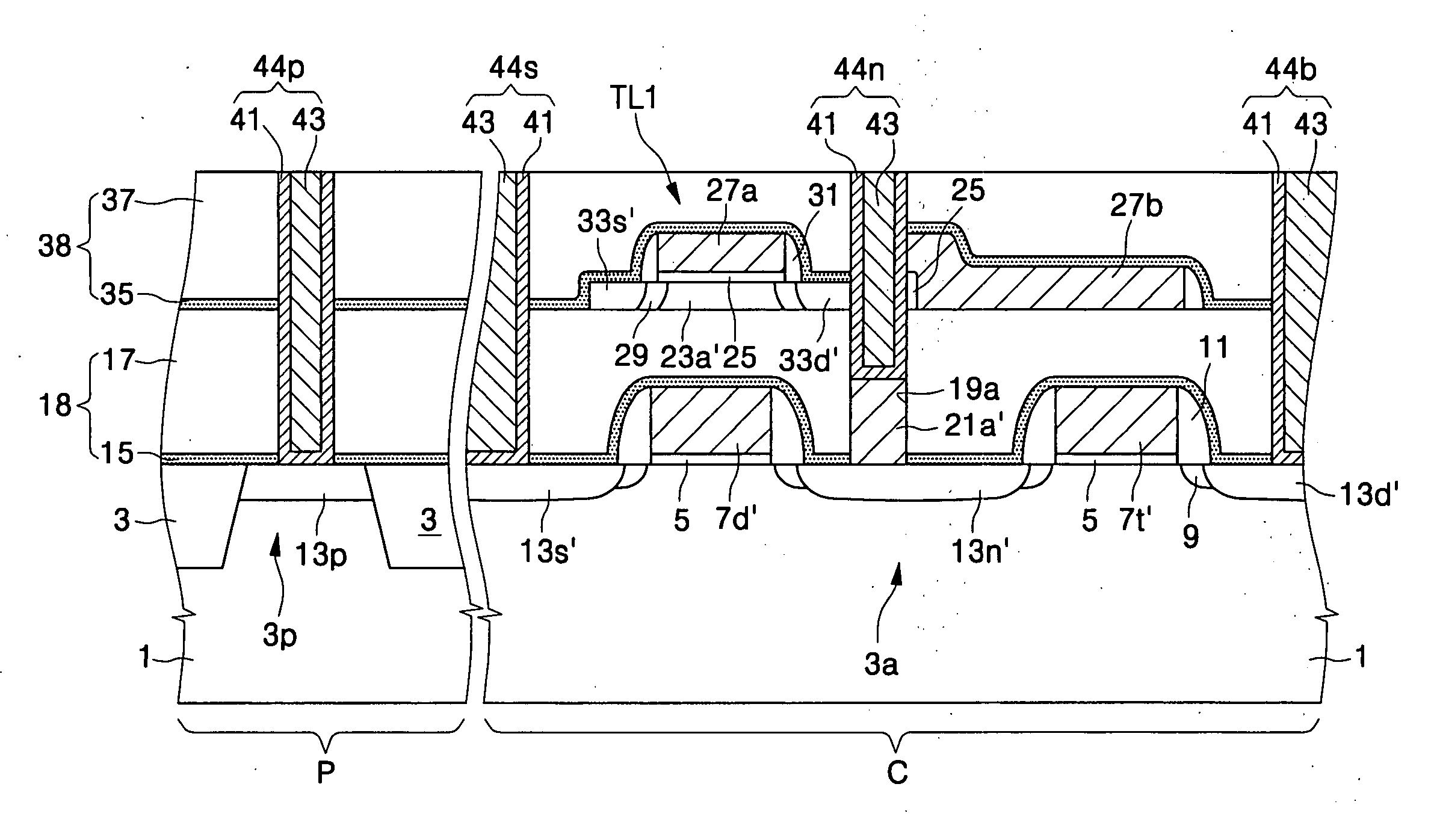

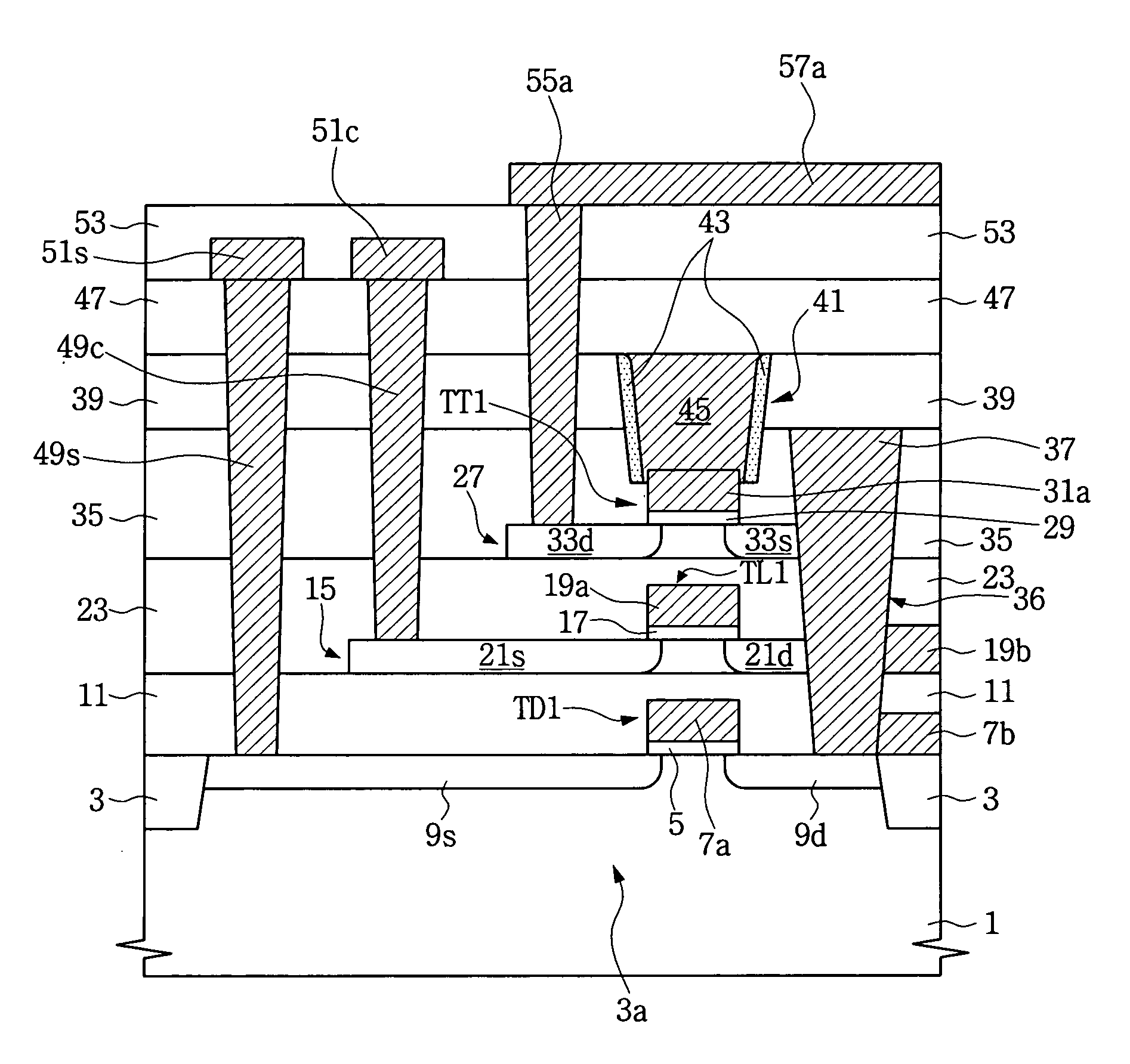

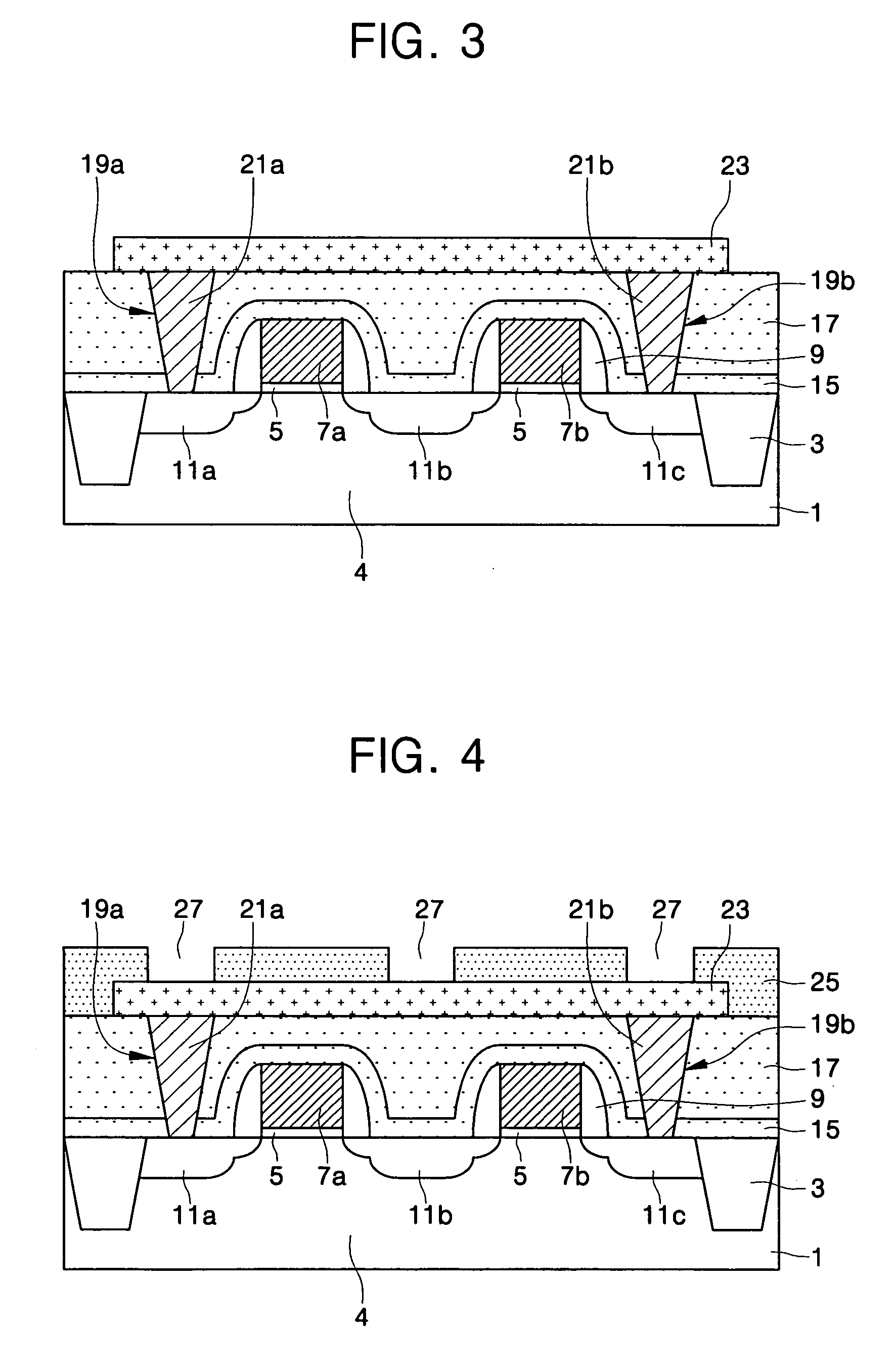

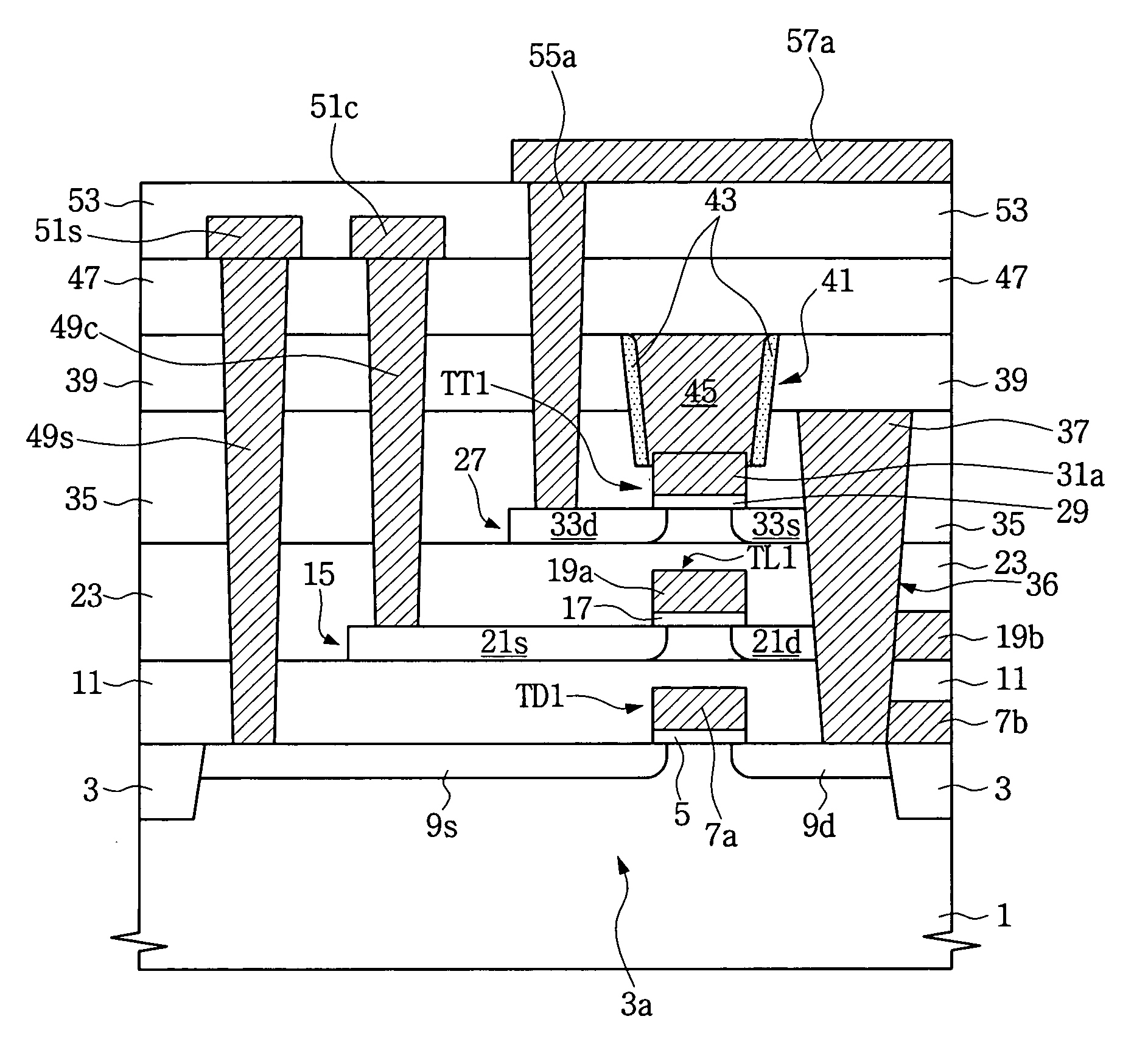

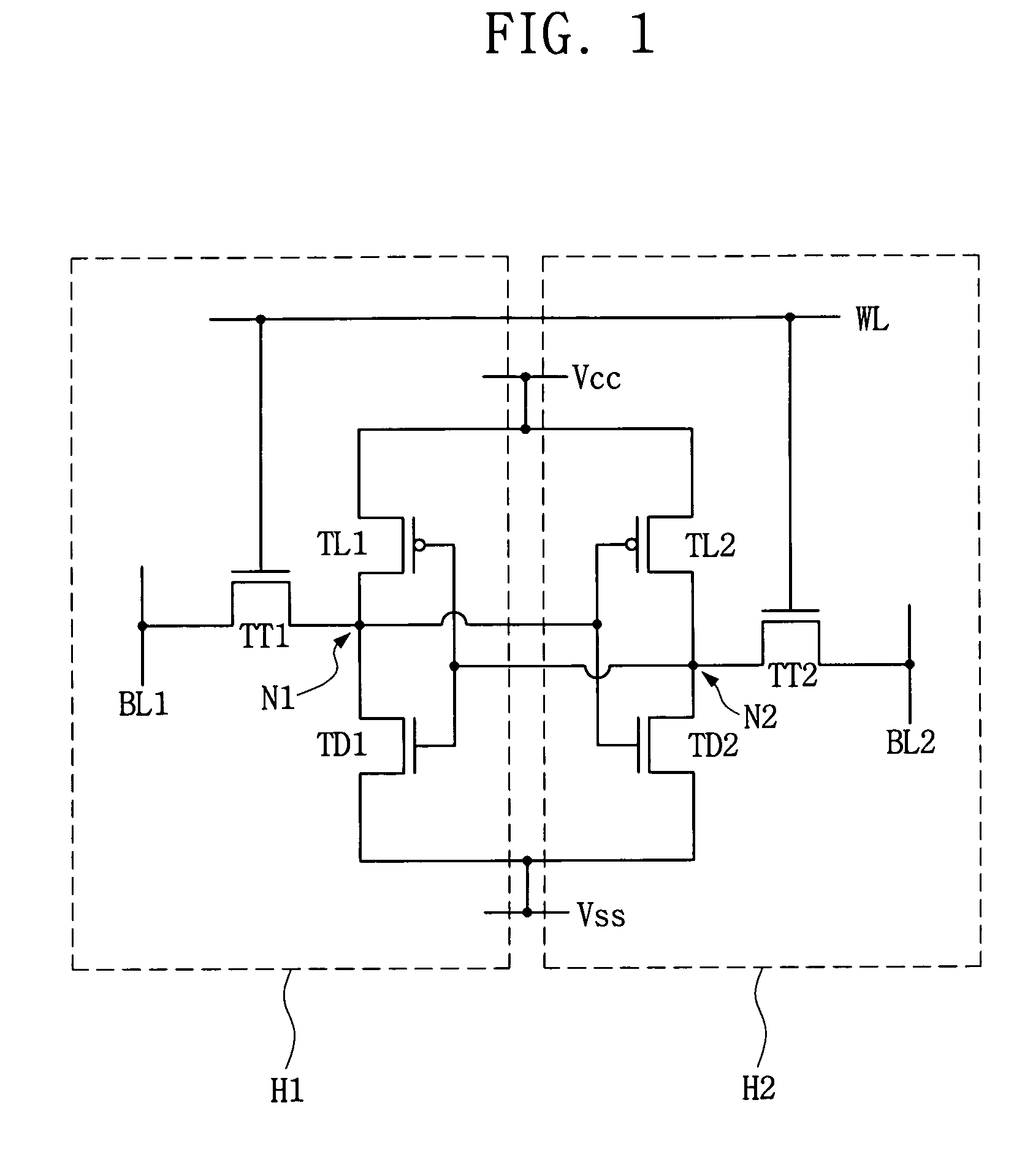

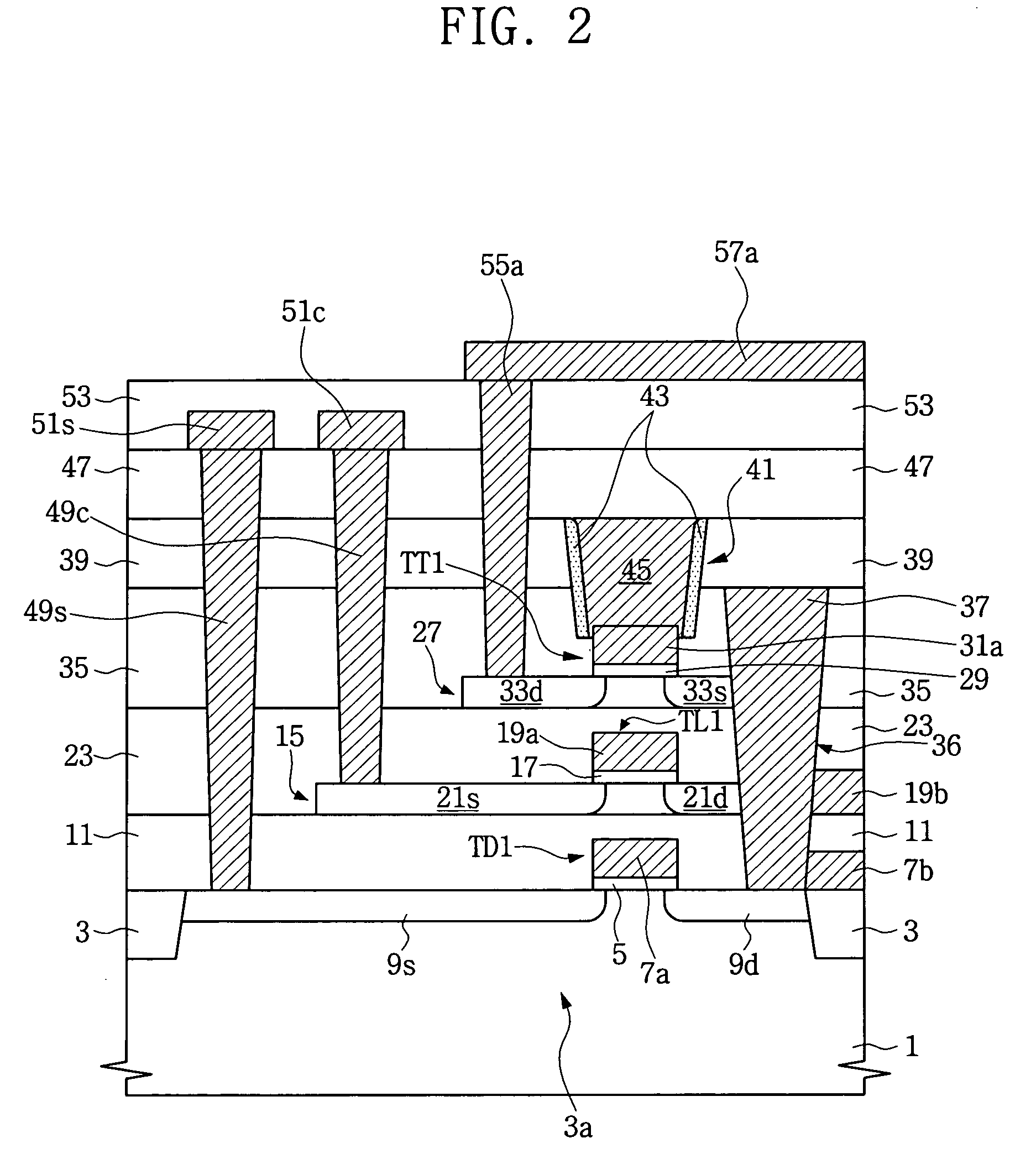

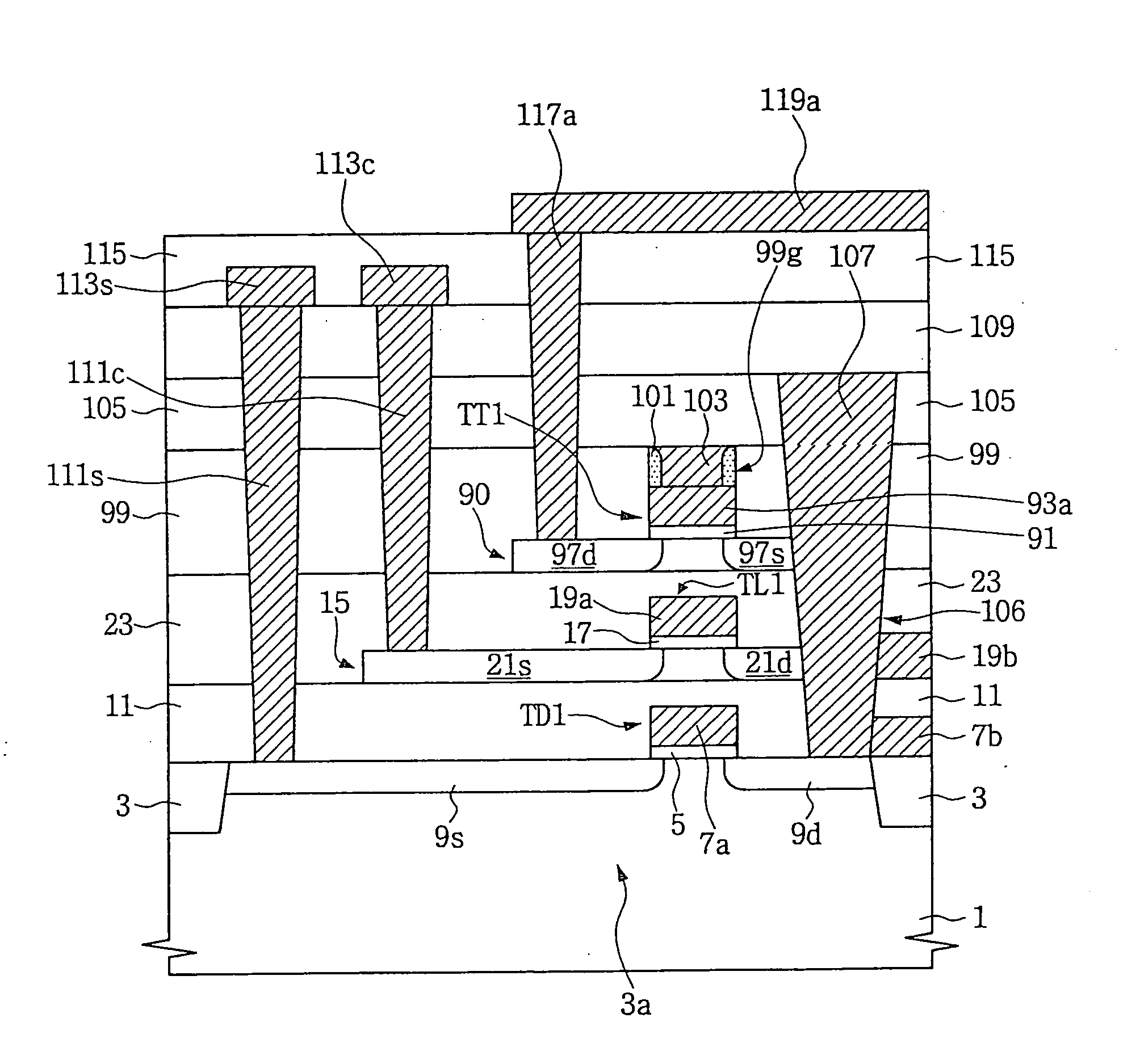

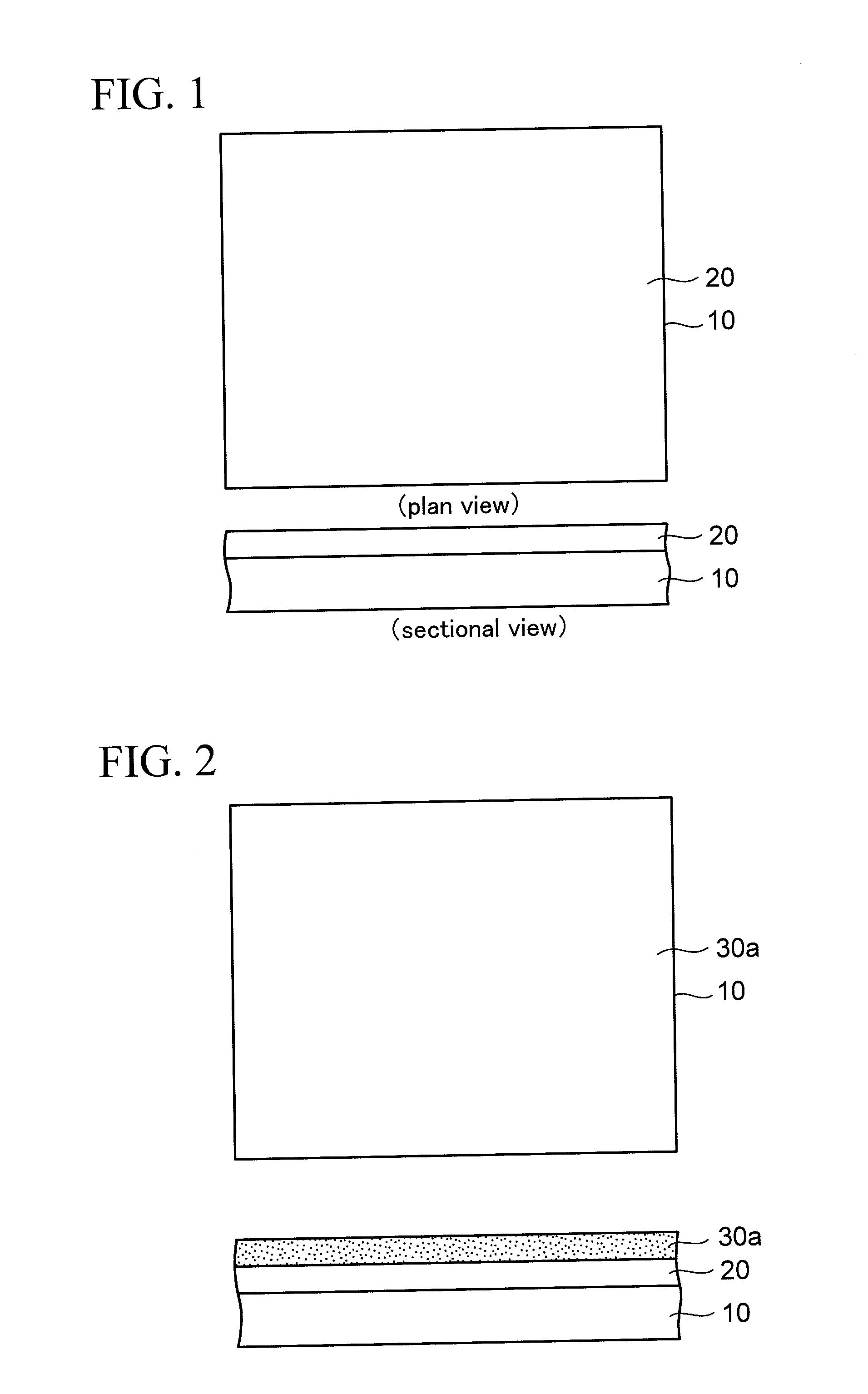

Semiconductor device having a plurality of stacked transistors and method of fabricating the same

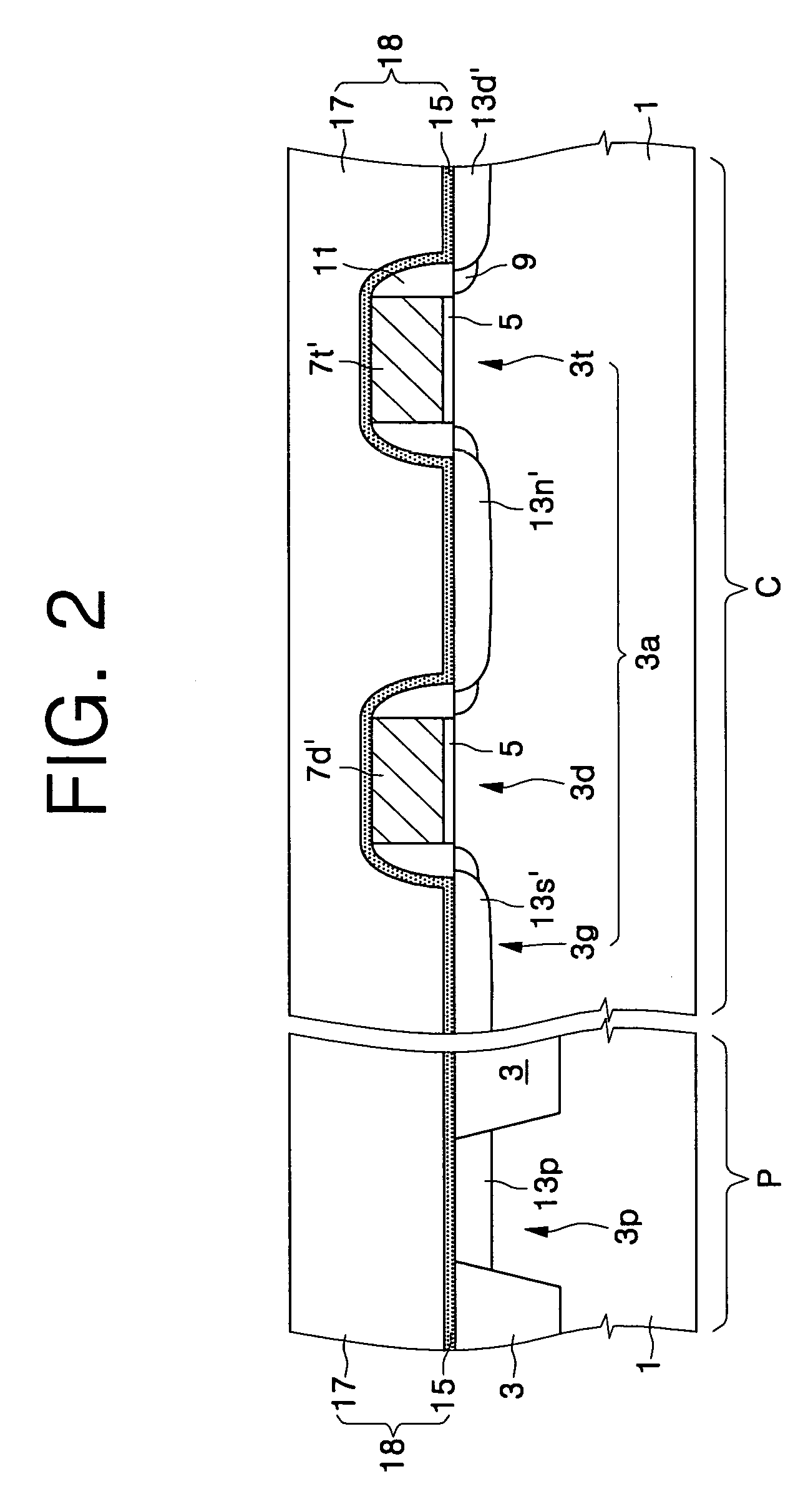

A semiconductor device according to example embodiments may have a plurality of stacked transistors. The semiconductor device may have a lower insulating layer formed on a semiconductor substrate and an upper channel body pattern formed on the lower insulating layer. A source region and a drain region may be formed within the upper channel body pattern, and a non-metal transfer gate electrode may be disposed on the upper channel body pattern between the source and drain regions. The non-metal transfer gate electrode, the upper channel body pattern, and the lower insulating layer may be covered by an intermediate insulating layer. A metal word line may be disposed within the intermediate insulating layer to contact at least an upper surface of the non-metal transfer gate electrode. An insulating spacer may be disposed on a sidewall of the metal word line. A metal node plug may be disposed within the intermediate insulating layer and the lower insulating layer to contact the source region of the upper channel body pattern. Example embodiments also relate to a method of fabricating the above semiconductor device.

Owner:SAMSUNG ELECTRONICS CO LTD

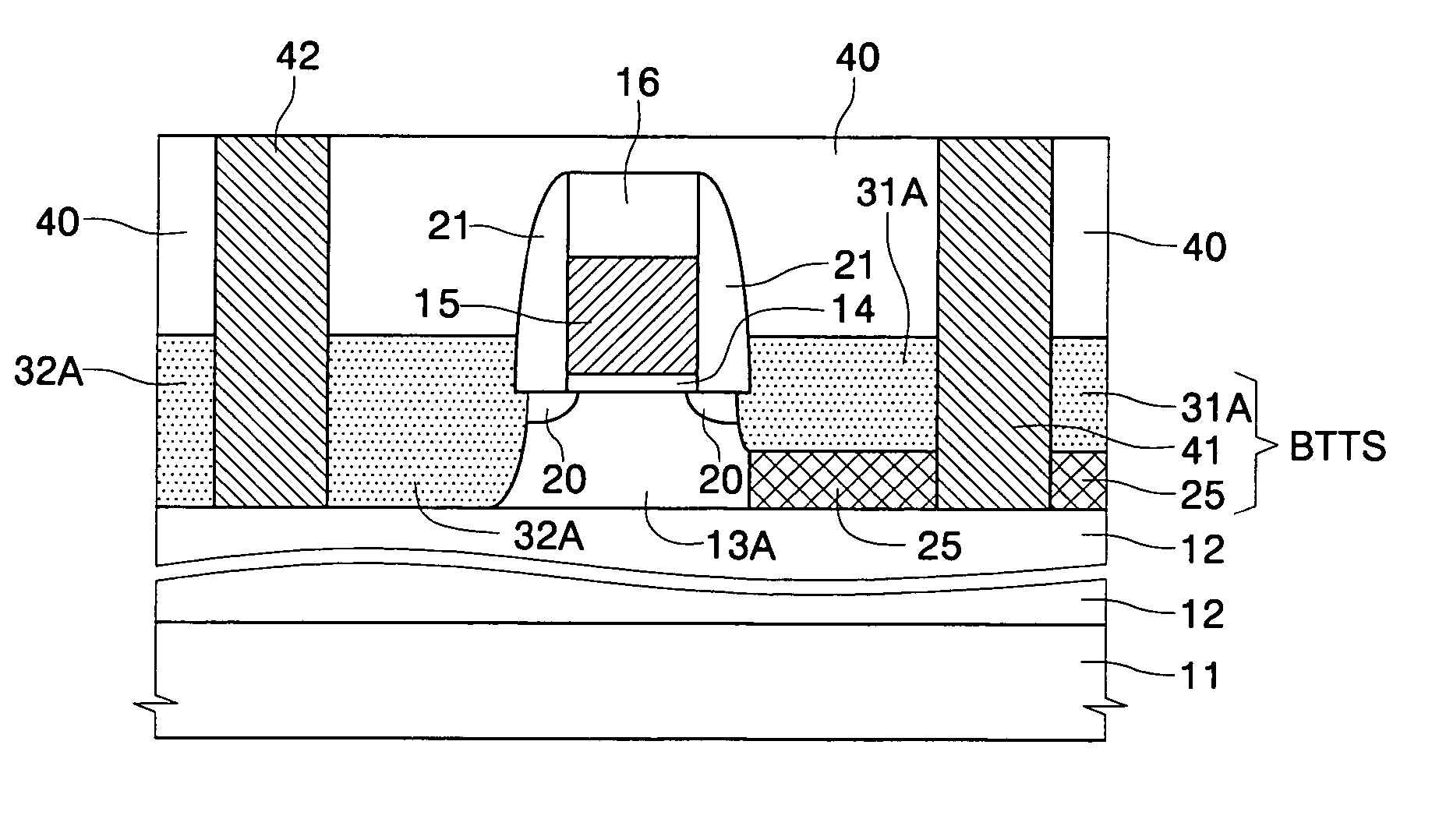

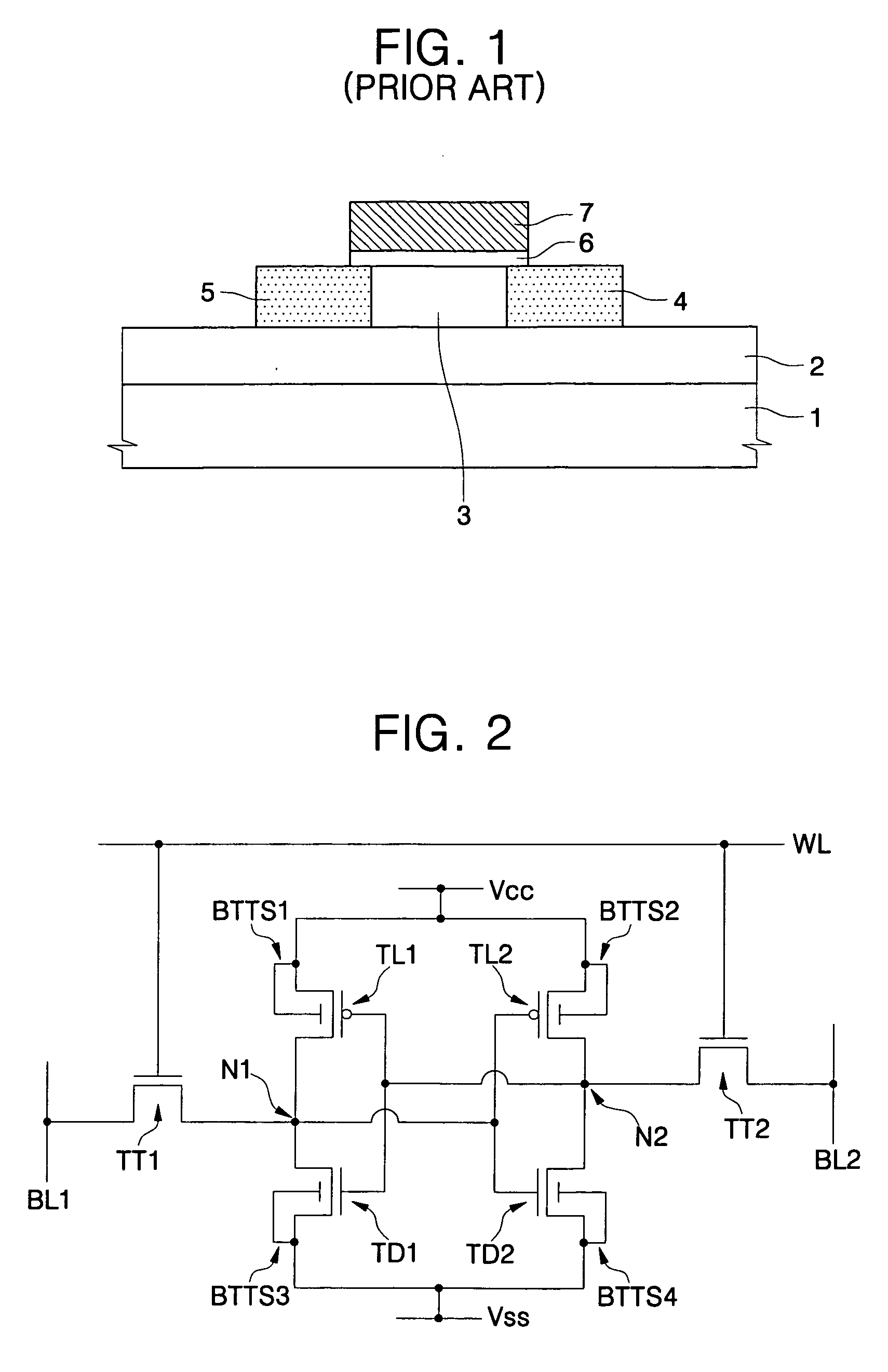

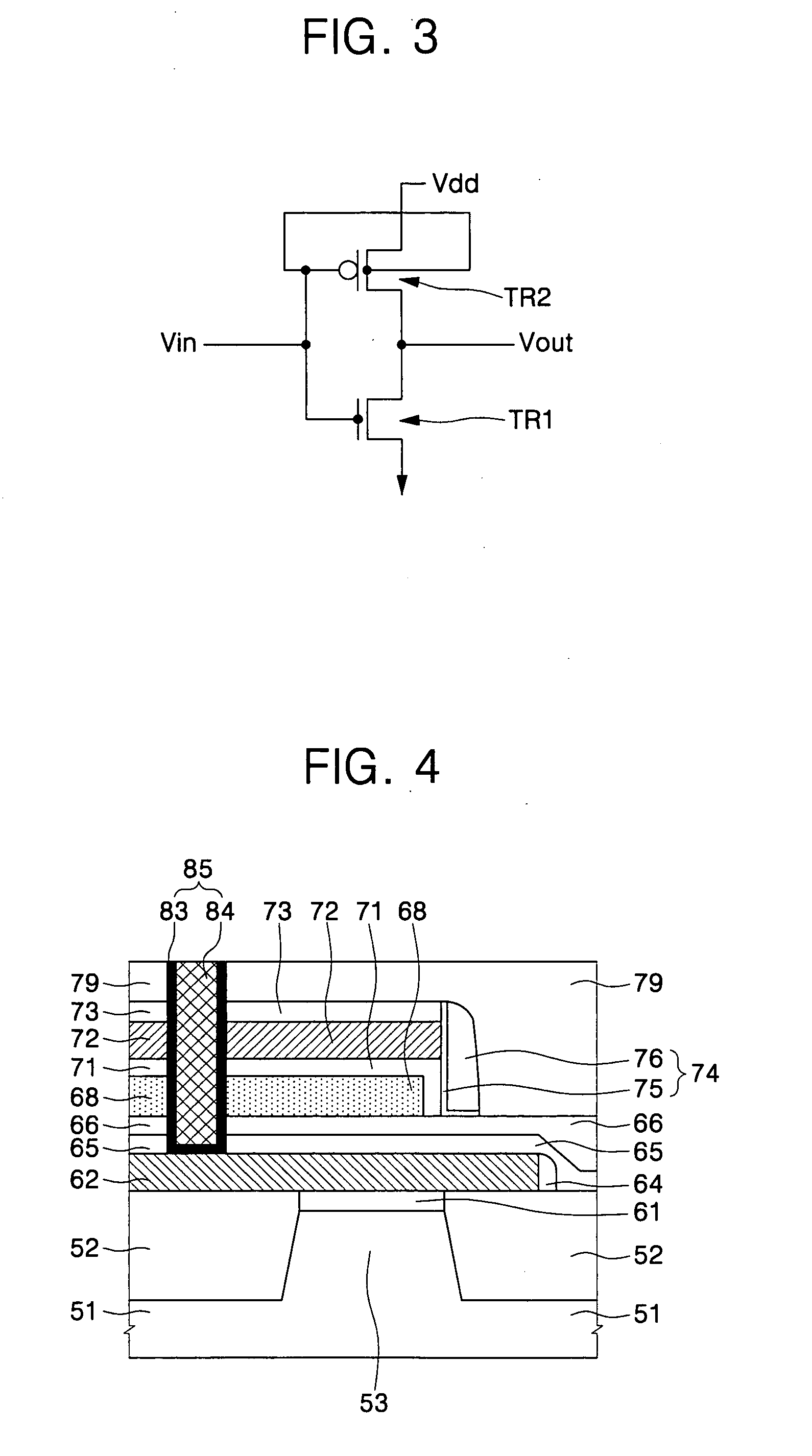

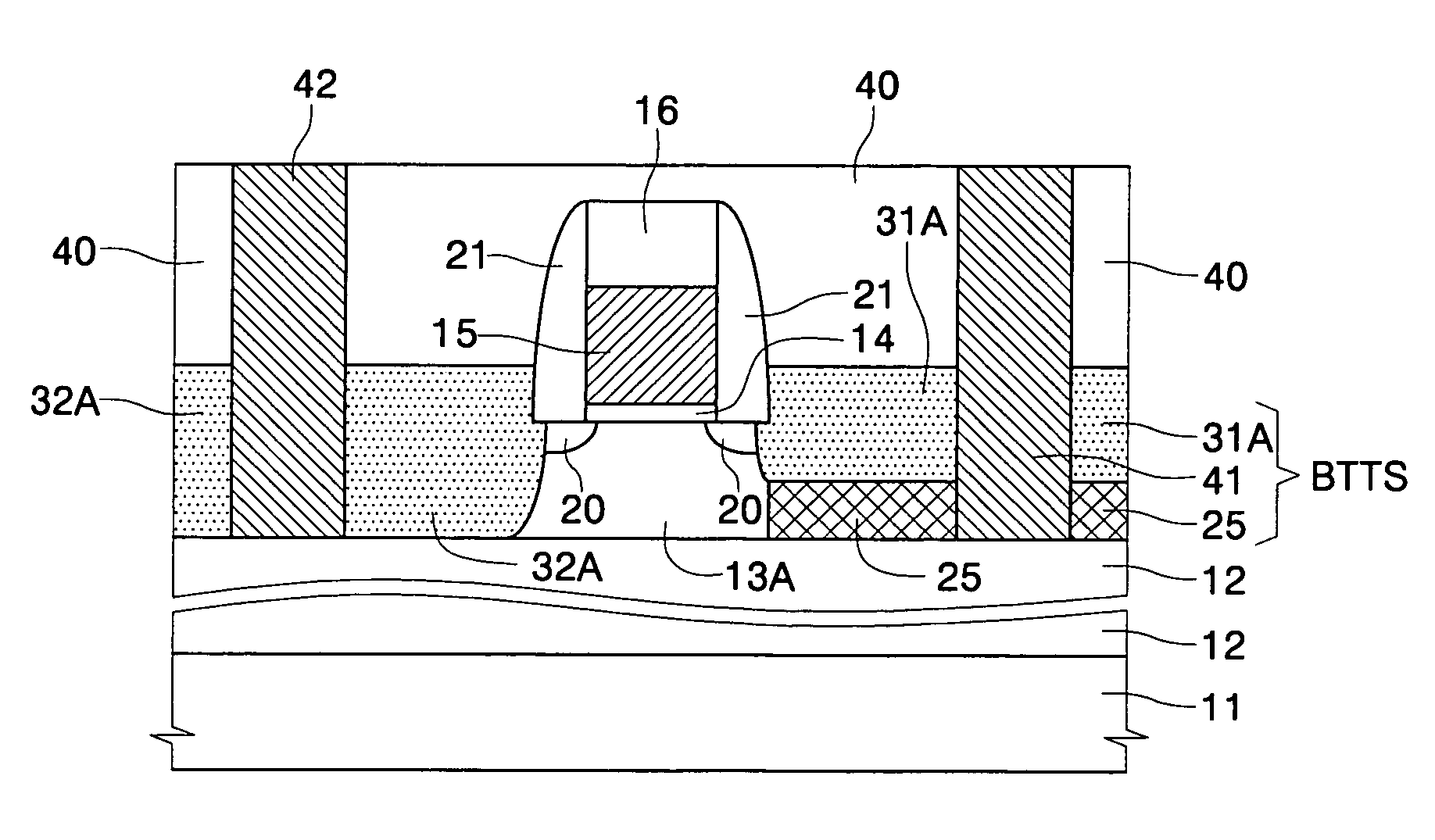

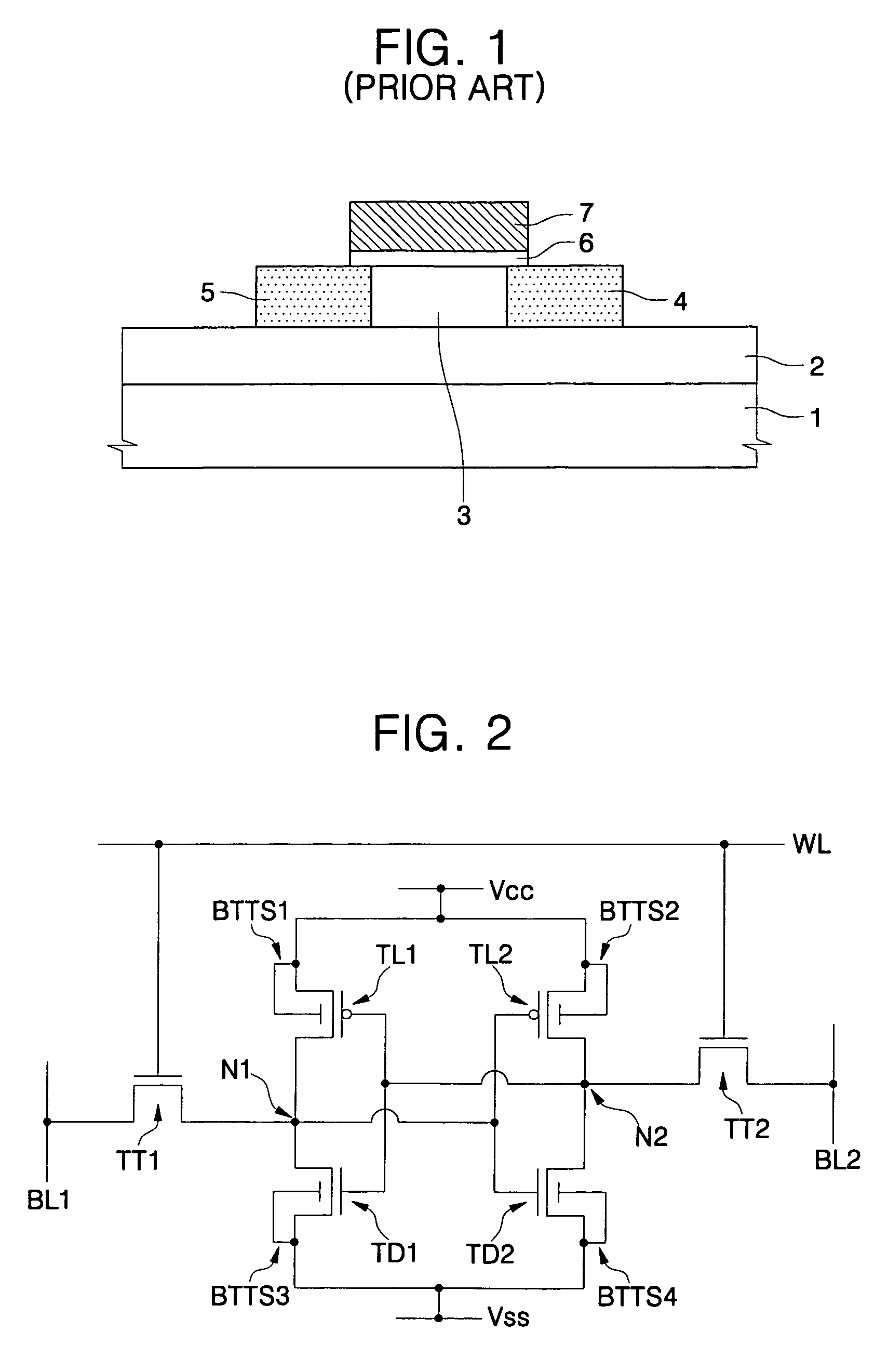

Body-tied-to-source MOSFETs with asymmetrical source and drain regions and methods of fabricating the same

A metal oxide semiconductor field effect transistor (MOSFET) includes a body pattern of a first conductivity type disposed on an insulating layer. A gate electrode is disposed on the body pattern. A drain region of a second conductivity type is disposed on the insulating layer and having a sidewall in contact with a first sidewall of the body pattern. An impurity-doped region of the first conductivity type is disposed on the insulating layer and having a sidewall in contact with a second sidewall of the body pattern. The MOSFET further includes a source region of the second conductivity type disposed on the impurity-doped region and having a sidewall in contact with the second sidewall of the body pattern, and a contact plug extending through the source region to contact the impurity-doped region.

Owner:SAMSUNG ELECTRONICS CO LTD

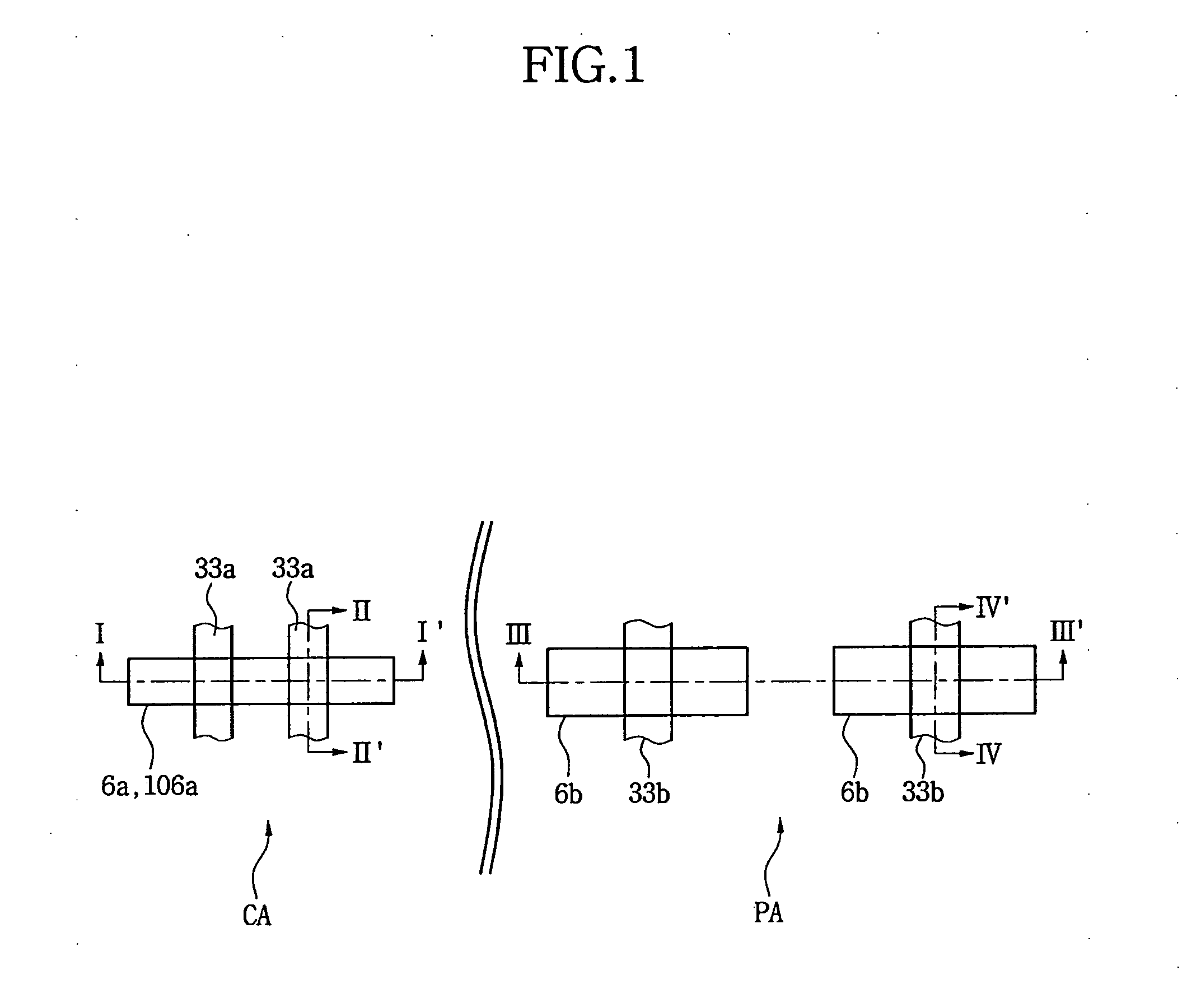

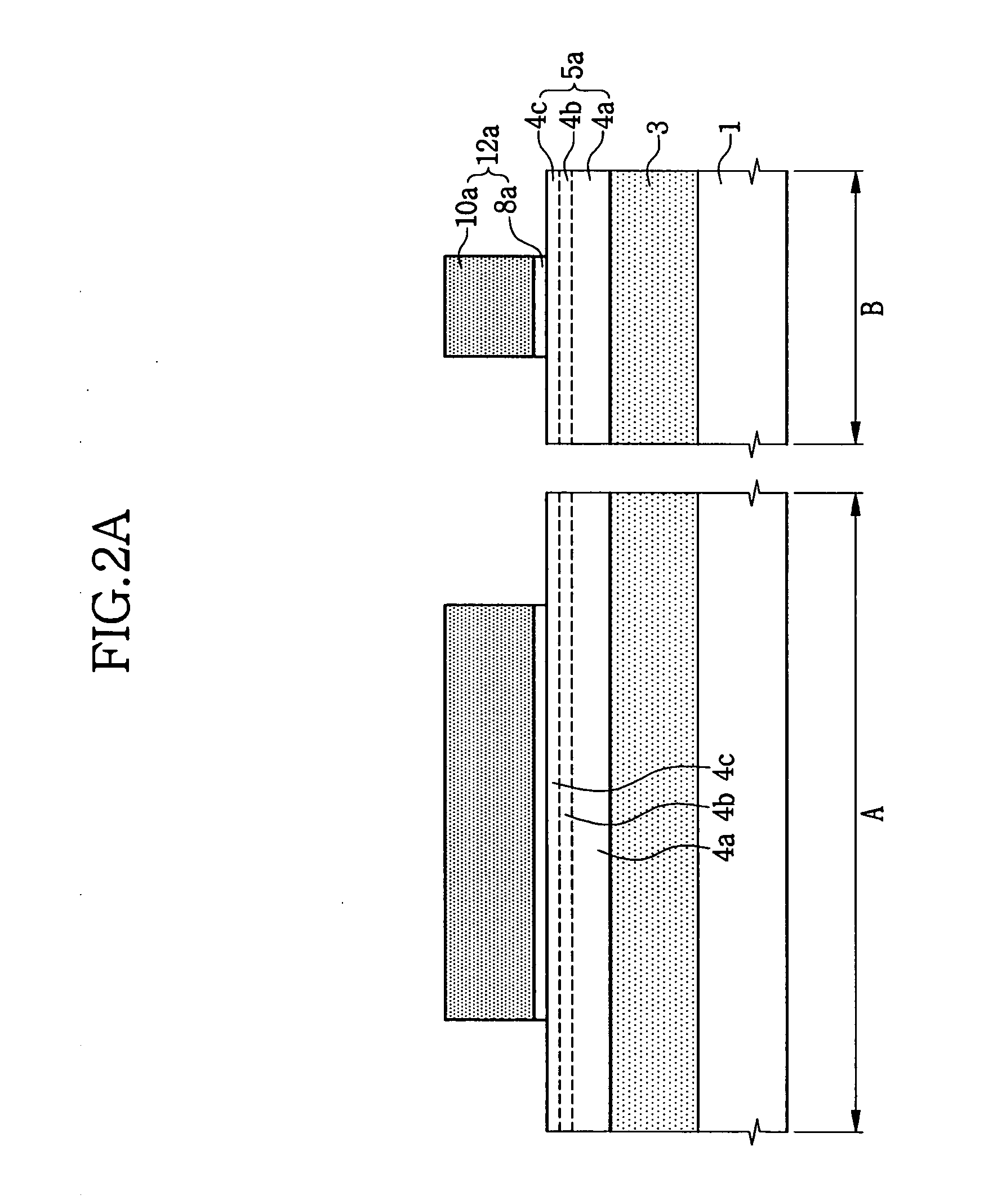

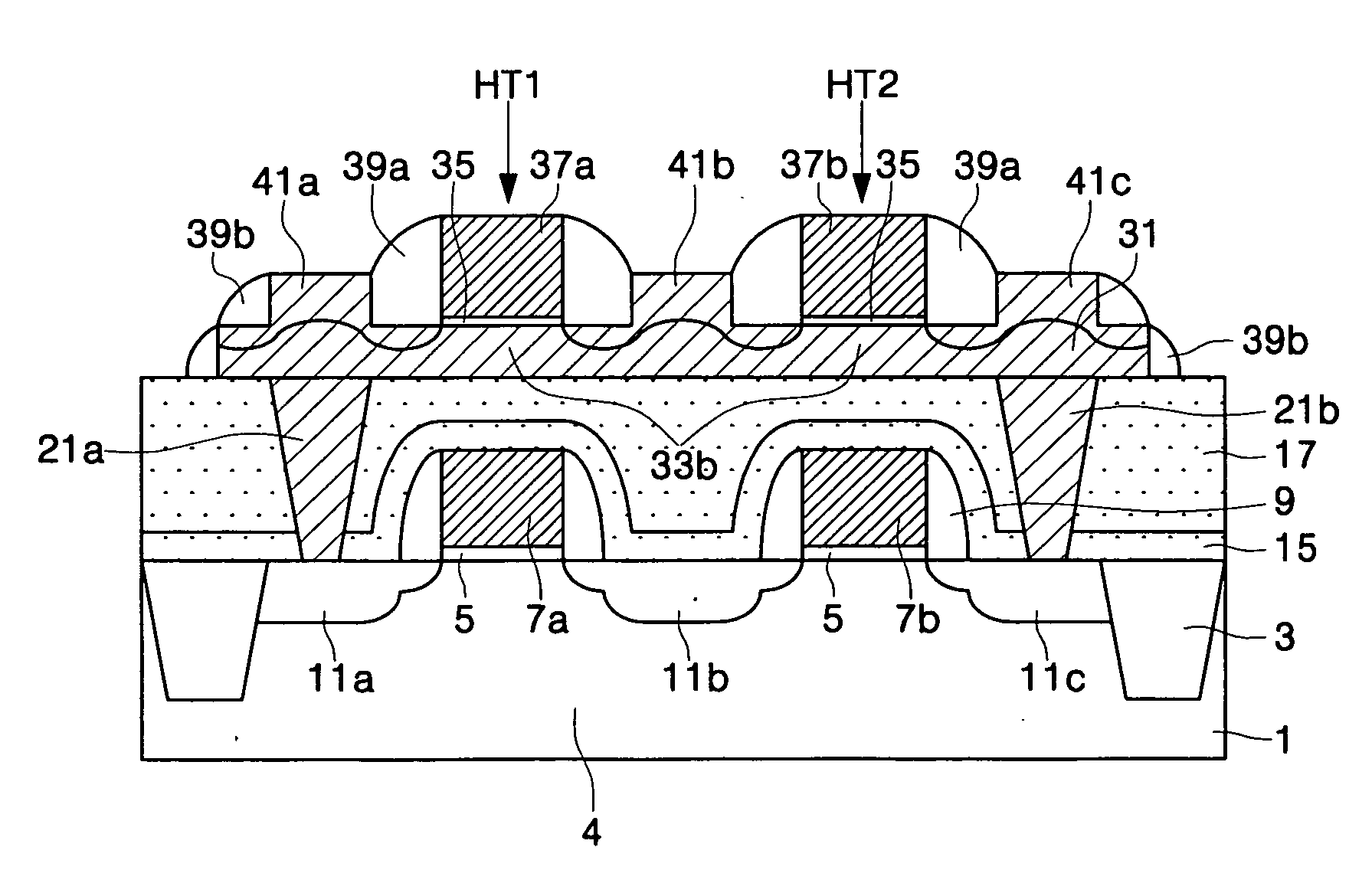

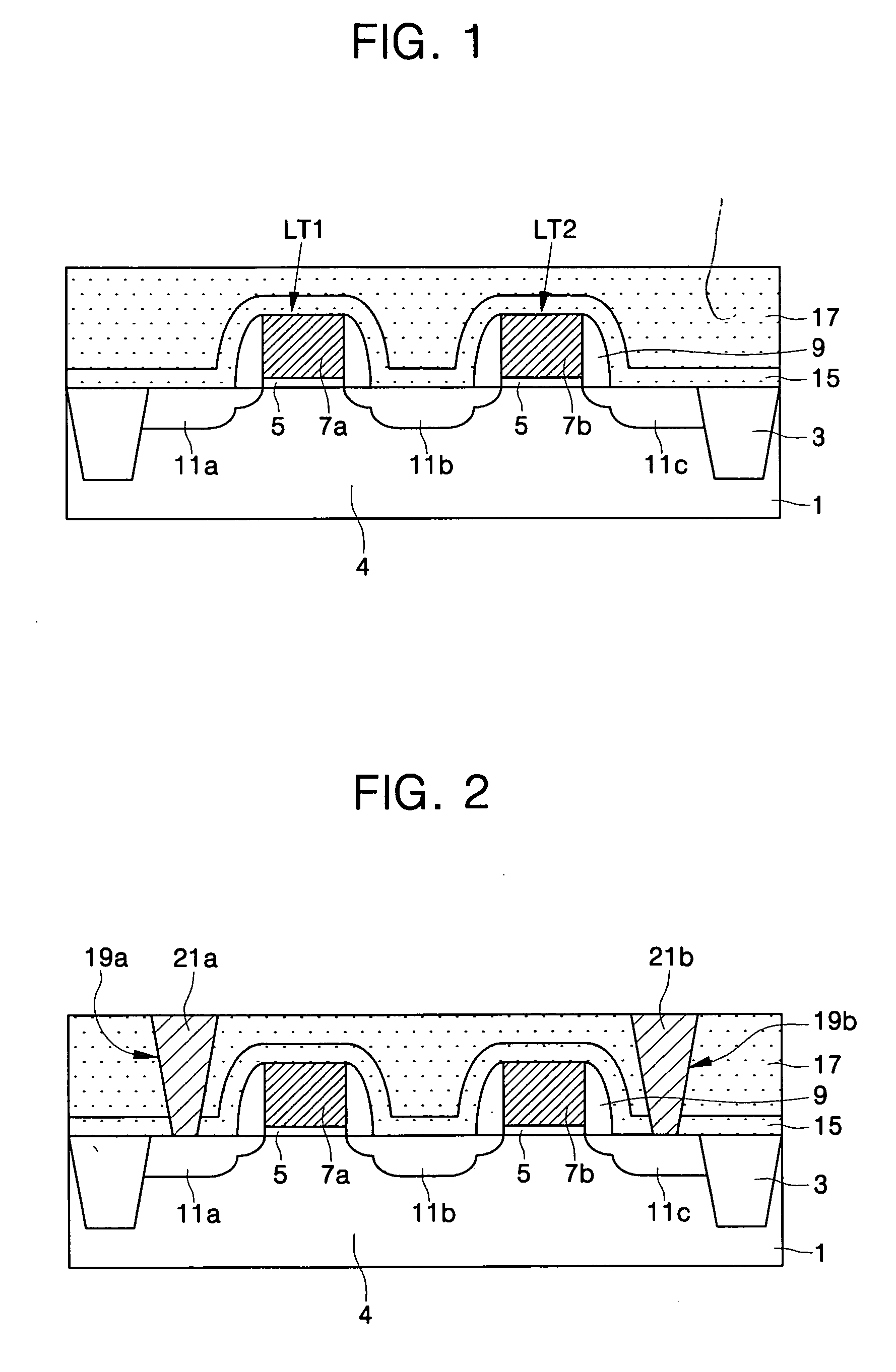

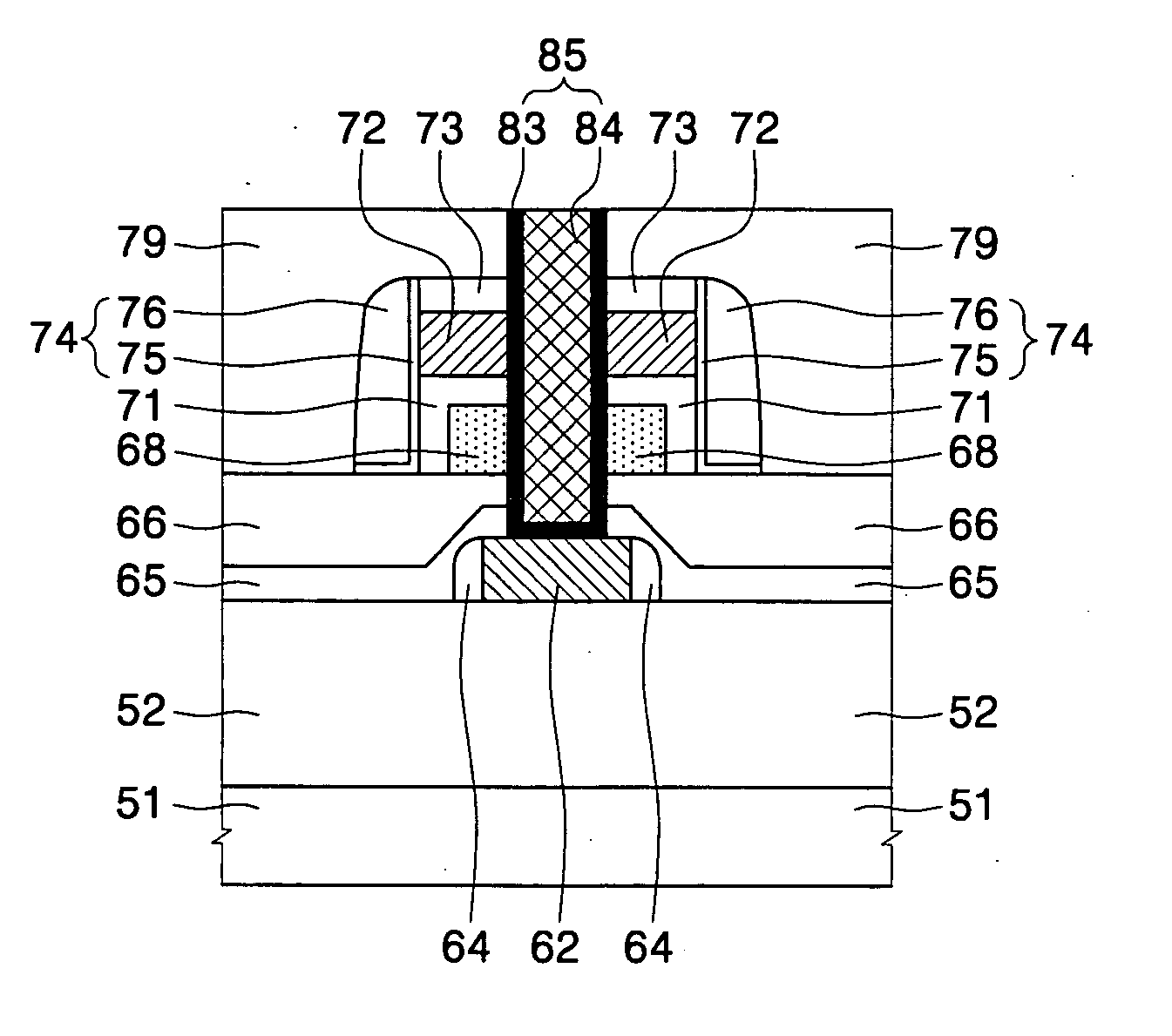

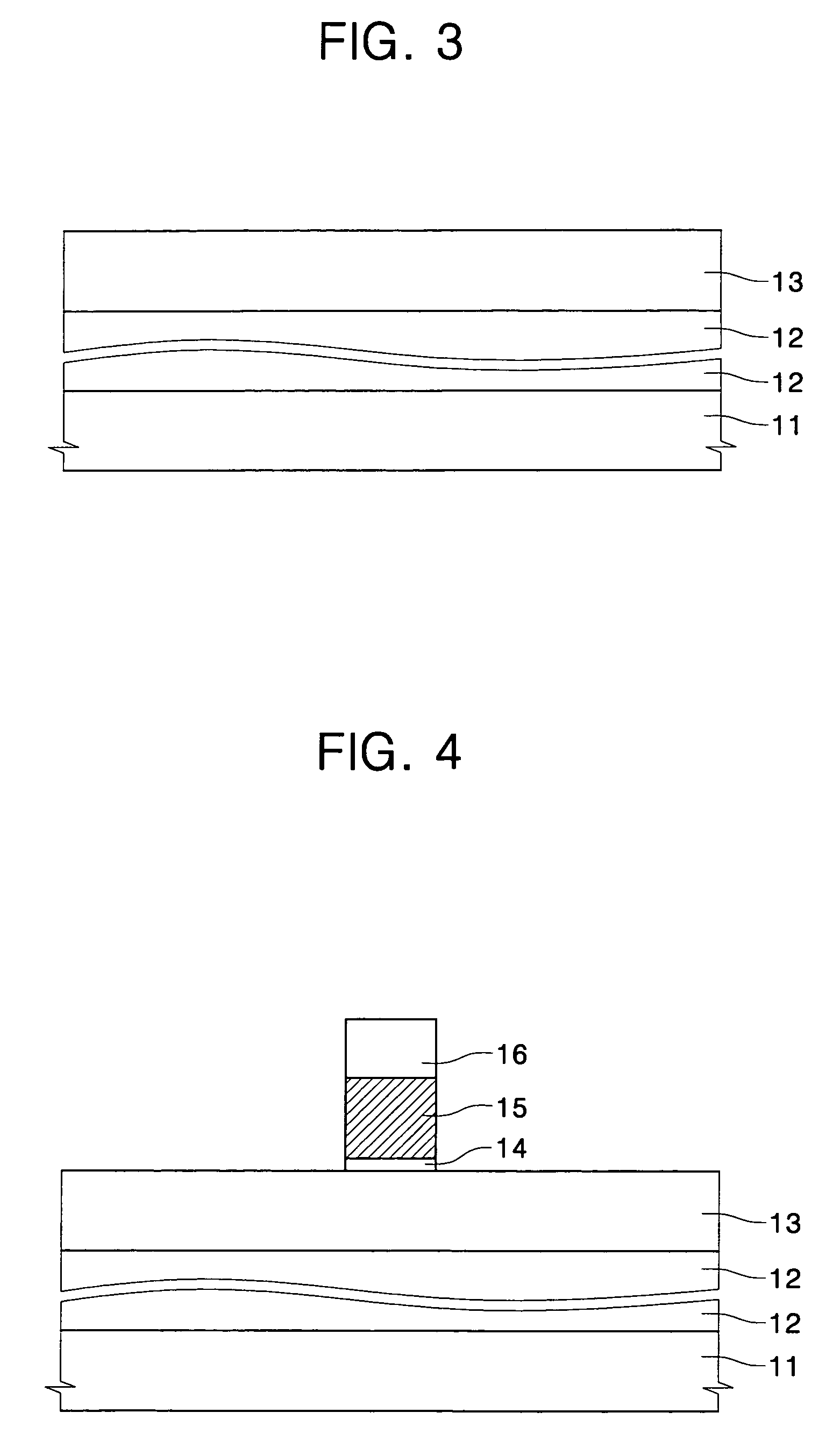

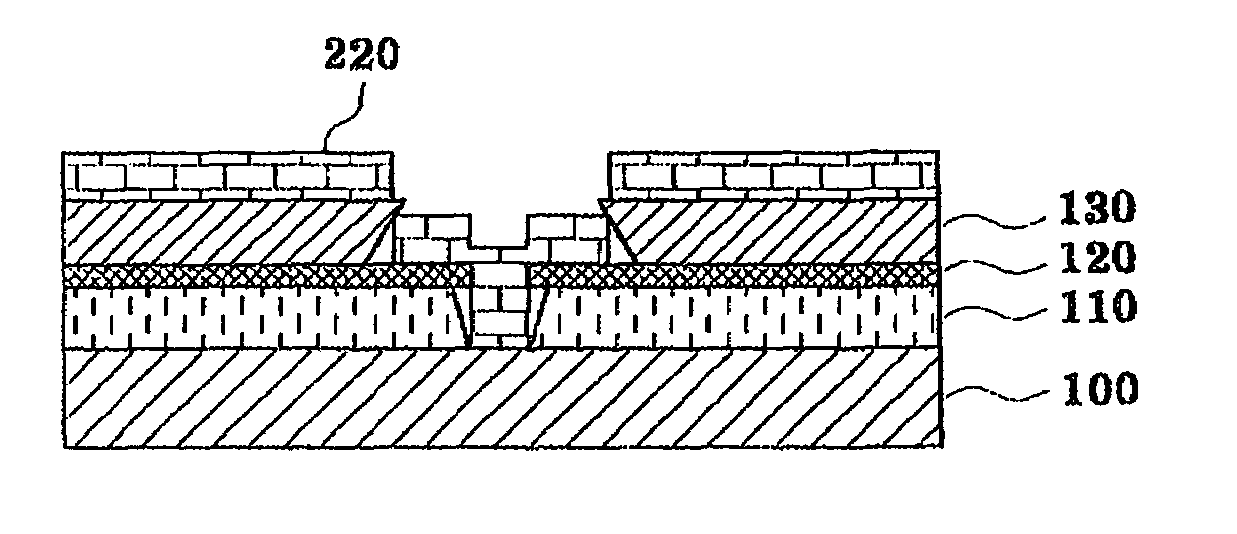

Semiconductor integrated circuit devices having single crystalline thin film transistors and methods of fabricating the same

InactiveUS20060102959A1Solid-state devicesSemiconductor/solid-state device manufacturingBody PatterningSingle crystal

Semiconductor integrated circuit devices having single crystalline thin film transistors and methods of fabricating the same are provided. The semiconductor integrated circuit devices include an interlayer insulating layer formed on a semiconductor substrate and a single crystalline semiconductor plug penetrating the interlayer insulating layer. A single crystalline semiconductor body pattern is provided on the interlayer insulating layer. The single crystalline semiconductor body pattern has an elevated region and contacts the single crystalline semiconductor plug. The method of forming the single crystalline semiconductor body pattern having the elevated region includes forming a sacrificial layer pattern covering the single crystalline semiconductor plug on the interlayer insulating layer. A capping layer is formed to cover the sacrificial layer pattern and the interlayer insulating layer, and the capping layer is patterned to form an opening which exposes a portion of the sacrificial layer pattern. Subsequently, the sacrificial layer pattern is selectively removed to form a cavity in the capping layer, and a planarized single crystalline semiconductor body pattern is formed to fill the cavity and the opening.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods of fabricating a semiconductor device having a node contact structure of a CMOS inverter

In one embodiment, an intrinsic single crystalline semiconductor plug is formed to pass through a lower insulating layer using a selective epitaxial growth process employing a node impurity region as a seed layer, and a single crystalline semiconductor body pattern is formed on the lower insulating layer using the intrinsic single crystalline semiconductor plug as a seed layer. When the recessed single crystalline semiconductor plug is doped with impurities having the same conductivity type as the node impurity region, a peripheral impurity region is prevented from being counter-doped. As a result, it is possible to implement a high performance semiconductor device that requires a single crystalline thin film transistor as well as a node contact structure with ohmic contact.

Owner:SAMSUNG ELECTRONICS CO LTD

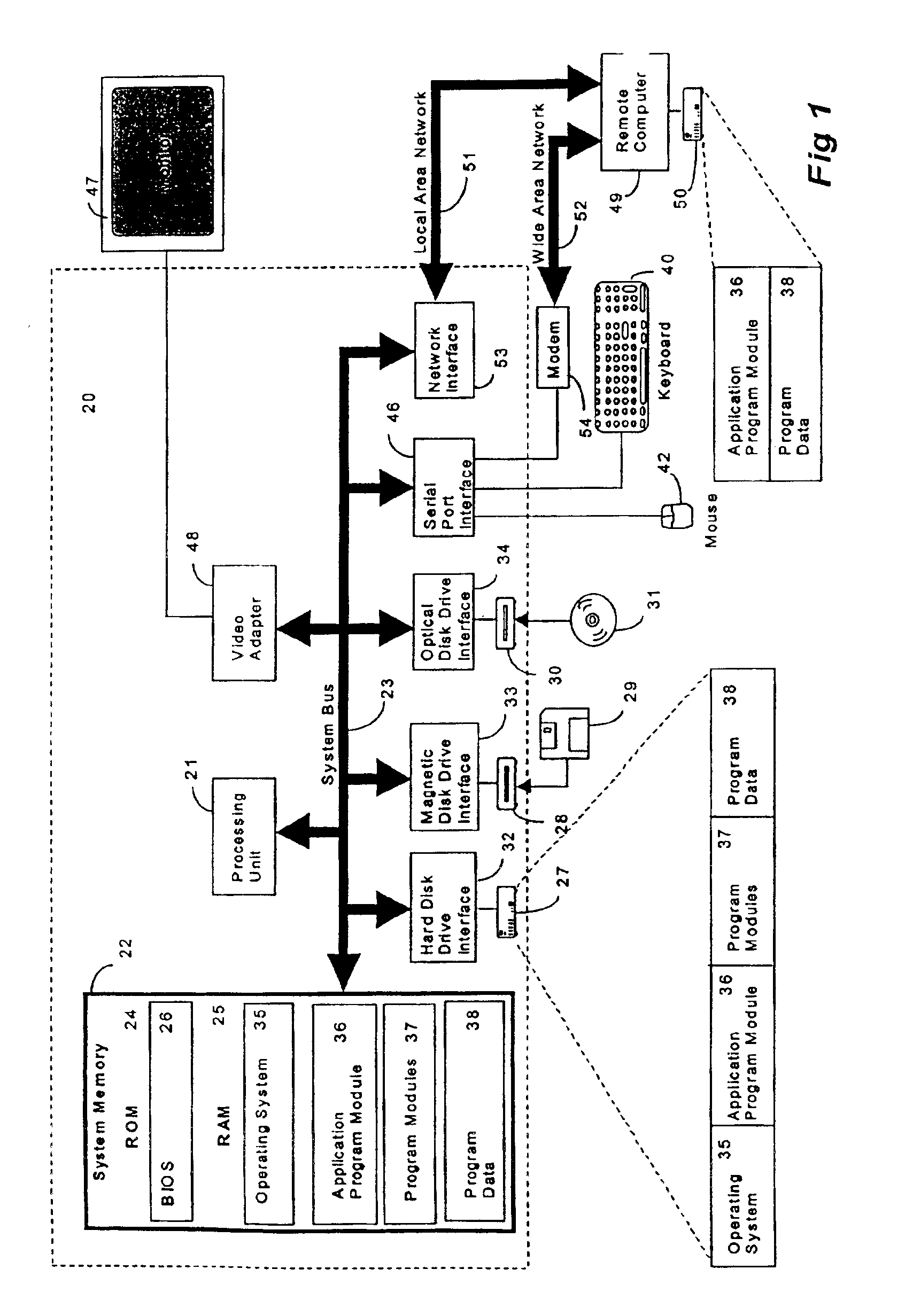

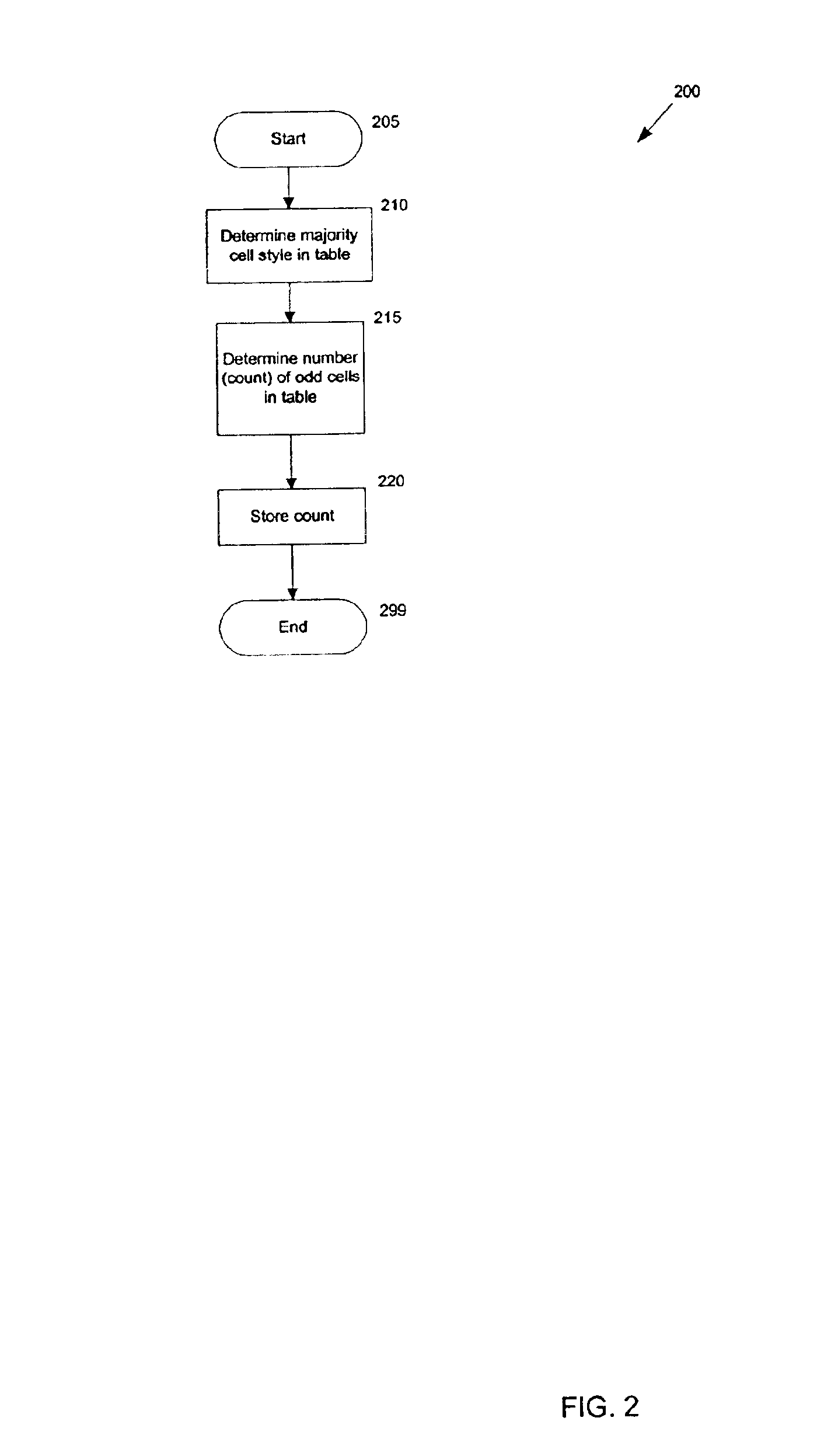

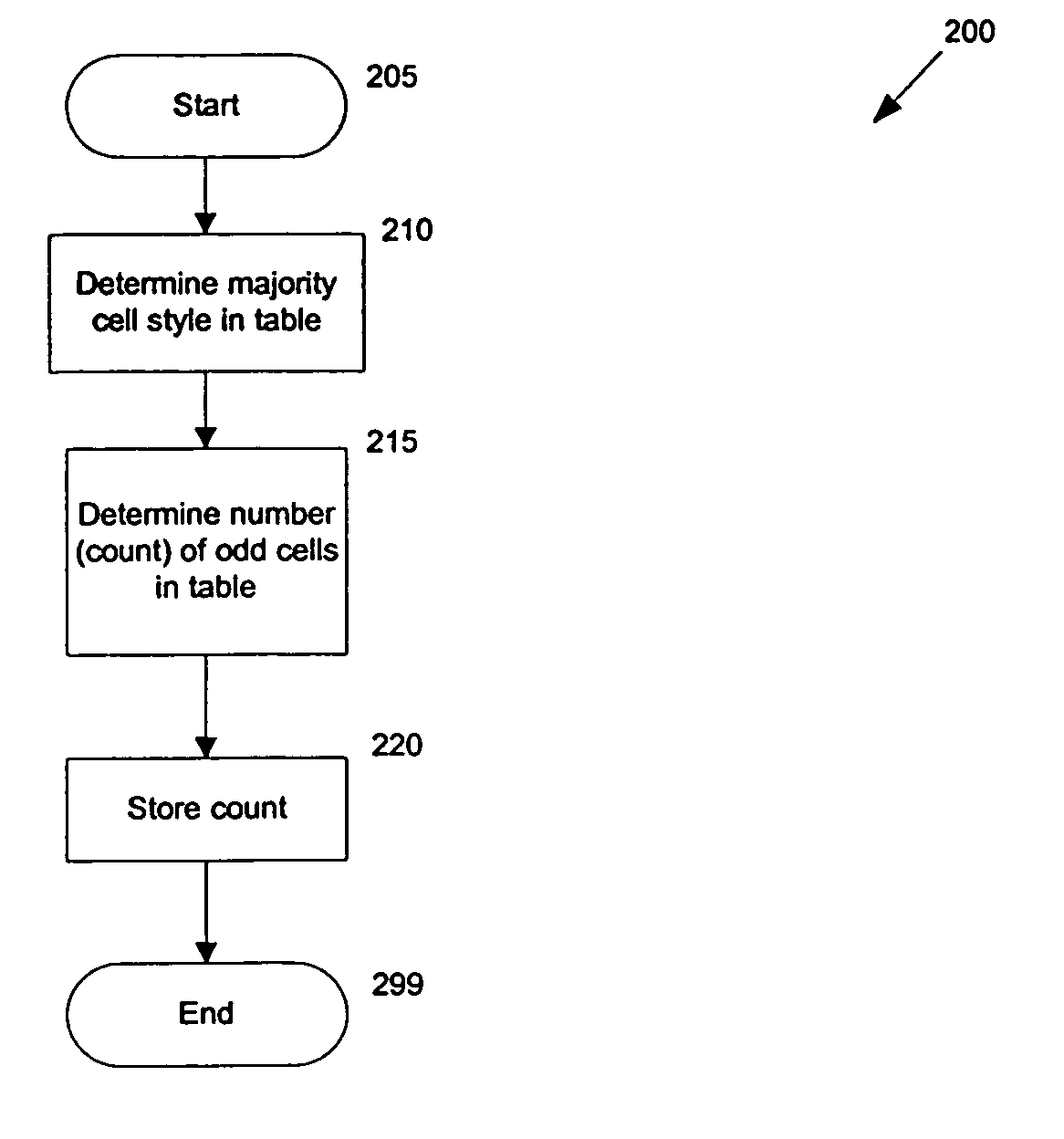

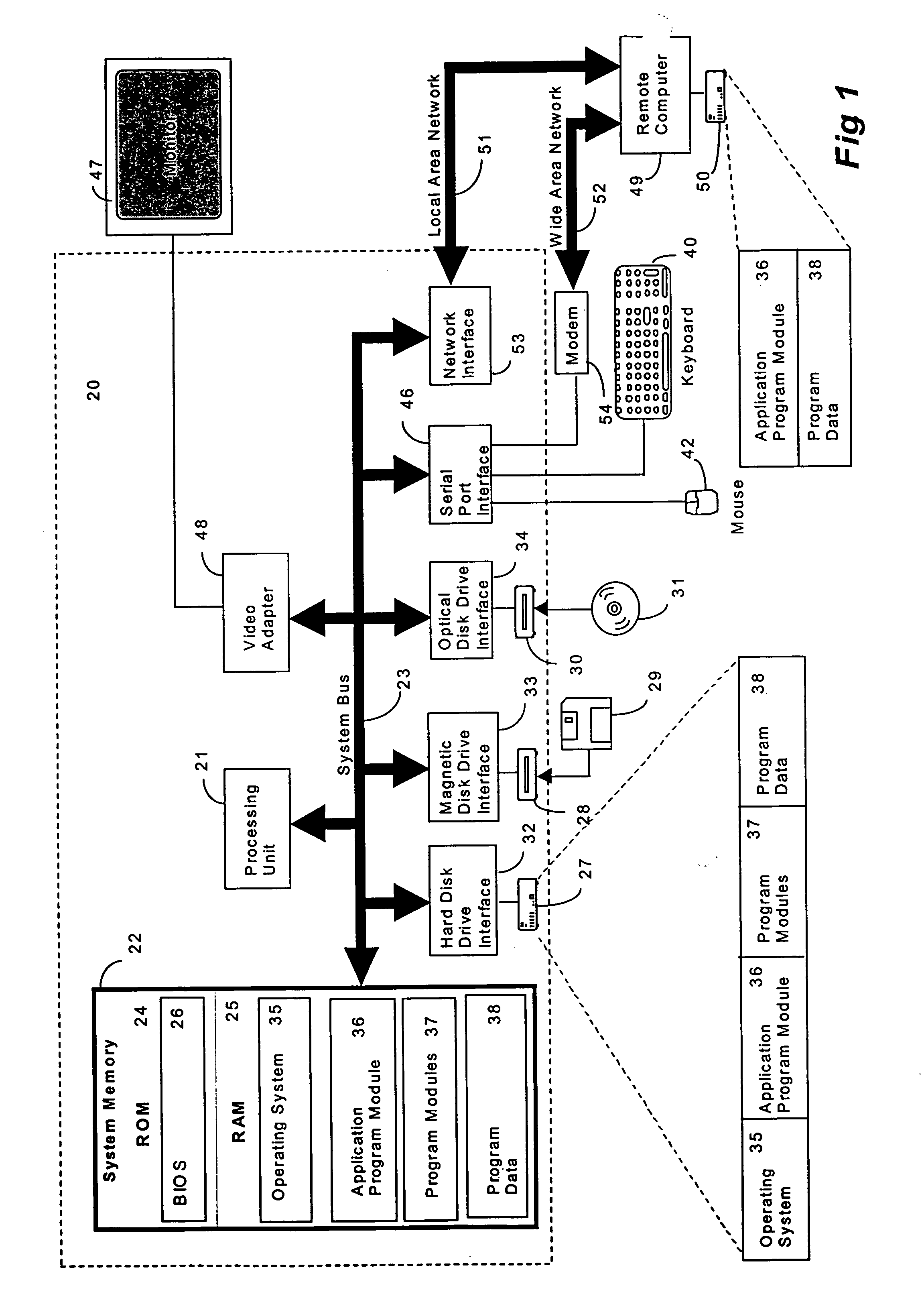

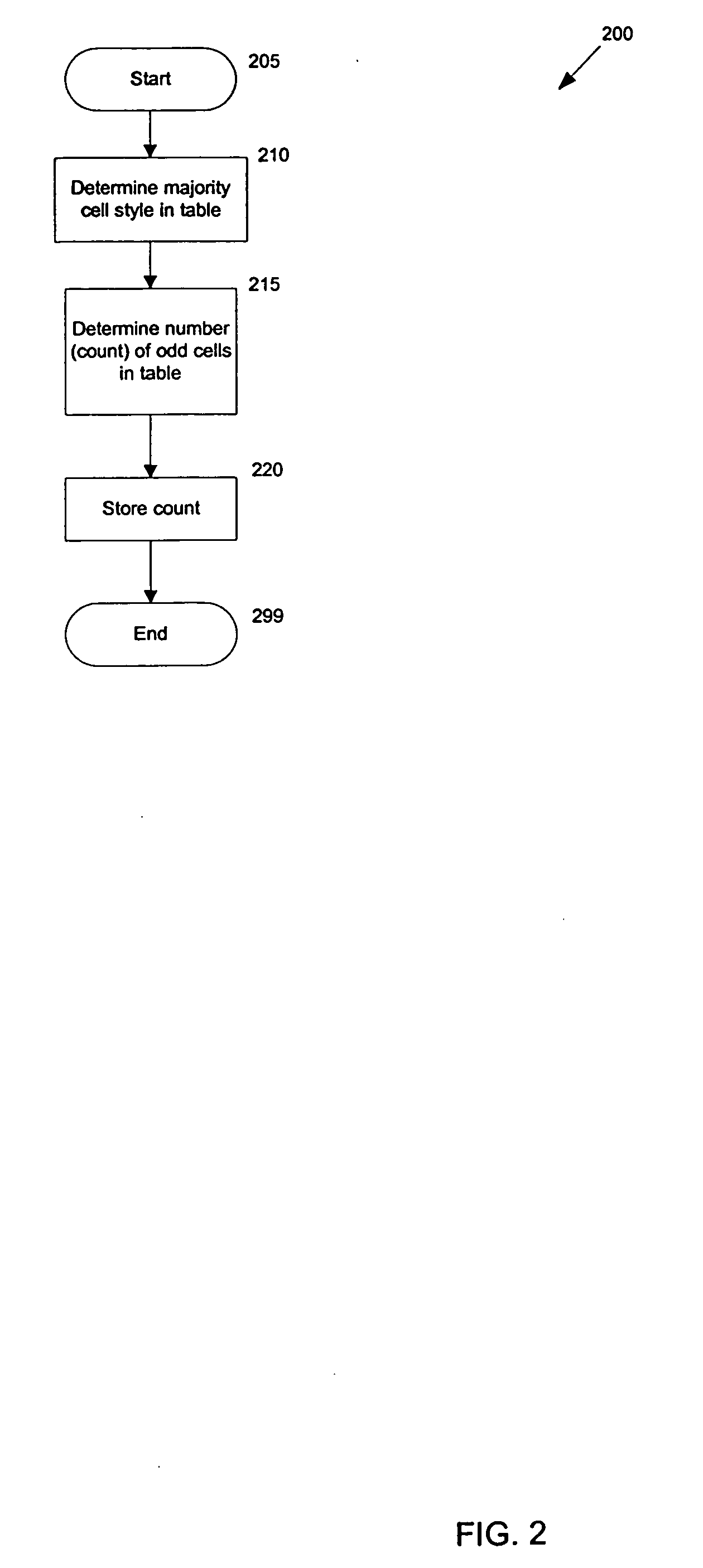

Table styles inference engine

InactiveUS6871319B2Natural language data processingSpecial data processing applicationsPattern recognitionBody Patterning

A table styles inference engine determines the optimal body pattern to describe a user-created table. Optimal uniform, row banding, and column banding body patterns, are determined. The user-defined table is analyzed assuming different uniform different row banding, and / or different column banding body patterns. The optimal uniform body pattern is then determined by determining the uniform body pattern that most closely matches the user-defined table. The optimal row banding body pattern is then determined by determining the row banding body pattern that most closely matches the user-defined table. The optimal column banding body pattern is then determined by determining the column banding body pattern that most closely matches the user-defined table. From these optimal body patterns, the closest match to the user-defined table is determined to be the overall optimal body pattern. The overall optimal body pattern is then saved as a table style.

Owner:MICROSOFT TECH LICENSING LLC

Photosensitive conductive paste and conductive body pattern formed thereby

InactiveCN1494090AImprove sinterabilityImprove conductivityNon-conductive material with dispersed conductive materialPhotosensitive materials for photomechanical apparatusConductive pasteX ray analysis

The purpose of the present invention is to provide a photosensitive conduction paste which is excellent in both of formability of high-fineness patterns and firing properties at <= 600 DEG C. The photosensitive conduction paste contains (A) silver powders having a low degree of crystallinity, (B) an organic binder, (C) a photopolymerizable monomer, and (D) a photopolymerization initiator, in which the silver powder (A) having the low degree of crystallinity exhibits a value of >= 0.15 DEG at a half peak width of the Ag (111) face peak in X-ray analysis patterns.

Owner:TAIYO INK MFG

Semiconductor device having a plurality of stacked transistors and method of fabricating the same

A semiconductor device according to example embodiments may have a plurality of stacked transistors. The semiconductor device may have a lower insulating layer formed on a semiconductor substrate and an upper channel body pattern formed on the lower insulating layer. A source region and a drain region may be formed within the upper channel body pattern, and a non-metal transfer gate electrode may be disposed on the upper channel body pattern between the source and drain regions. The non-metal transfer gate electrode, the upper channel body pattern, and the lower insulating layer may be covered by an intermediate insulating layer. A metal word line may be disposed within the intermediate insulating layer to contact at least an upper surface of the non-metal transfer gate electrode. An insulating spacer may be disposed on a sidewall of the metal word line. A metal node plug may be disposed within the intermediate insulating layer and the lower insulating layer to contact the source region of the upper channel body pattern. Example embodiments also relate to a method of fabricating the above semiconductor device.

Owner:SAMSUNG ELECTRONICS CO LTD

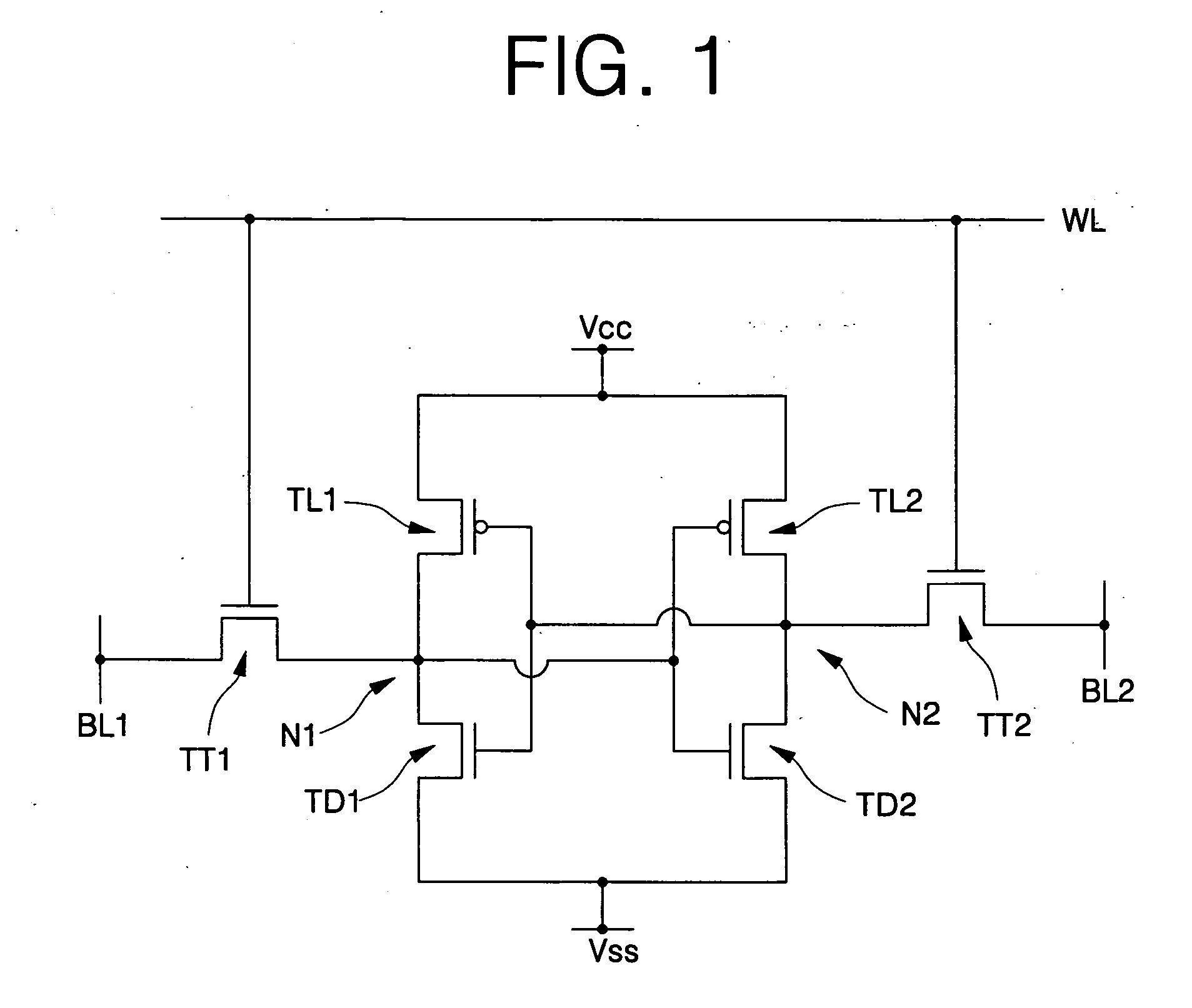

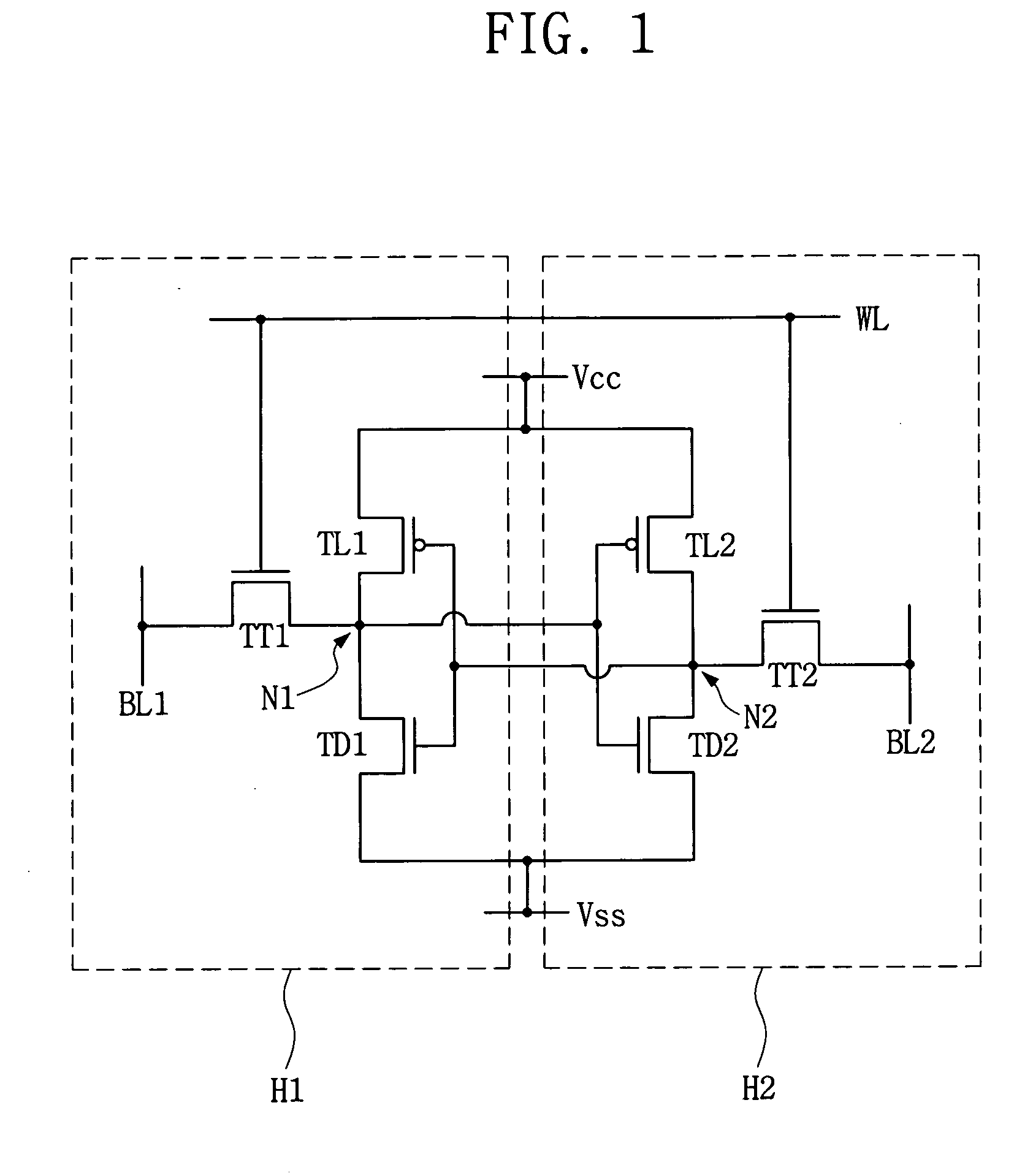

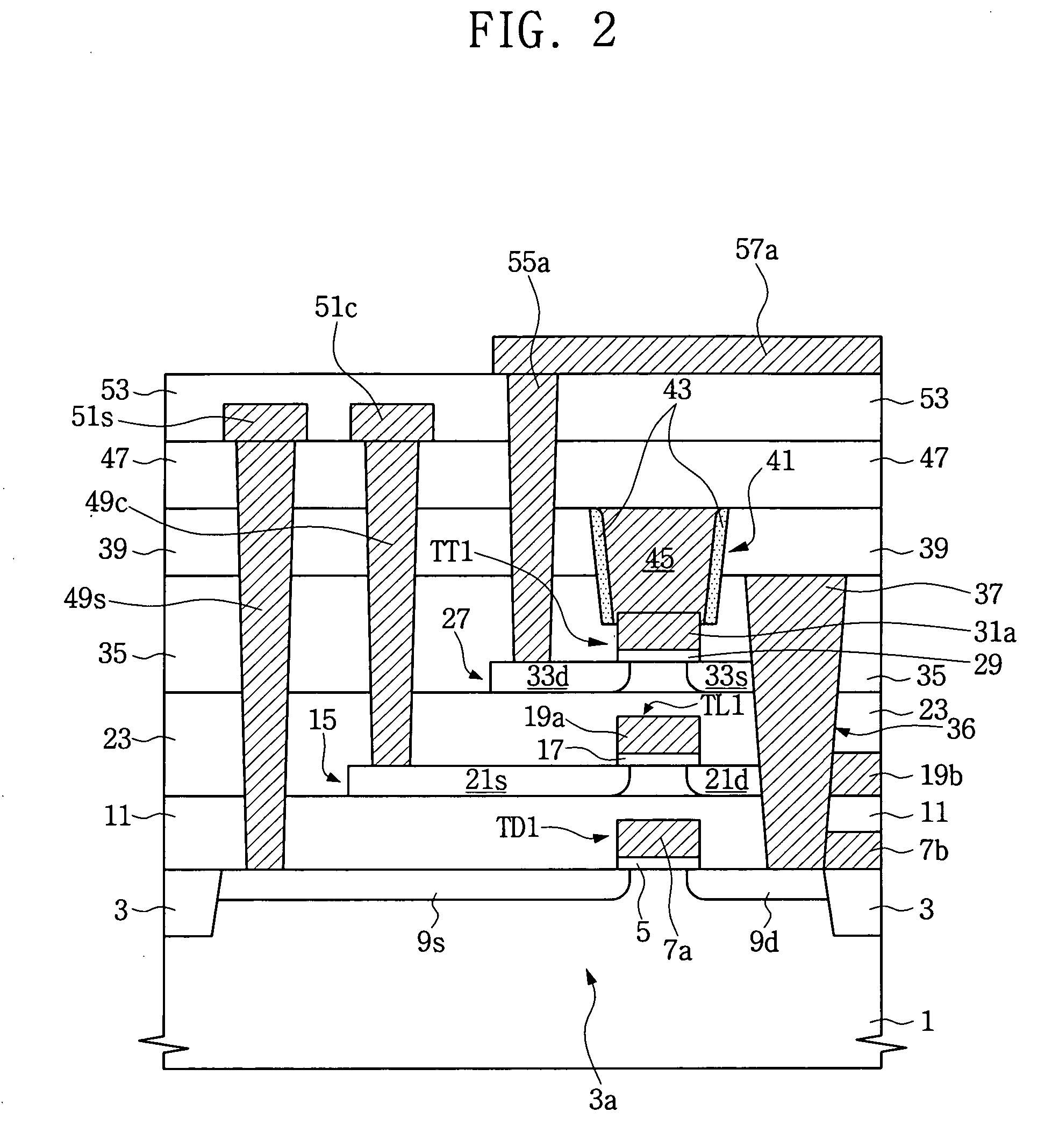

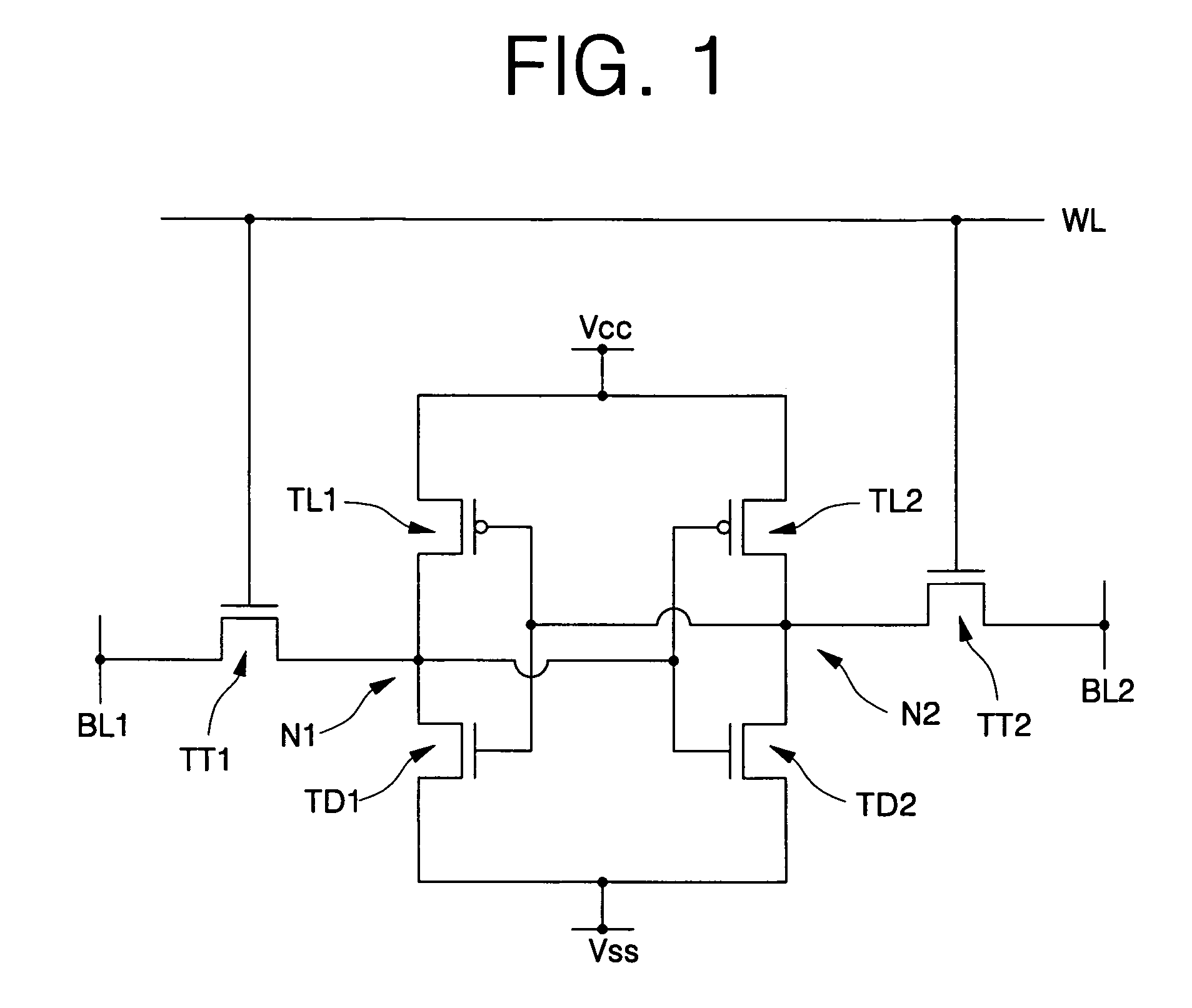

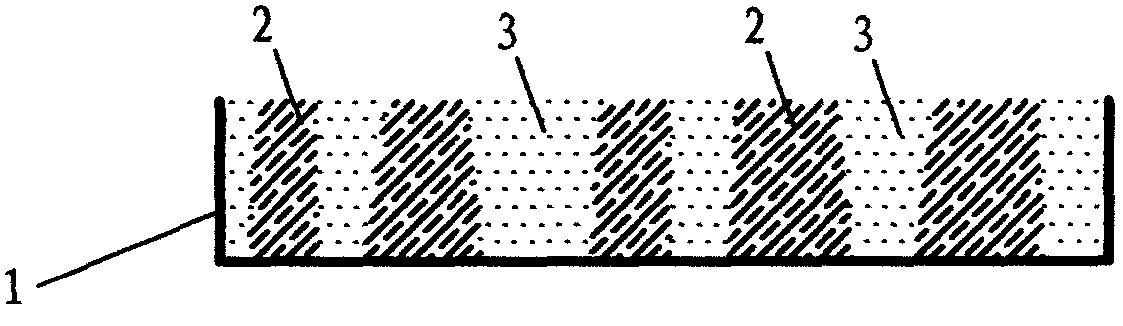

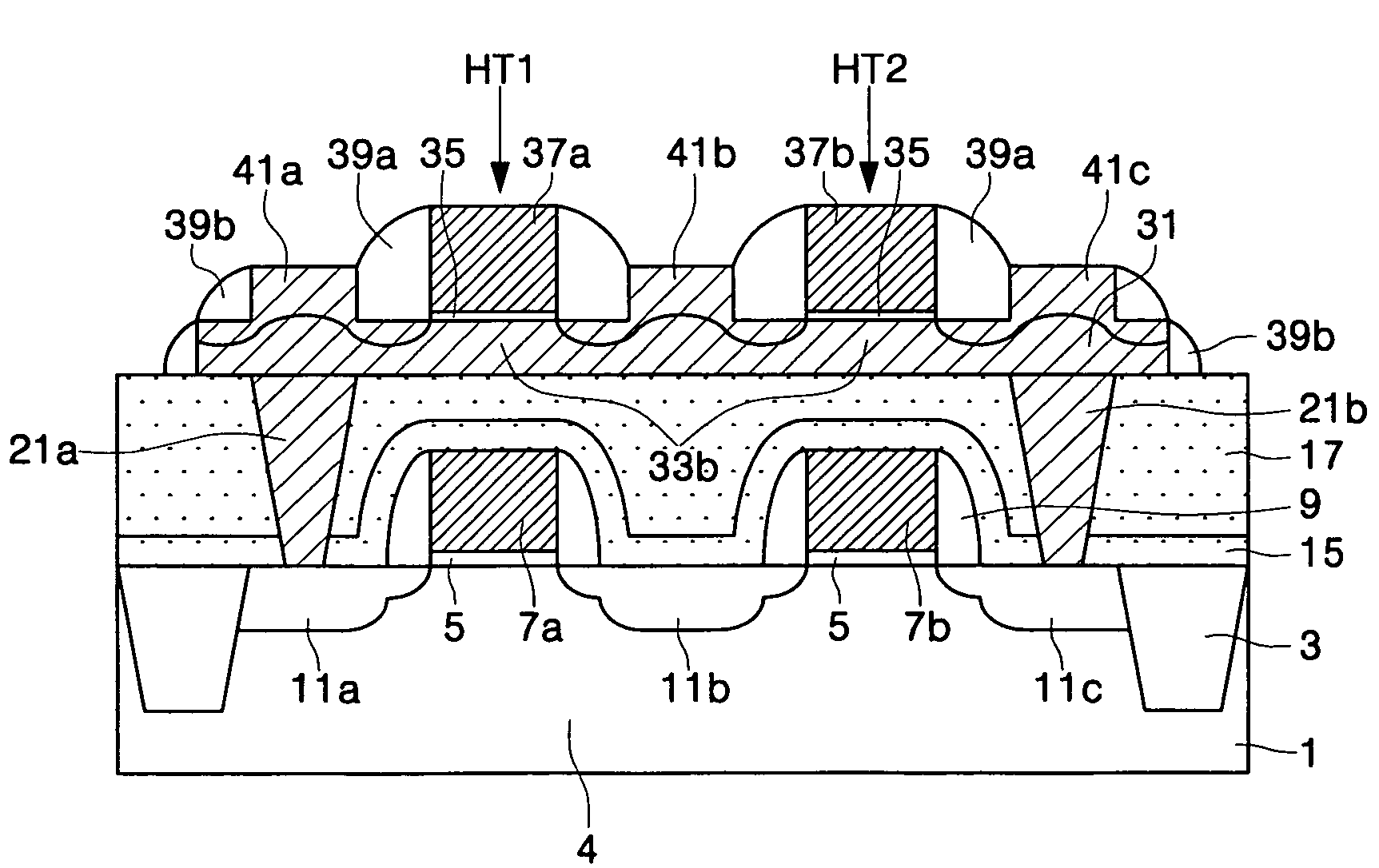

Semiconductor device having body contact through gate and method of fabricating the same

ActiveUS20060019434A1Avoid floating body effectSolid-state devicesSemiconductor/solid-state device manufacturingFloating body effectDevice material

According to an embodiment of the invention, a lower transistor is formed on a semiconductor substrate, and an upper thin film transistor is formed on the lower transistor. A body contact plug is formed to penetrate an upper gate electrode of the upper thin film transistor and a body pattern, and to electrically connect with a lower gate electrode of the lower transistor. The body contact plug uses a contact hole to apply an electrical signal to the upper gate electrode of the upper thin film transistor, so additional volume is not necessary. Since the upper gate electrode is electrically connected to the body pattern through the body contact plug, the floating body effect of the upper thin film transistor can be improved. Therefore, a semiconductor device is provided with the high performance required to realize a highly-integrated semiconductor device.

Owner:SAMSUNG ELECTRONICS CO LTD

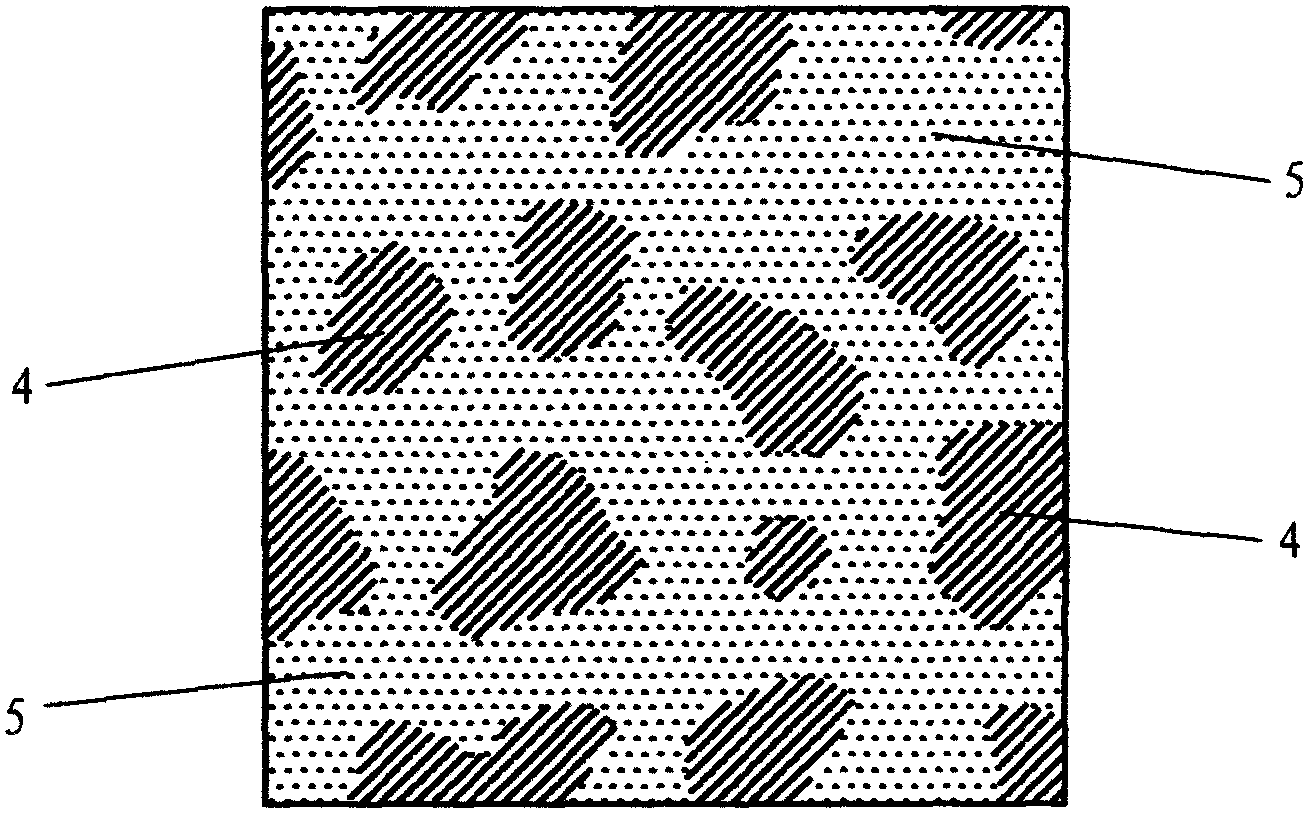

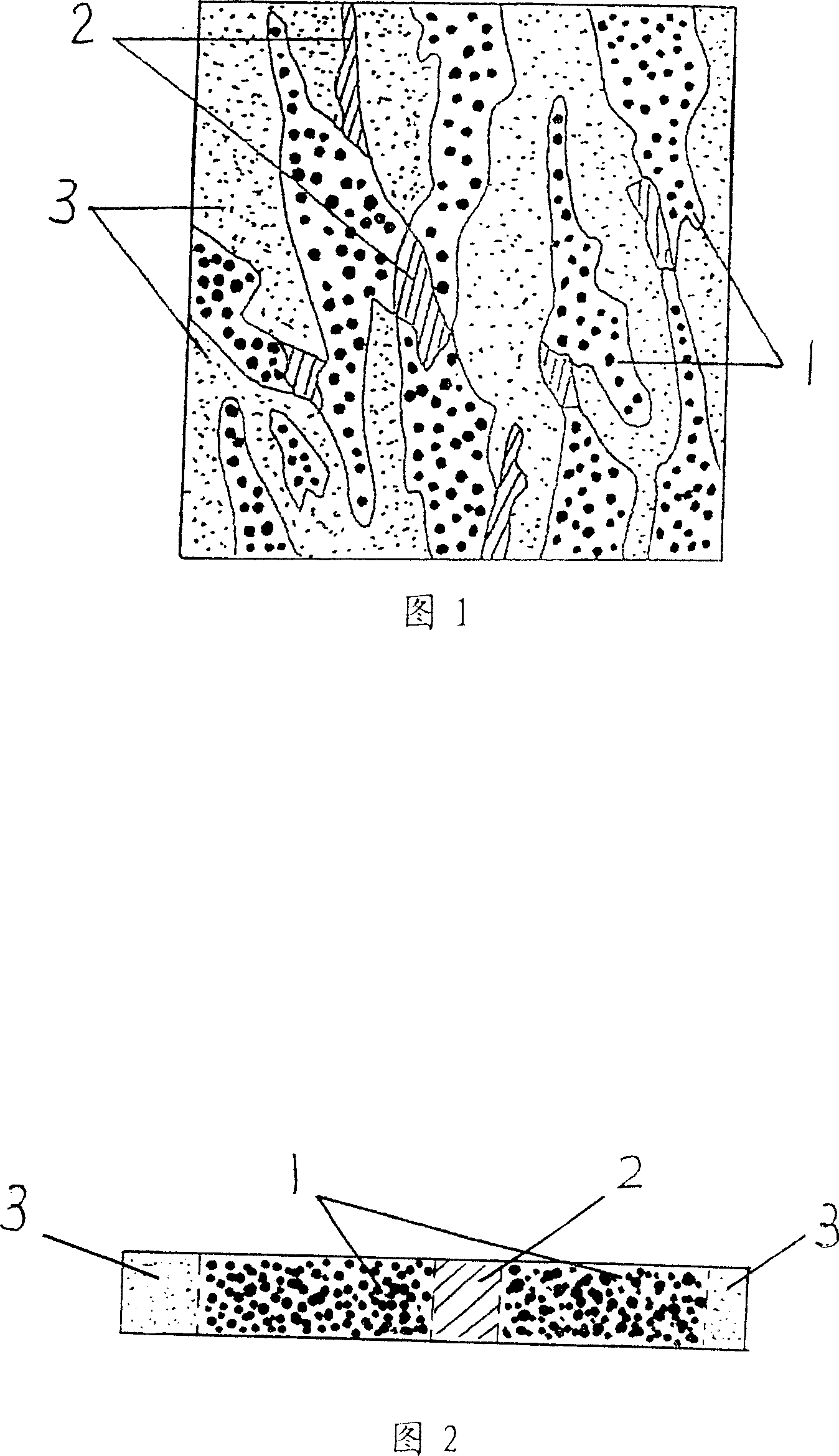

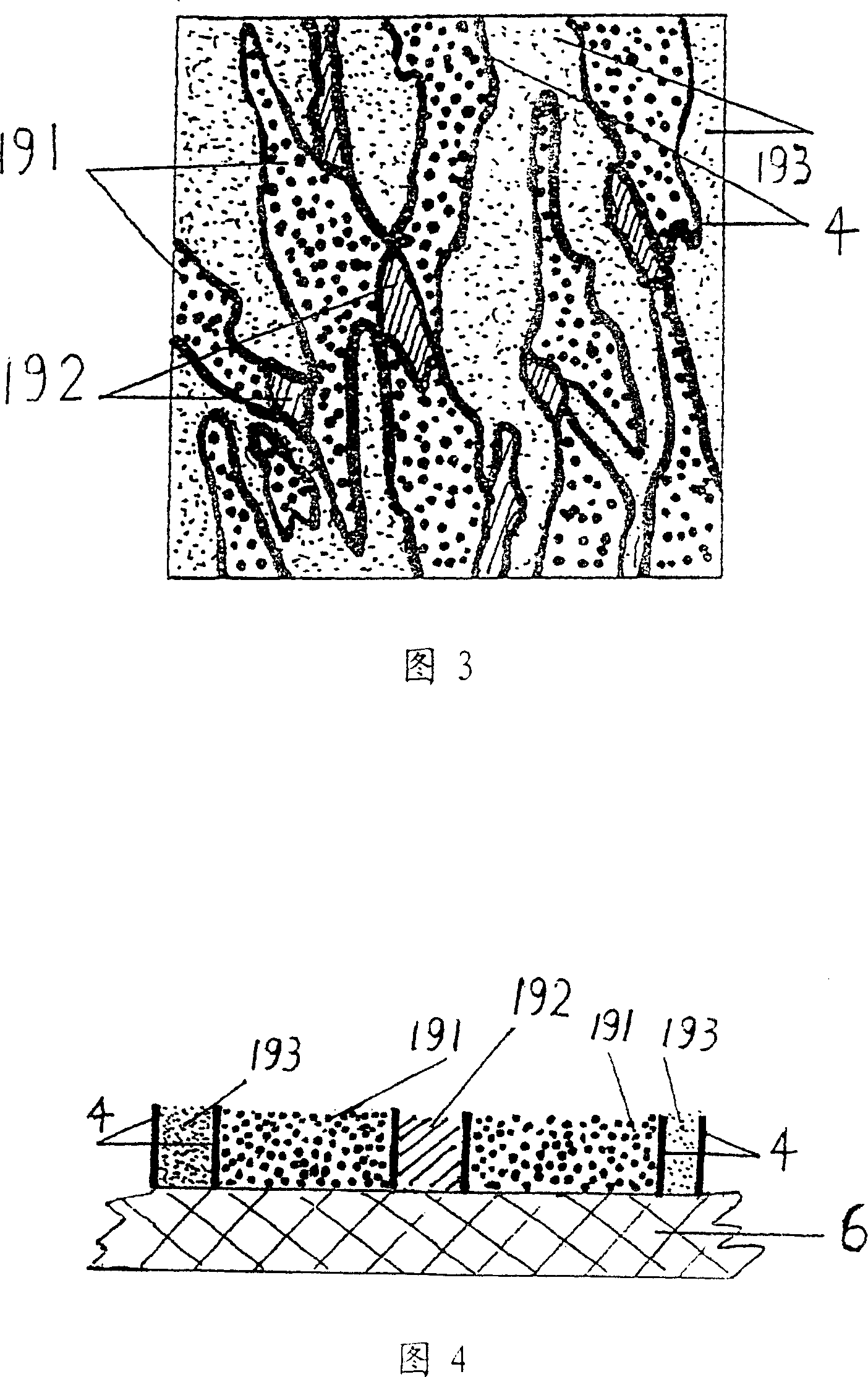

Imitated stone slab with preset patterns containing different size grading raw materials and preparation method thereof

The invention provides an imitated stone slab with preset patterns containing different size grading raw materials. The imitated stone slab with the preset patterns containing the different size grading raw materials is characterized in that a product of the imitated stone slab is made of porcelain raw materials; the product of the imitated stone slab contains two to twenty types of body pattern color areas with different preset shapes, wherein the body pattern color areas have different colors which can be obviously distinguished, or the body pattern color areas have the same color with different color depths, or the body pattern color areas have mixed colors with different proportions of colors; the thickness of each multicolour pattern body of each pattern color area of the imitated stone slab is 70-100% of that of a three-dimensional space from the surface layer of the product to the back side of the product; in at least one type of the pattern color areas, 1-10000 patterns are made of colored raw materials which have different preset size grading and comprise 5-95% of large-particle materials with the largest particle size of 6-20mm, 0-90% of middle-particle materials with the largest particle size of 1-6mm, 0-90% of sand powder with the largest particle size of 0.3-1mm, and 5-95% of micro-fine powder with the largest particle size of 0.1-0.3mm; the consumption of the raw materials with different particle sizes and the colors of different color area patterns are determined according to the requirements given in advance.

Owner:陈章武

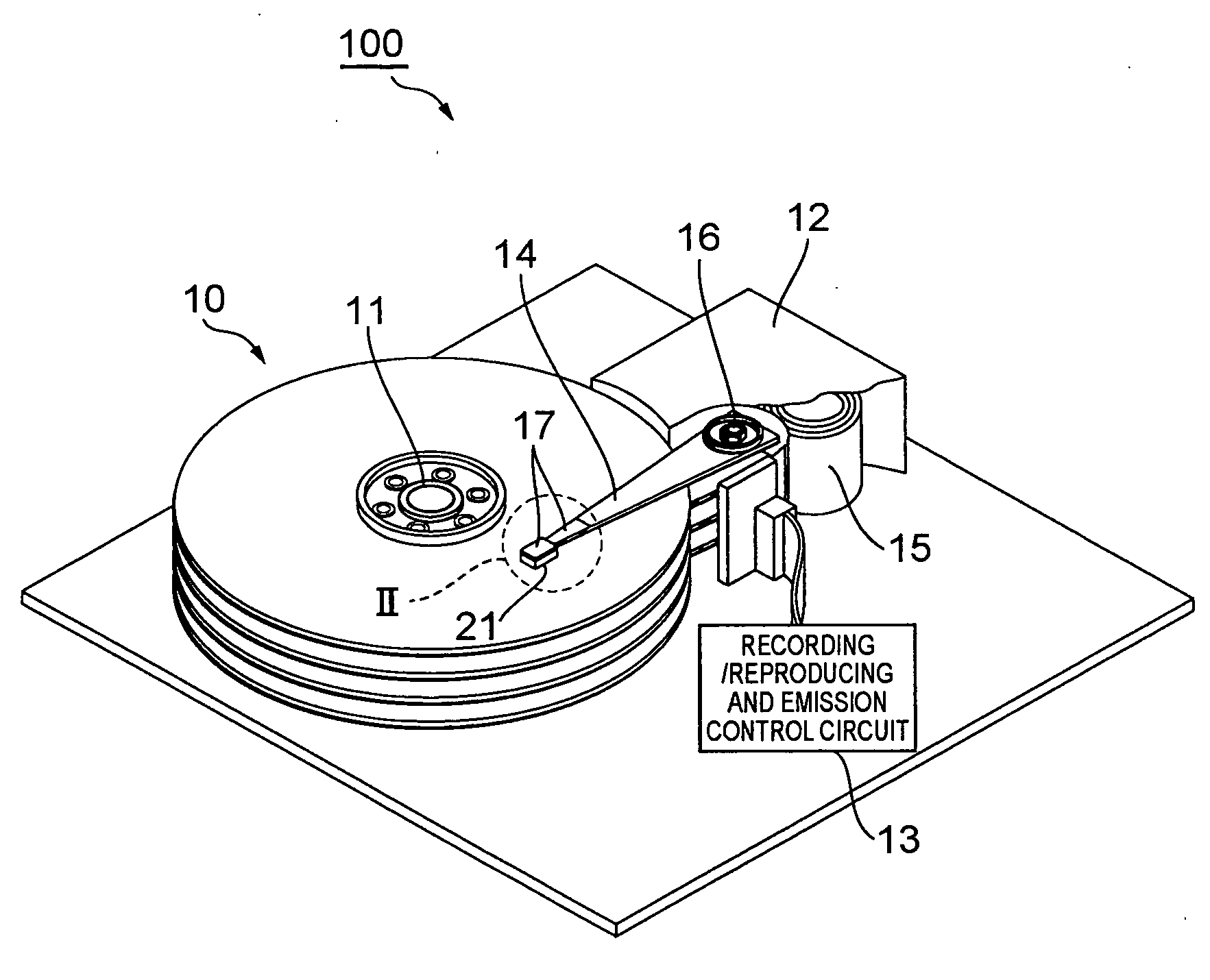

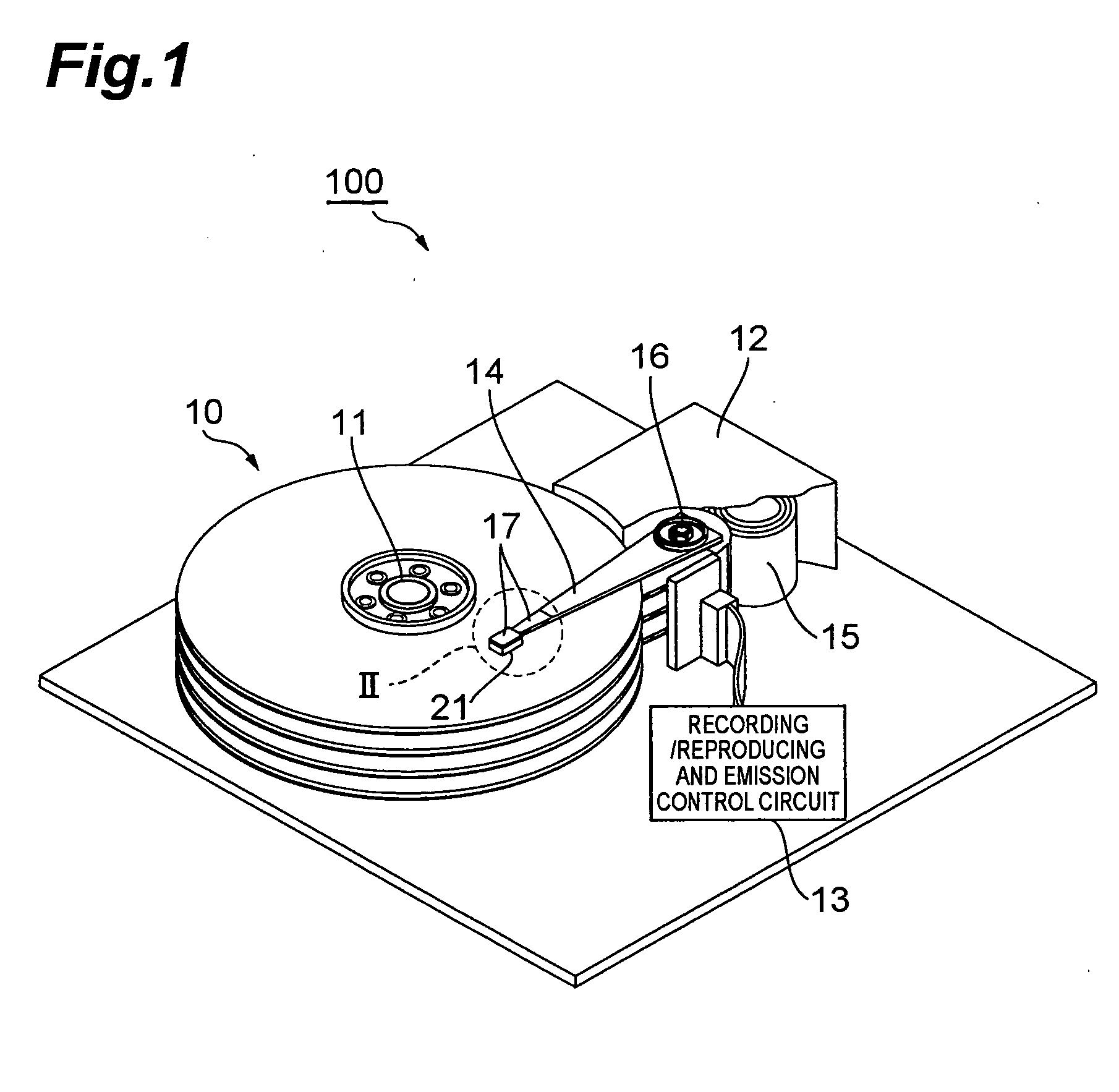

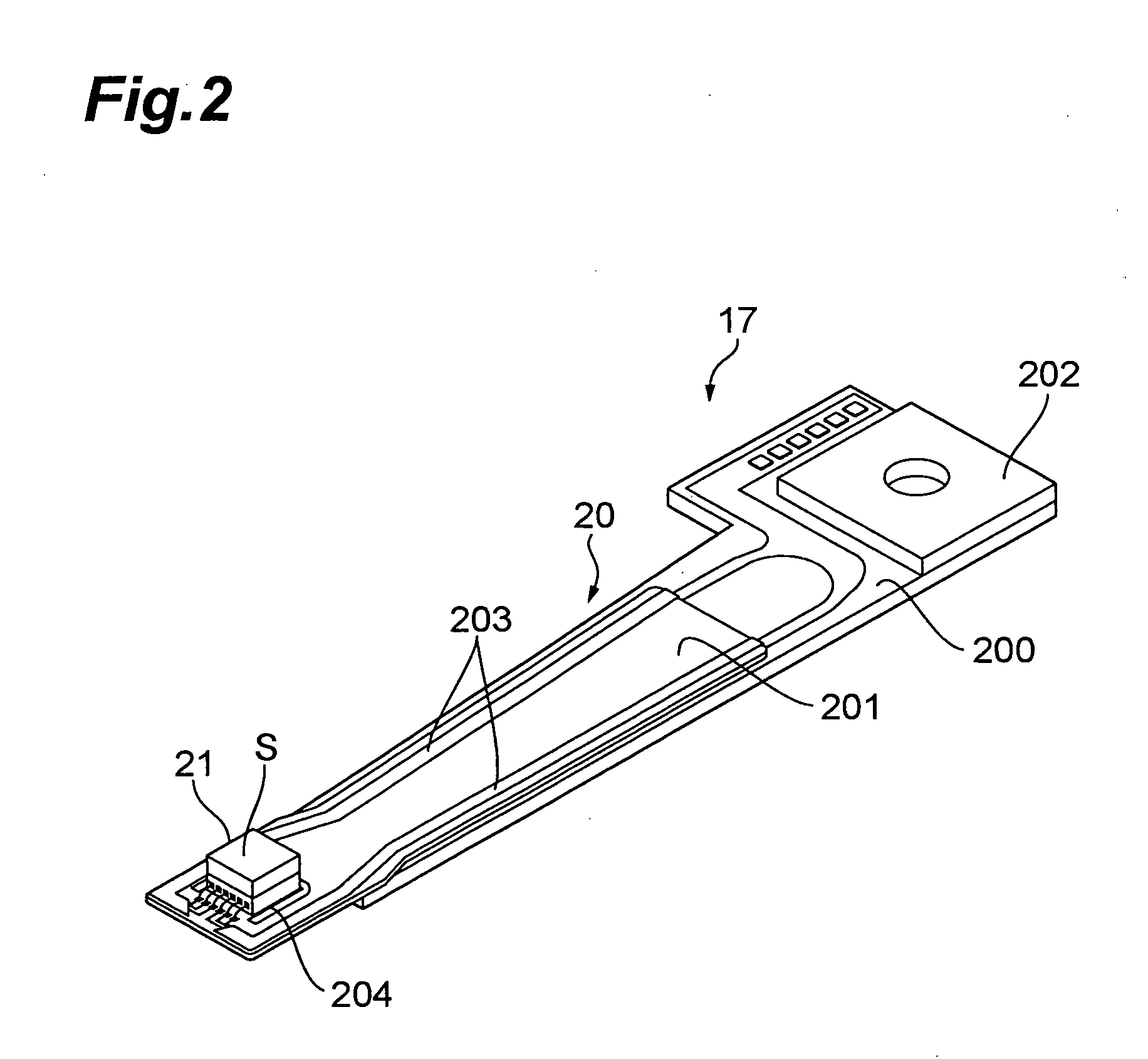

Method of manufacturing thermally assisted magnetic head

ActiveUS20090188891A1Easy to flattenEasy to controlDecorative surface effectsOptical articlesBody PatterningEngineering

A method comprises a first multilayer body forming step of forming a first multilayer body on a first cladding layer, the first multilayer body including a core layer and a first polishing stop layer in order from the first cladding layer side; a first multilayer body patterning step of pattering the first multilayer body, so as to expose the first cladding layer about the patterned first multilayer body; a second multilayer body forming step of forming a second multilayer body on the exposed first cladding layer and patterned first multilayer body, the second multilayer body including a second cladding layer and a second polishing stop layer in order from the first cladding layer side; and a removing step of polishing away a part of the second multilayer body formed on the first multilayer body.

Owner:TDK CORPARATION

Semiconductor device having a plurality of stacked transistors and method of fabricating the same

A semiconductor device according to example embodiments may have a plurality of stacked transistors. The semiconductor device may have a lower insulating layer formed on a semiconductor substrate and an upper channel body pattern formed on the lower insulating layer. A source region and a drain region may be formed within the upper channel body pattern, and a non-metal transfer gate electrode may be disposed on the upper channel body pattern between the source and drain regions. The non-metal transfer gate electrode, the upper channel body pattern, and the lower insulating layer may be covered by an intermediate insulating layer. A metal word line may be disposed within the intermediate insulating layer to contact at least an upper surface of the non-metal transfer gate electrode. An insulating spacer may be disposed on a sidewall of the metal word line. A metal node plug may be disposed within the intermediate insulating layer and the lower insulating layer to contact the source region of the upper channel body pattern. Example embodiments also relate to a method of fabricating the above semiconductor device.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor integrated circuit devices having single crystalline thin film transistors and methods of fabricating the same

InactiveUS7417286B2Semiconductor/solid-state device detailsSolid-state devicesContact formationSingle crystal

Owner:SAMSUNG ELECTRONICS CO LTD

Multi-layer stereo lace production method

InactiveCN107268171ARich layersStrong three-dimensional senseLiquid surface applicatorsWarp knittingPulp and paper industryBody Patterning

The invention discloses a method for producing multi-layer three-dimensional lace, which is produced on a multi-bar raschel warp knitting machine, and is equipped with two separated jacquard bars, at least one weft insert bar, and at least one pressed yarn bar. Bars, weaving through jacquard bars to form a fancy ground net, weaving through interlining flower bars to form a multi-layer weft inlay pattern layer, and weaving through embossing flower bar to form an embossed pattern layer; The three-dimensional flocking is bonded with fluff on the surface of the lace to form a flocking pattern with a certain outline, and forms a multi-layered three-dimensional lace with the fancy ground net, the weft pattern and the pressed yarn pattern. The fancy ground net formed by the invention is light, thin and transparent, and the formed main pattern is rich in layers and has a prominent three-dimensional effect, which provides an effective method for the production of high-grade three-dimensional lace.

Owner:JIANGNAN UNIV

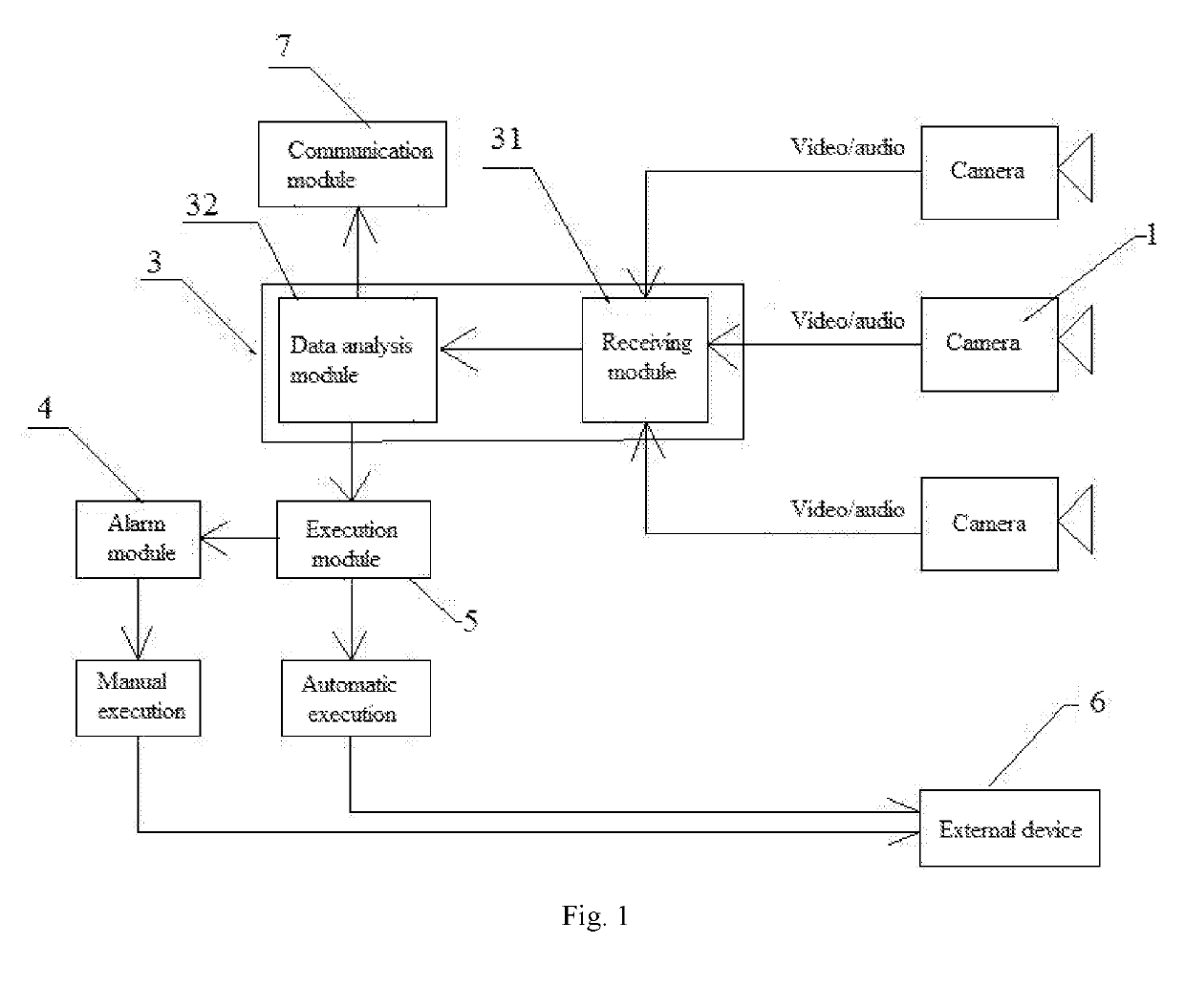

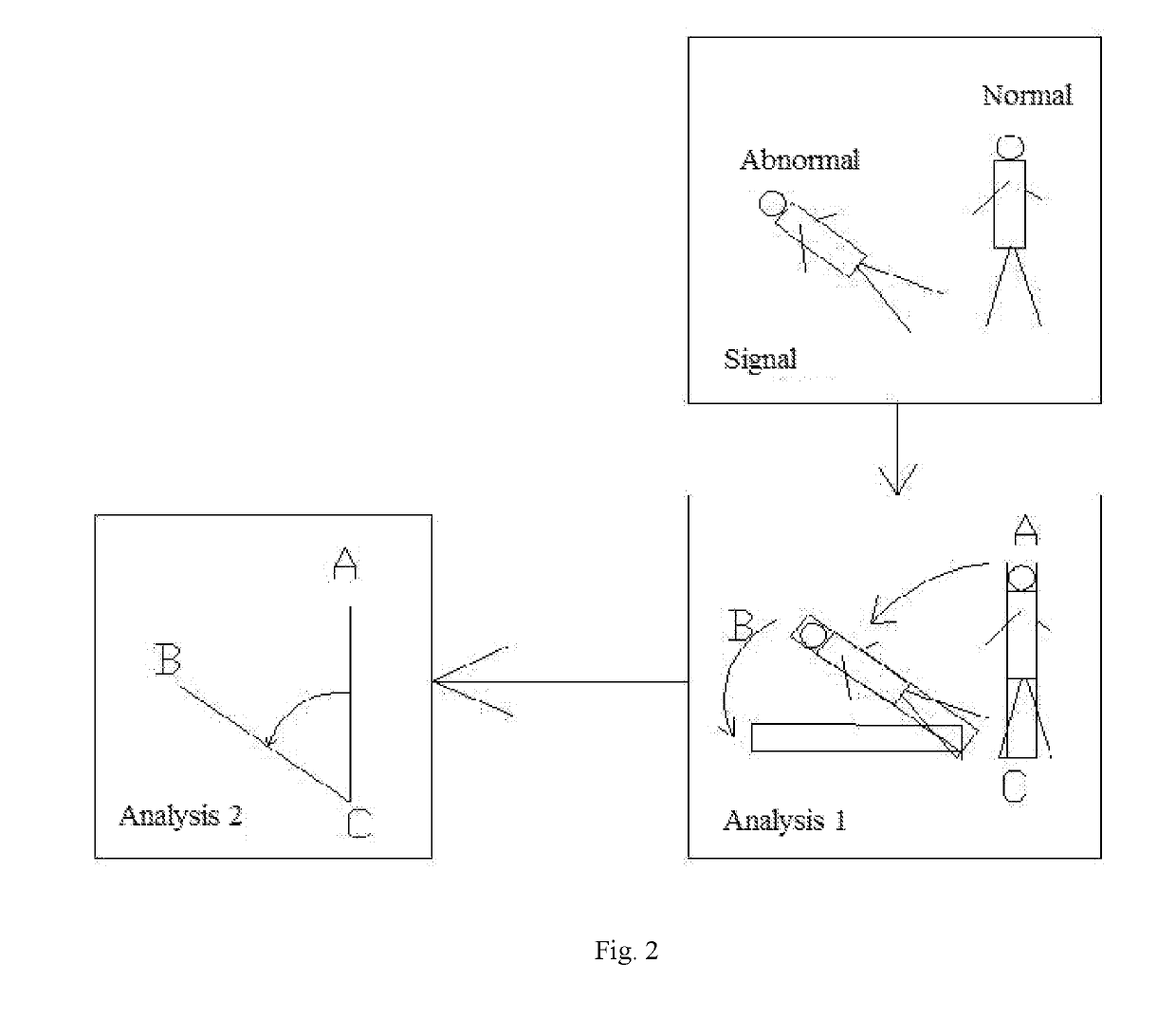

Body fall smart control system and method therefor

ActiveUS20190114895A1High speedImprove accuracyImage enhancementImage analysisImaging processingAutomatic braking

A body fall smart control system includes at least one image capturing module used for capturing a video image and an image processing module connected to the image capturing module. The image processing module is used for performing body pattern identification on the captured video image, establishing a 2D or 3D model of the identified body pattern, tracking whether a signal change speed and / or angle of the modeled body pattern reaches a set threshold value to determine whether a fall has occurred, and controlling an alarm module to sound an alarm if a fall has occurred. A 2D or 3D model compares and analyzes the speed, angle, associated help voice, etc. of a falling body to determine whether a fall has occurred, and sounding an alarm and sending a signal for manual braking or automatic braking etc. and controlling an action of a related device if the comparison is successful.

Owner:SUZHOU LING WEI TECH CO LTD

Body-tied-to-source MOSFETs with asymmetrical source and drain regions and methods of fabricating the same

Owner:SAMSUNG ELECTRONICS CO LTD

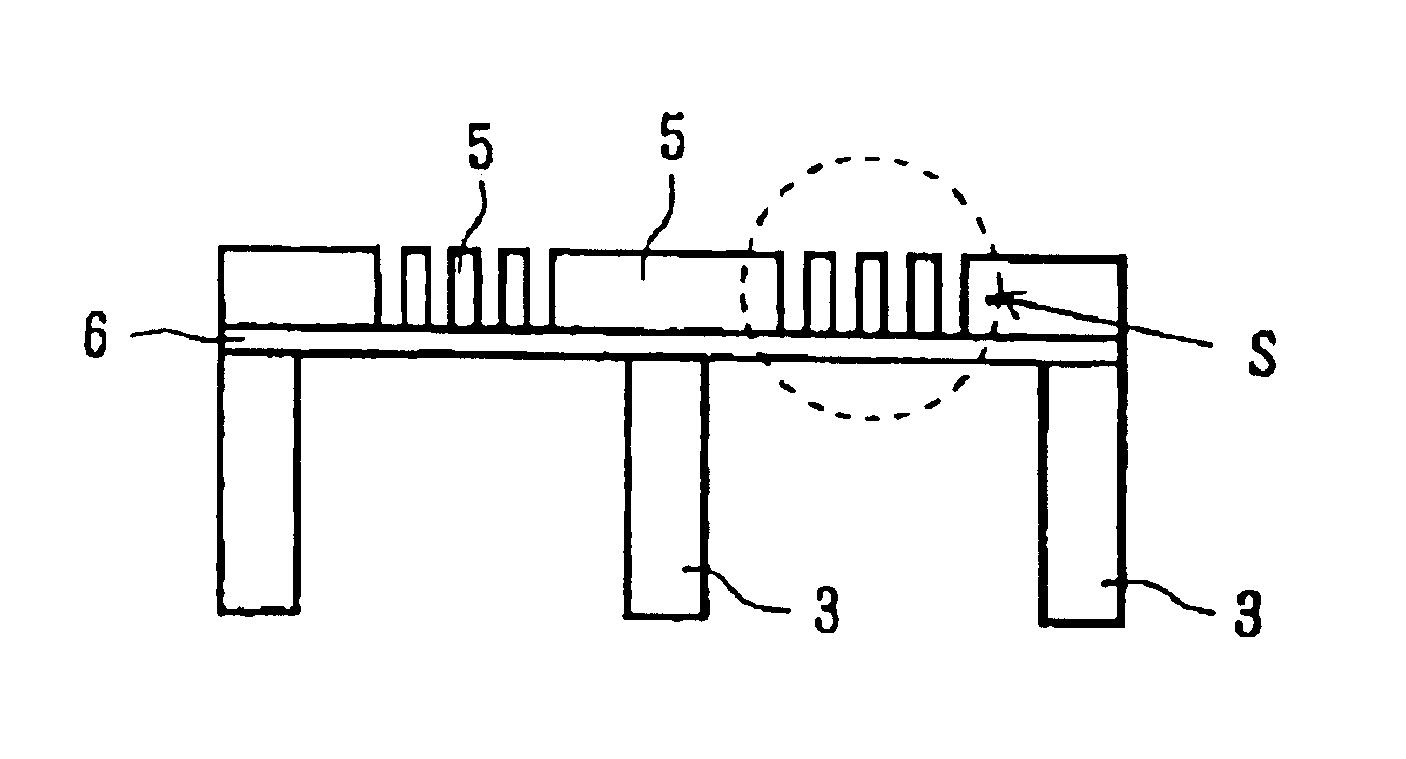

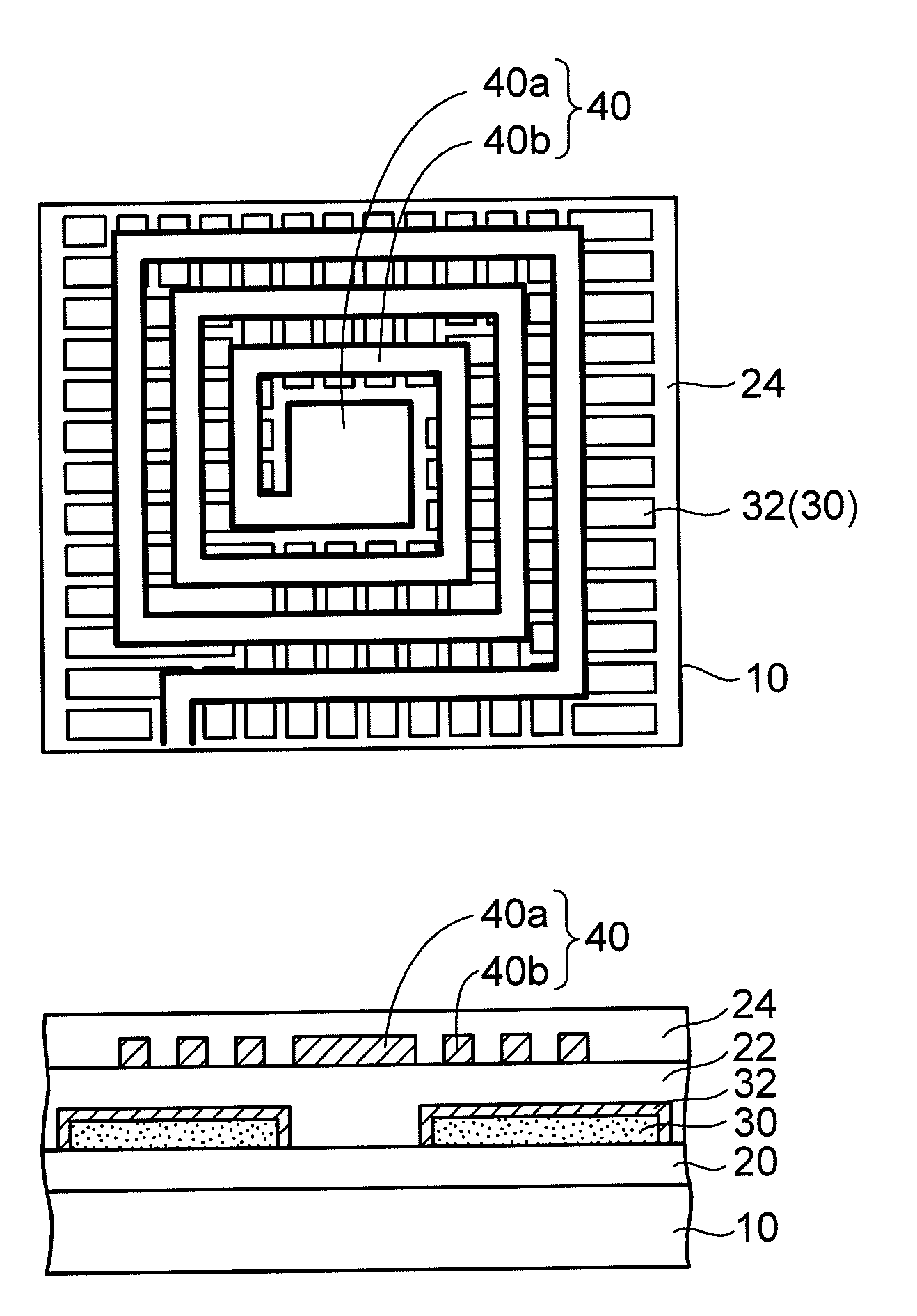

Inductor device, and method of manufacturing the same

ActiveUS20100231344A1Well formedImprove reliabilityTransformers/inductances coils/windings/connectionsInductances/transformers/magnets manufactureInductorBody Patterning

An inductor device includes a first magnetic body pattern layer in which slits are provided and which is made to a pattern, a lower insulating layer formed on the first magnetic body pattern layer, a planar coil layer formed on the lower insulating layer, an upper insulating layer formed on the planar coil layer, and a second magnetic body pattern layer formed on the upper insulating layer and in which slits are provided and which is made to a pattern, wherein the first magnetic body pattern layer and the second magnetic body pattern layer are arranged to intersect orthogonally with the planar coil layer.

Owner:SHINKO ELECTRIC IND CO LTD

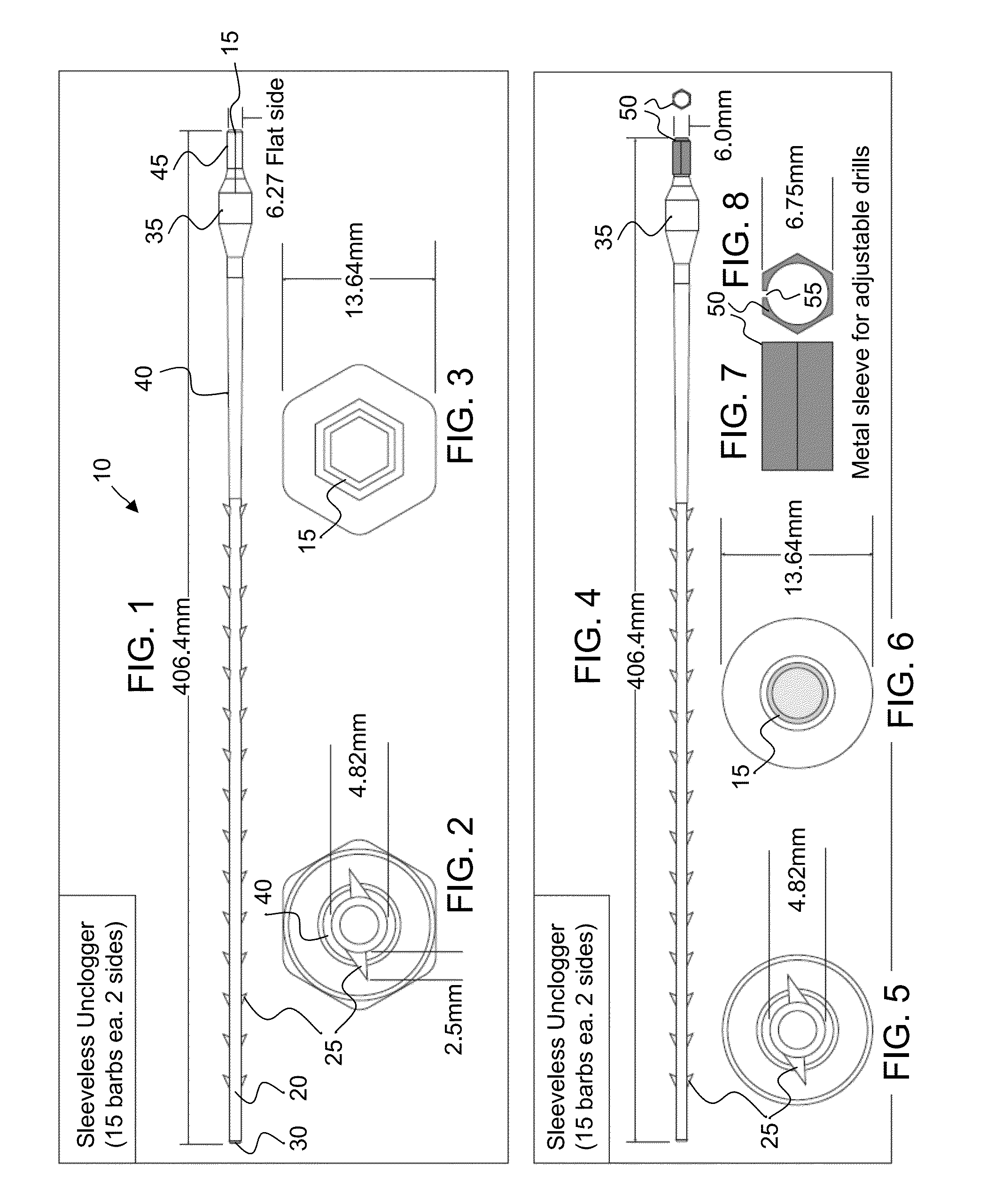

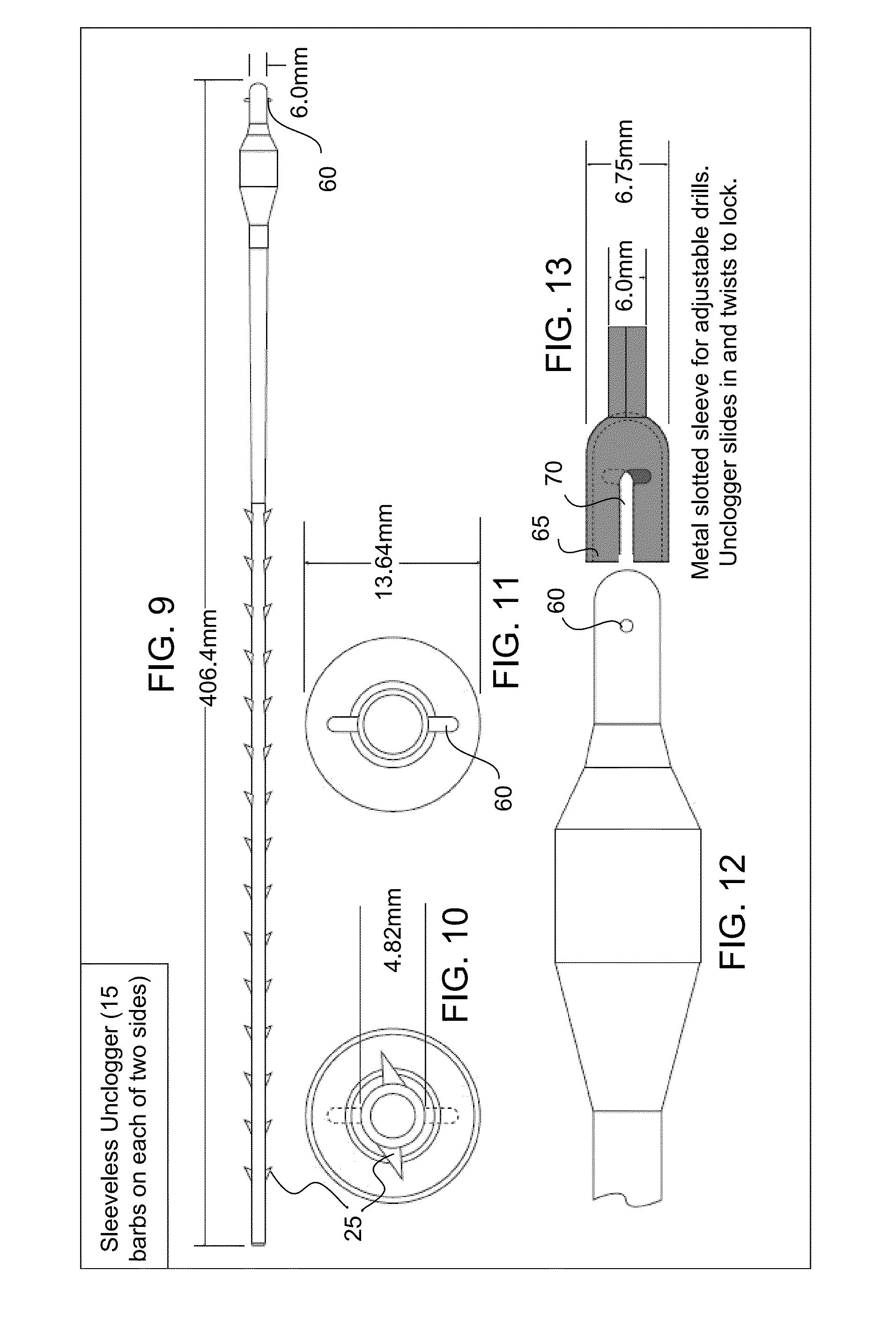

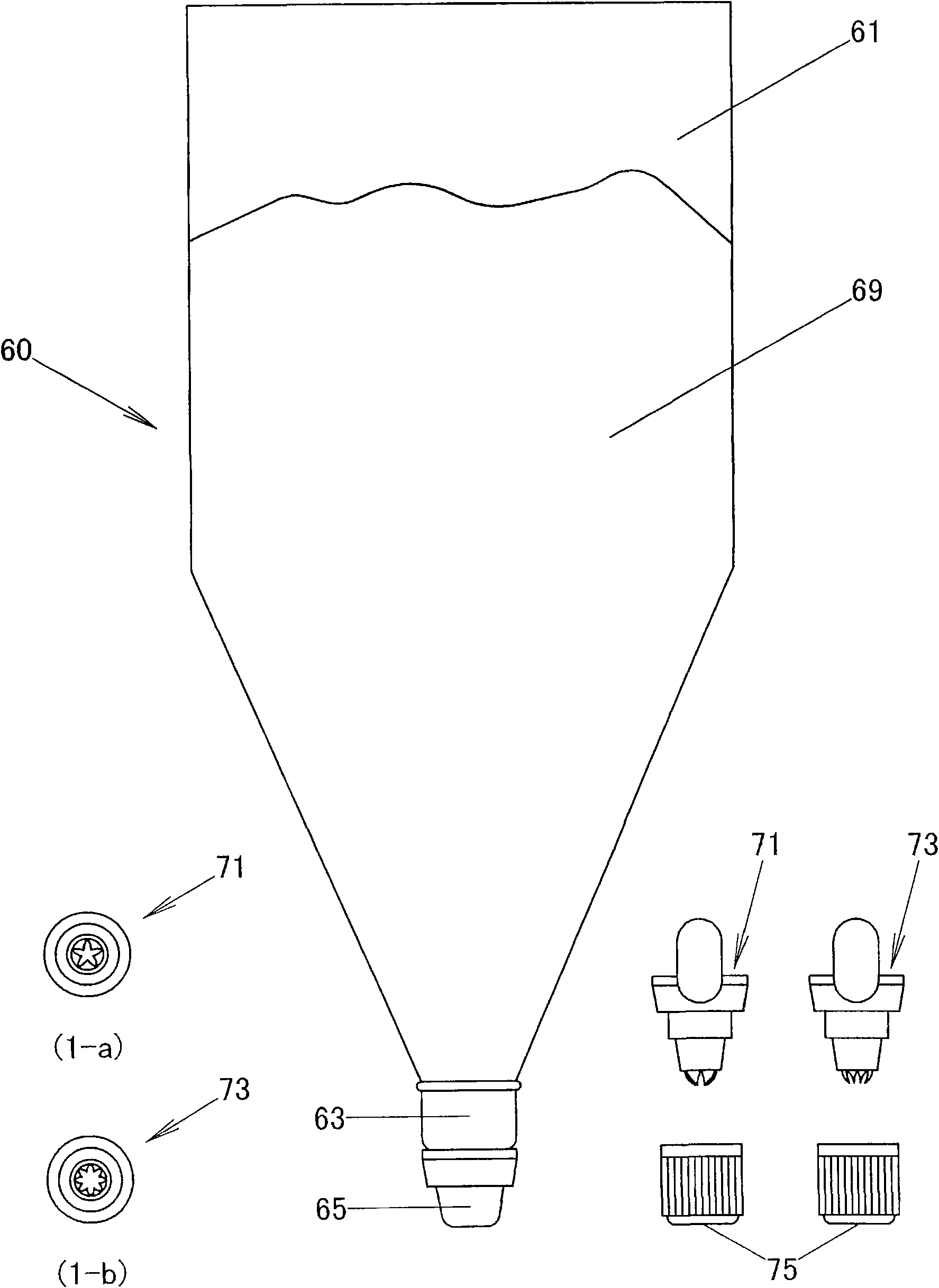

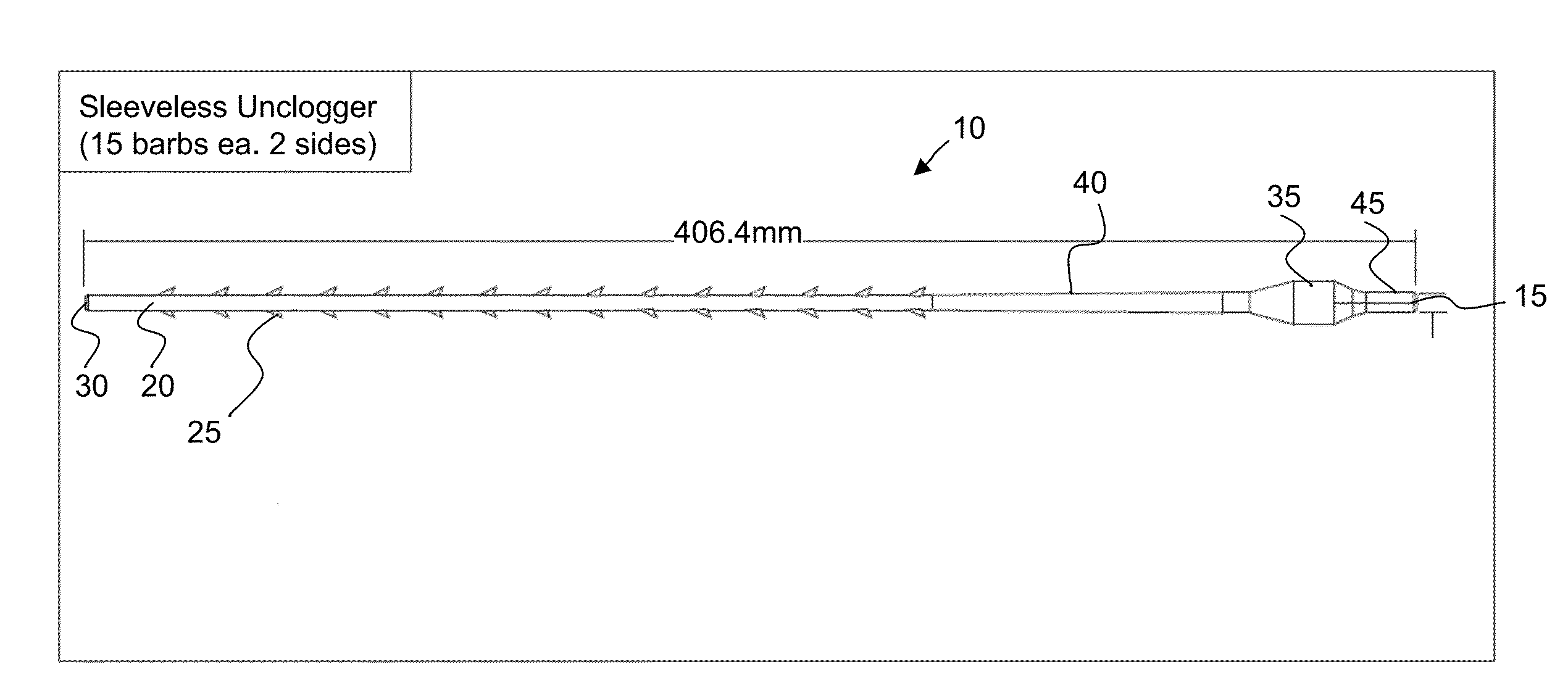

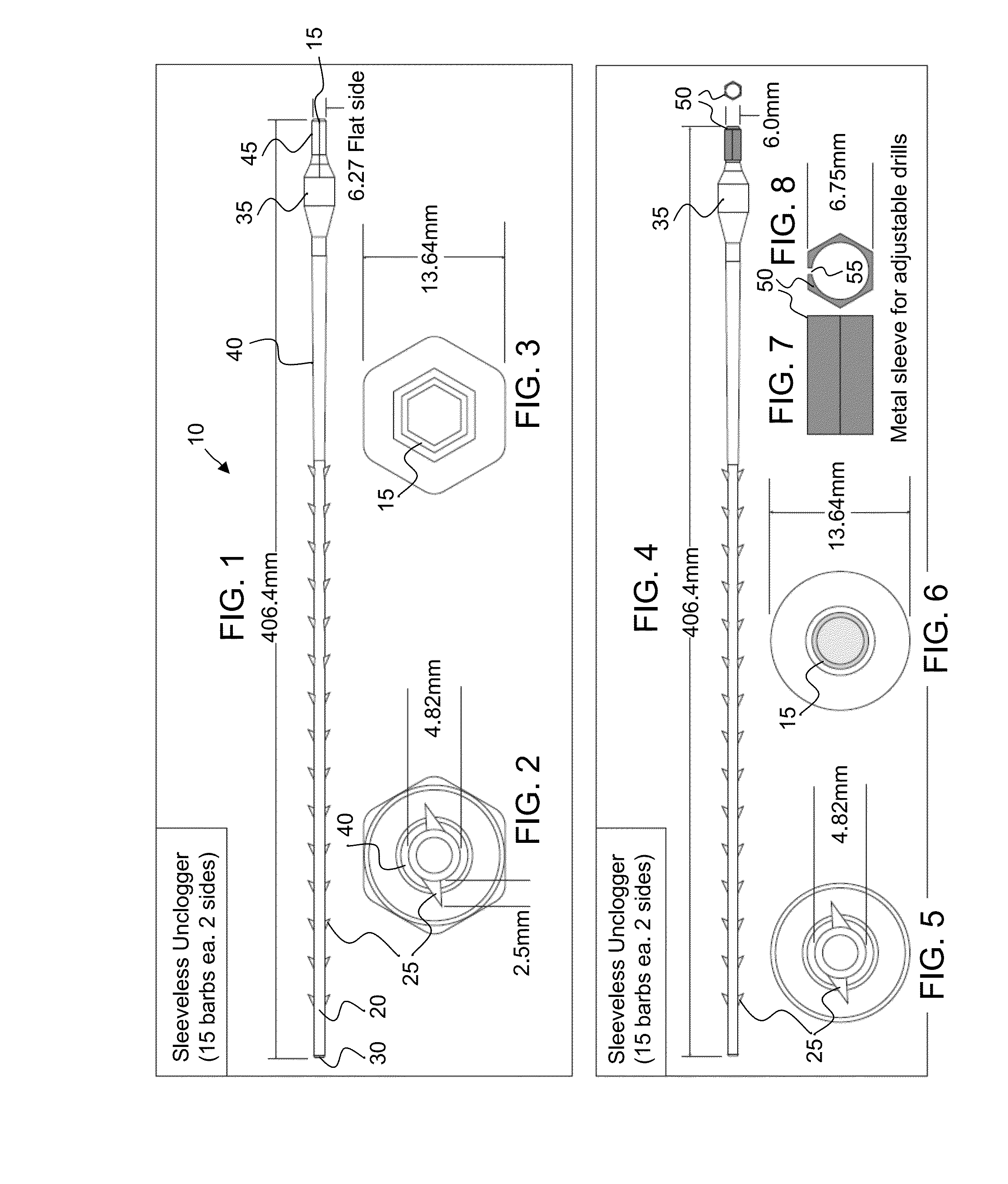

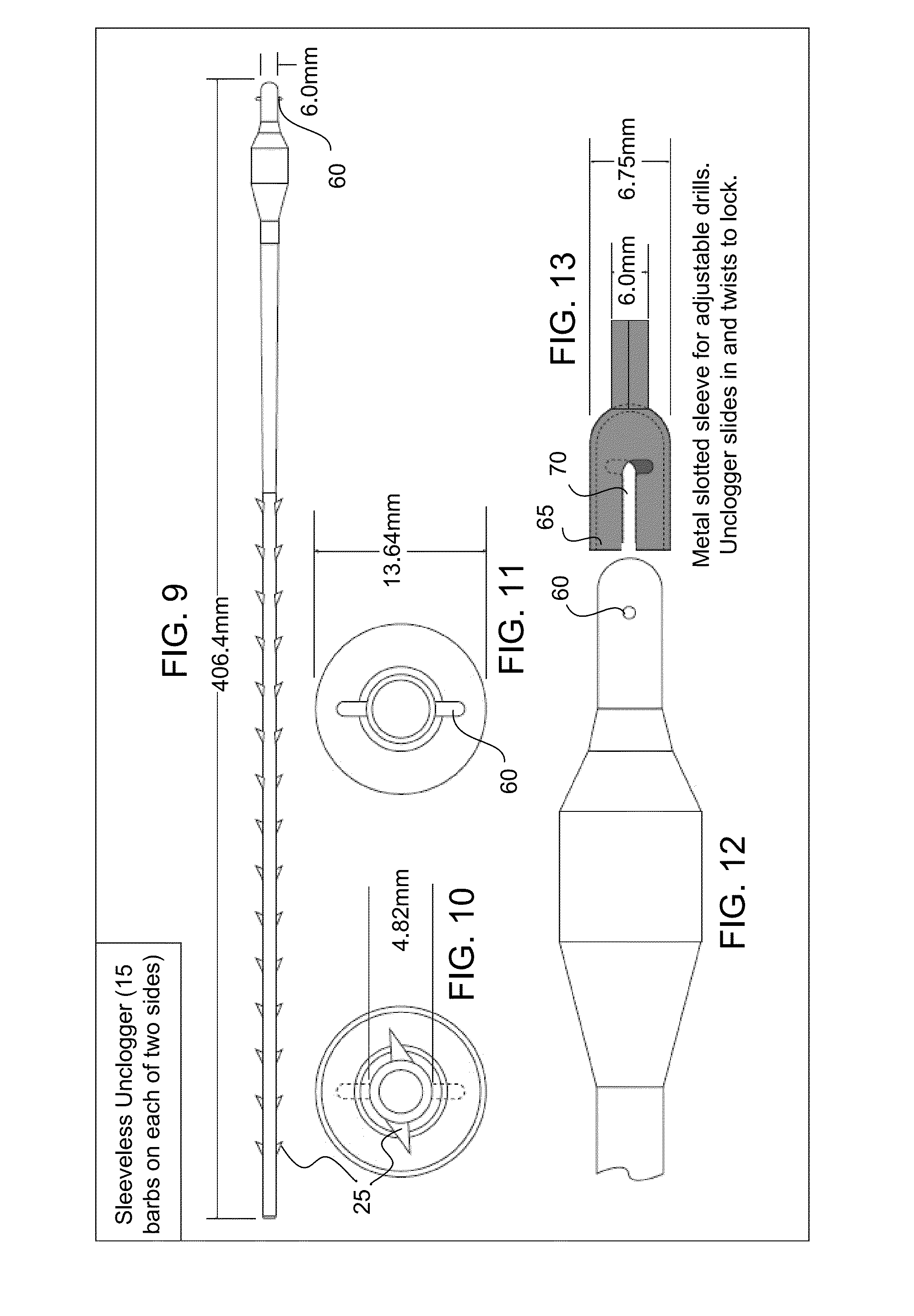

Powered drain unclogging attachment device

A disclosed powered drain unclogging device, system and method comprises a rotational power source and an attachment having a first end detachably coupled to the rotational power source and a second end comprising a plurality of protrusions disposed laterally from a tip thereof in a spiral tip pattern and a helical body pattern configured to drive the rotating tip into a drain and grab and retain debris therefrom. The disclosed method comprises driving the rotating tip into a drain based on an interaction of the spiral arrangement of the protrusions proximal the tip with an inside of the drain walls. The method further includes unclogging debris from the drain via a grabbing and retaining action of the debris by the sharp barbs of the attachment and the driving action thereof. The protrusions comprise bristles and barbs which sway and adjust to varying drain diameters. A splash guard protects the user.

Owner:CHEN ROBERT CV +1

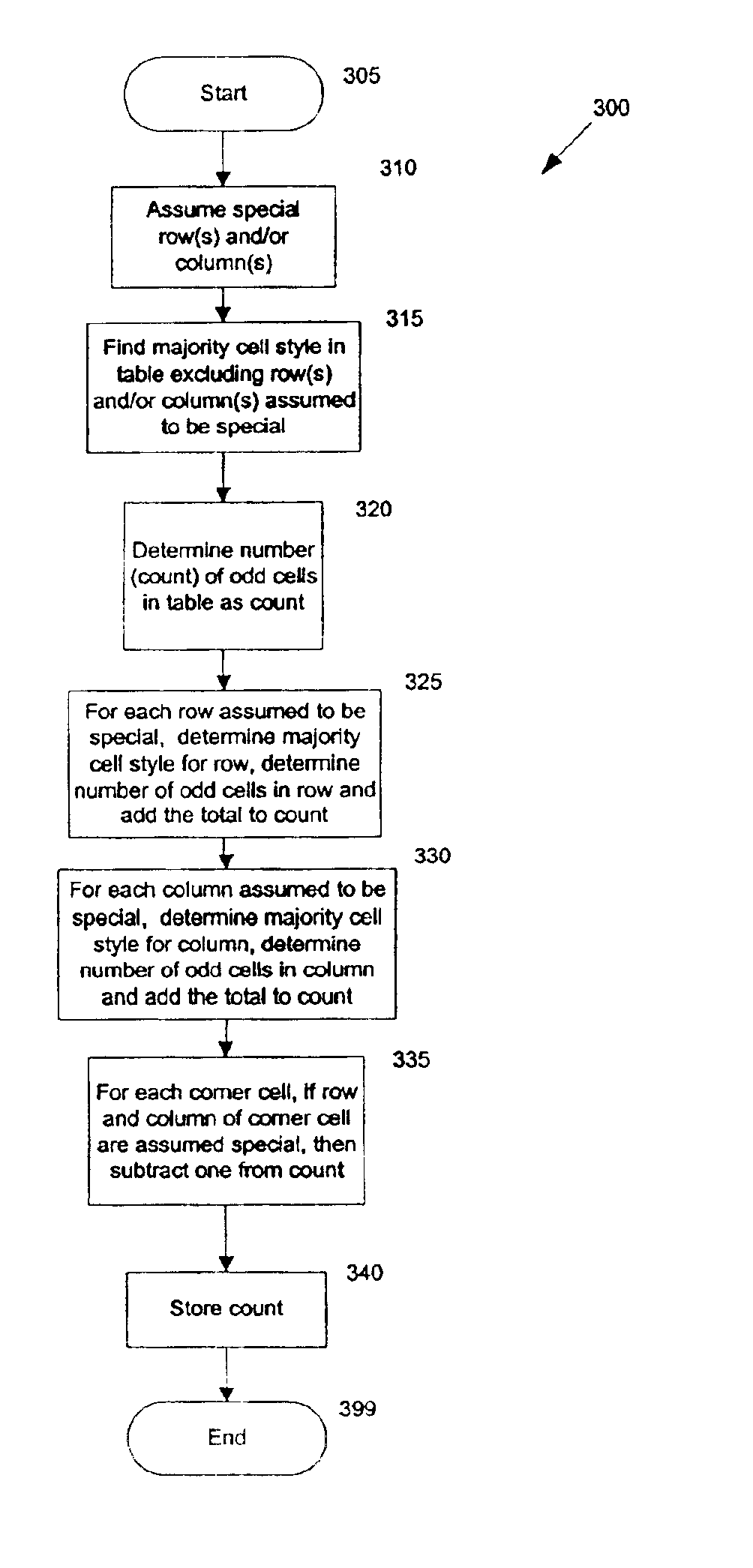

Table styles inference engine

InactiveUS20050120297A1Natural language data processingSpecial data processing applicationsPattern recognitionBody Patterning

A table styles inference engine is described to determine the optimal body pattern to describe a user-created table. In order to achieve compatibility with existing table styles, an optimal uniform body pattern, an optimal row banding pattern and an optimal column banding pattern are determined. The user-defined table is analyzed assuming different uniform body patterns. The optimal uniform body pattern is then determined by determining the uniform body pattern that most closely matches the user-defined table. The user-defined table is also analyzed assuming different row banding body patterns. The optimal row banding body pattern is then determined by determining the row banding body pattern that most closely matches the user-defined table. The user-defined table is also analyzed assuming different column banding body patterns. The optimal column banding body pattern is then determined by determining the column banding body pattern that most closely matches the user-defined table. From these optimal body patterns, the closest match to the user-defined table is determined to be the overall optimal body pattern. The overall optimal body pattern is then saved as a table style.

Owner:MICROSOFT TECH LICENSING LLC

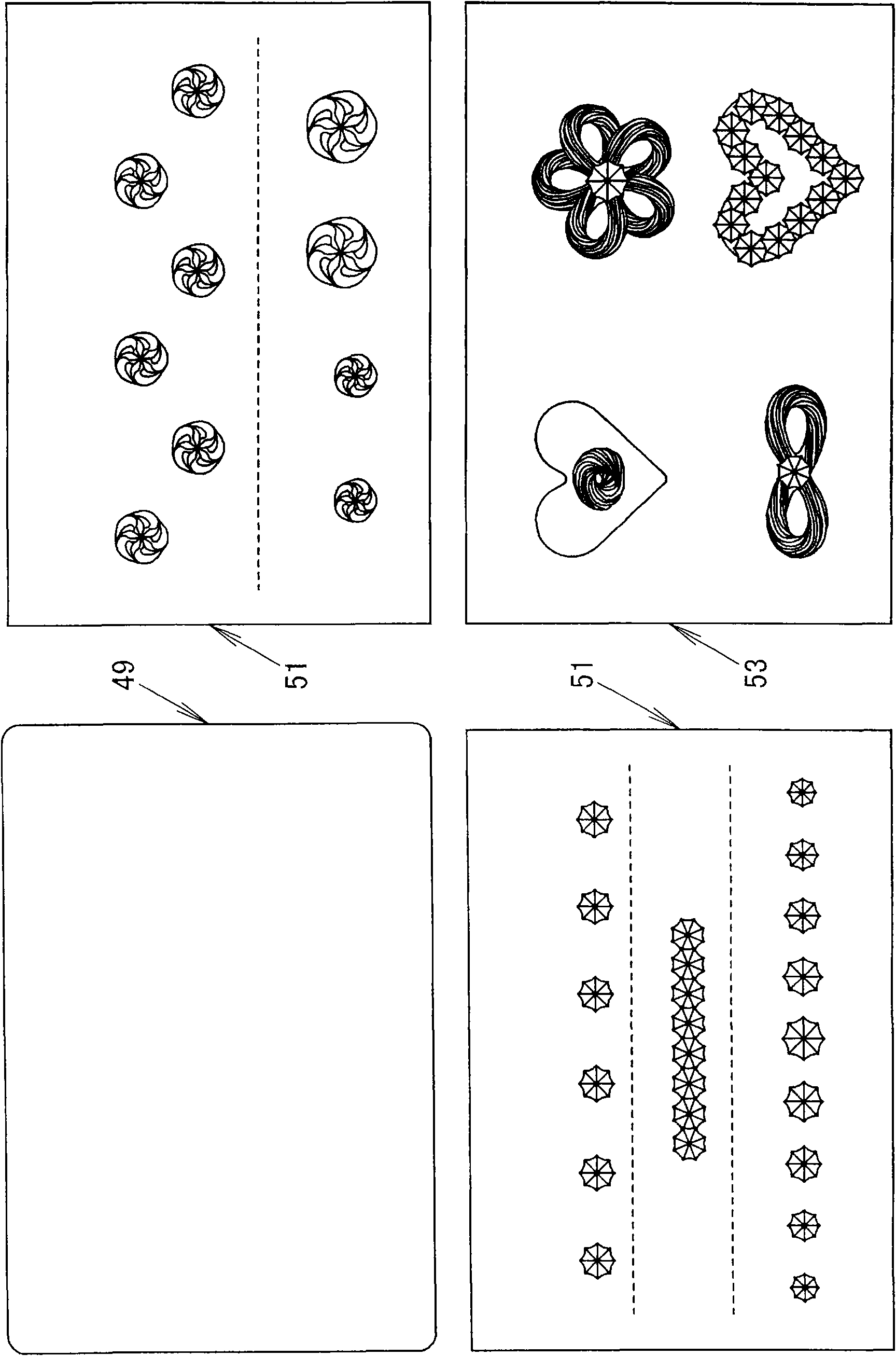

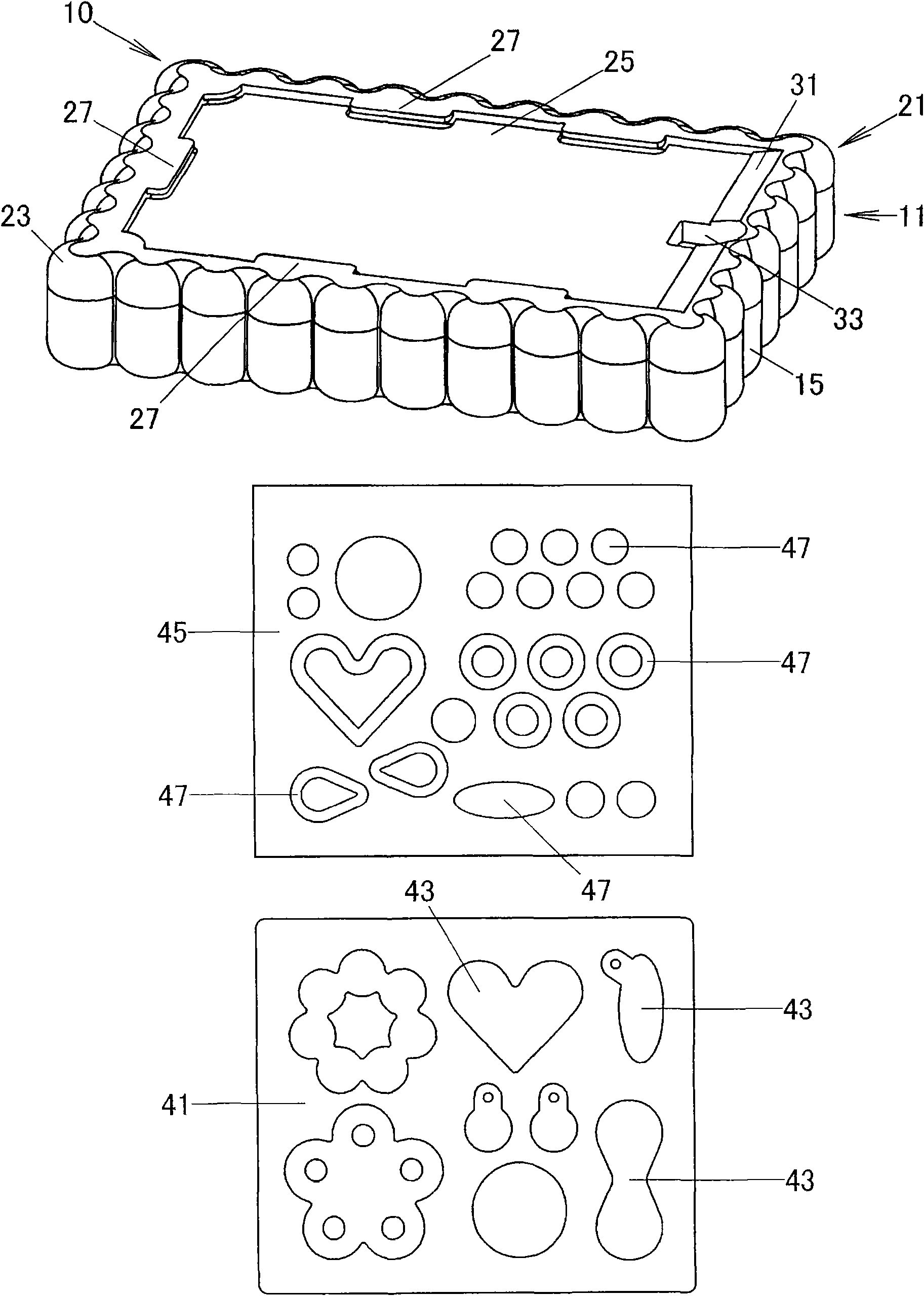

Shaping combination of decorative body toys

The present invention is capable of simply preparing a pretty food toy simulating the appearance of cakes and the like and forming a decorative body toy having strong decoration and simulating the food shape. The shaping combination of decorative body toys is provided with in structure: a resin barrel filled with foaming cream shape special synthetic resin namely cream resin is arranged in a cylinder container, the front end having through holes of the resin barrel is provided with a through hole cap in an assembling and disassembling mode, a shaping plate capable of cutting into a plurality of reinforcing plates with different shapes, sticking pieces with shapes and sizes corresponding with the shapes of the reinforcing plates, formworks with shaping objects namely decorative body patterns corresponding with the reinforcing plates shapes, and bases for placing the reinforcing plates cutting from the shaping plate.

Owner:EPOCH CO

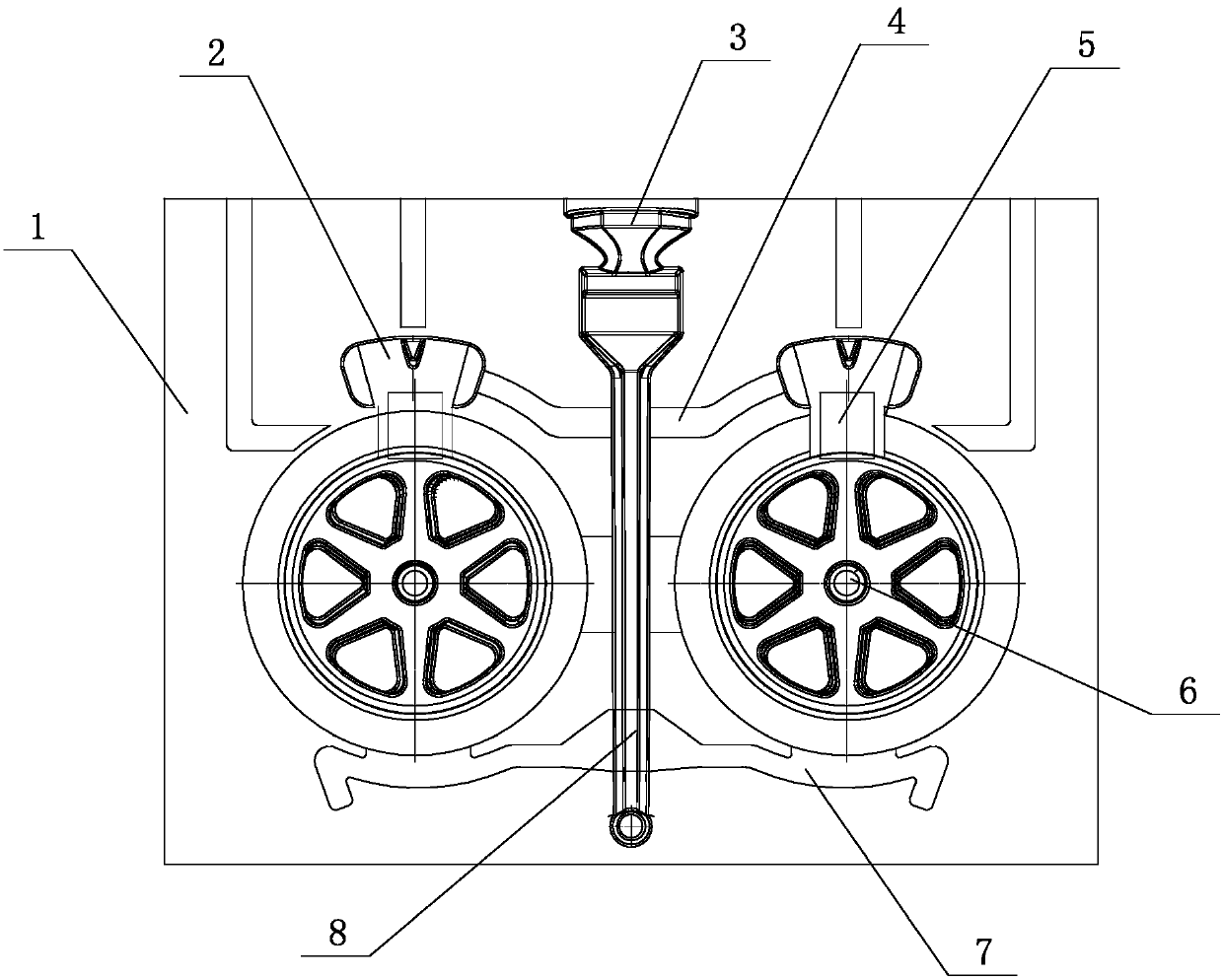

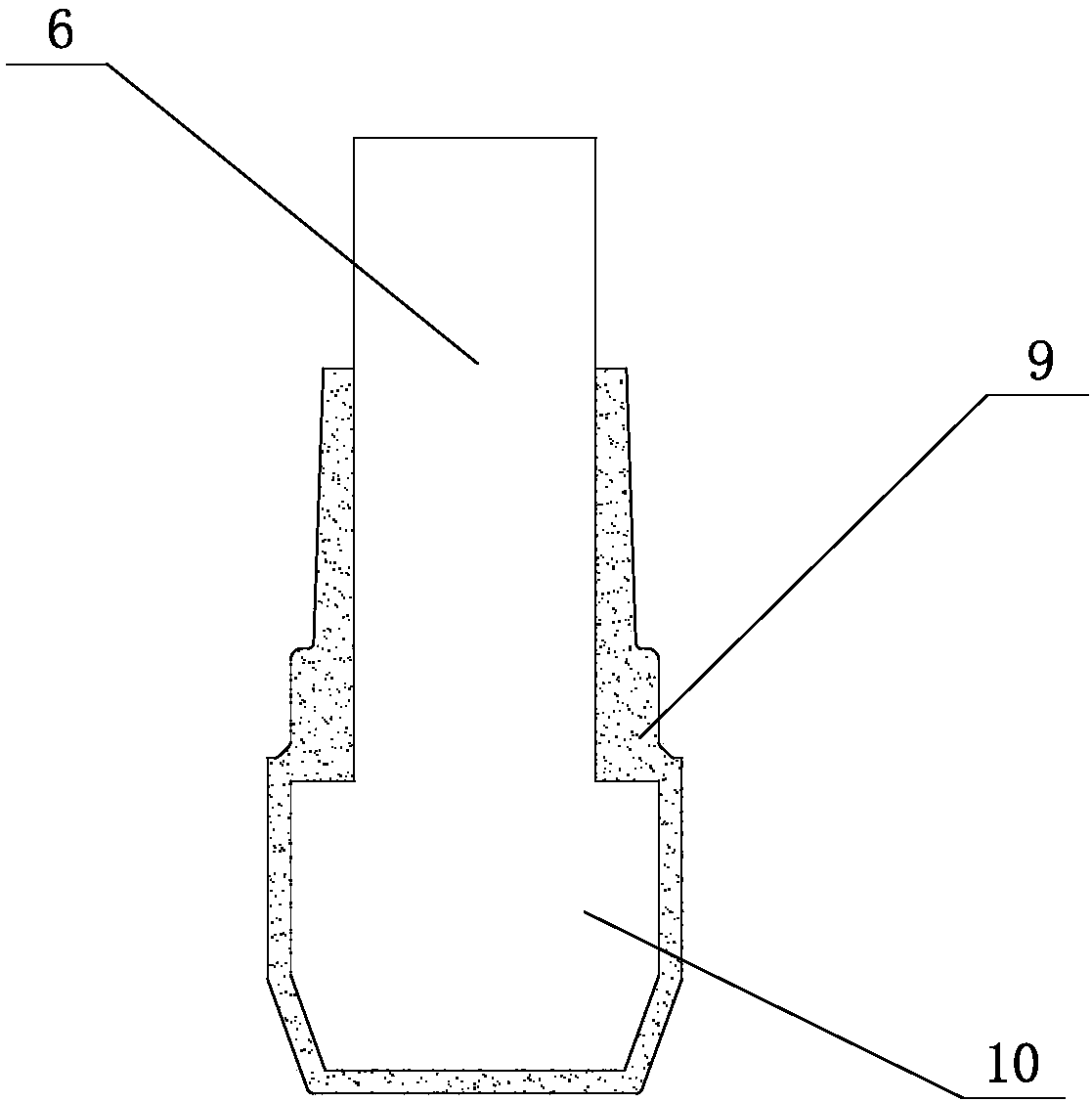

Hub template and hub casting process

InactiveCN107695306AHigh precisionEasy to separateFoundry mouldsFoundry coresBody PatterningEngineering

The present invention relates to the technical field of wheel hub casting, in particular to a wheel hub pattern plate and a wheel hub casting process. The lower end is connected with the middle sprue, the upper sprue is arranged on both sides of the upper part of the middle sprue, the end of the upper sprue is connected with the riser, the riser is connected with the hub shape through the riser neck, and the two sides of the lower part of the middle sprue are set The down runner is connected with the hub shape; the center hole of the hub shape is provided with a cold iron; the invention enlarges the riser, increases the down runner, speeds up the pouring speed, improves the feeding effect, and the product is qualified The rate is high; there are few rough processing parts, only the iron supplement parts need to be processed; the cooling iron is added, and measures to accelerate the cooling of castings can be used to improve the internal shrinkage and shrinkage defects of the product.

Owner:SHANDONG MEILING CHEM EQUIP

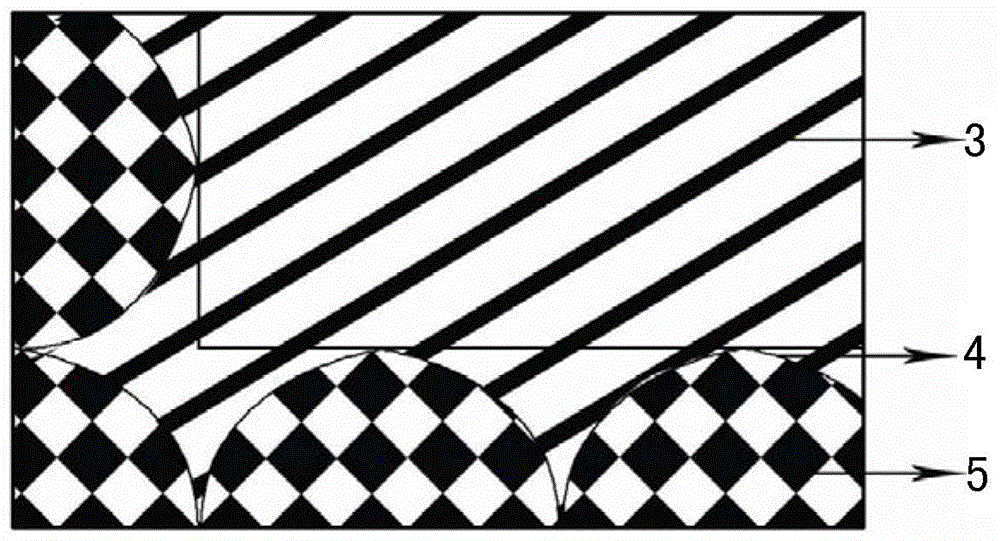

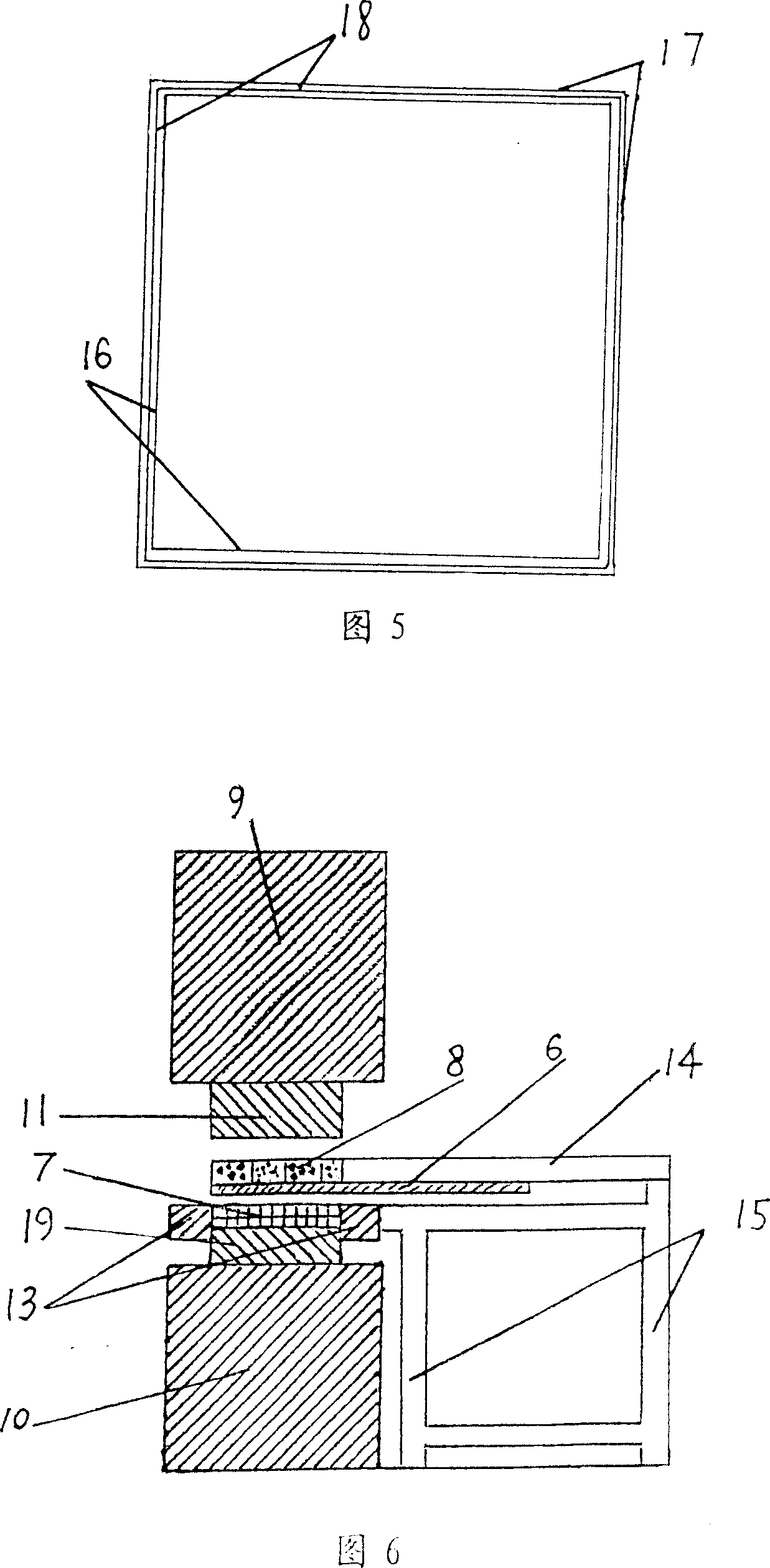

Preparation method for mono-firing embossed ceramic tile

ActiveCN106554156AAchieve three-dimensional effectInsufficient improvementOther printing apparatusSocial benefitsBody Patterning

The invention relates to a preparation method for a mono-firing embossed ceramic tile. The mono-firing embossed ceramic tile comprises a main tile body and an embossed tile body. The preparation method comprises the following steps that (1) a ground coat is applied to a billet; (2) main tile body pattern printing and embossed tile body pattern printing are conducted on the billet coated with the bottom coat, and an embossed tile billet is produced; (3) protective glaze is applied to the main tile billet and the embossed tile billet obtained in the step (2); (4) an embossed material corresponding to an embossed tile pattern is printed on the embossed tile billet obtained in the step (3), so that a three-dimensional layer is formed; and (5), the main tile billet obtained in the step (3) and the embossed tile billet obtained in the step (4) are fired, so that the mono-firing main tile body and the mono-firing embossed tile body are obtained. By adoption of the preparation method for the mono-firing embossed ceramic tile, the three-dimensional effect of a tri-firing product embossed tile is achieved, deficiencies of the tri-firing product are overcome, the durability of the product is enhanced, the energy source is saved, the labor cost is lowered, and good economical and social benefits can be obtained.

Owner:MONALISA GRP CO LTD

Powered Drain Unclogging Attachment Device

A disclosed powered drain unclogging device, system and method comprises a rotational power source and an attachment having a first end detachably coupled to the rotational power source and a second end comprising a plurality of protrusions disposed laterally from a tip thereof in a spiral tip pattern and a helical body pattern configured to drive the rotating tip into a drain and grab and retain debris therefrom. The disclosed method comprises driving the rotating tip into a drain based on an interaction of the spiral arrangement of the protrusions proximal the tip with an inside of the drain walls. The method further includes unclogging debris from the drain via a grabbing and retaining action of the debris by the sharp barbs of the attachment and the driving action thereof. The protrusions comprise bristles and barbs which sway and adjust to varying drain diameters. A splash guard protects the user.

Owner:CHEN ROBERT CV +1

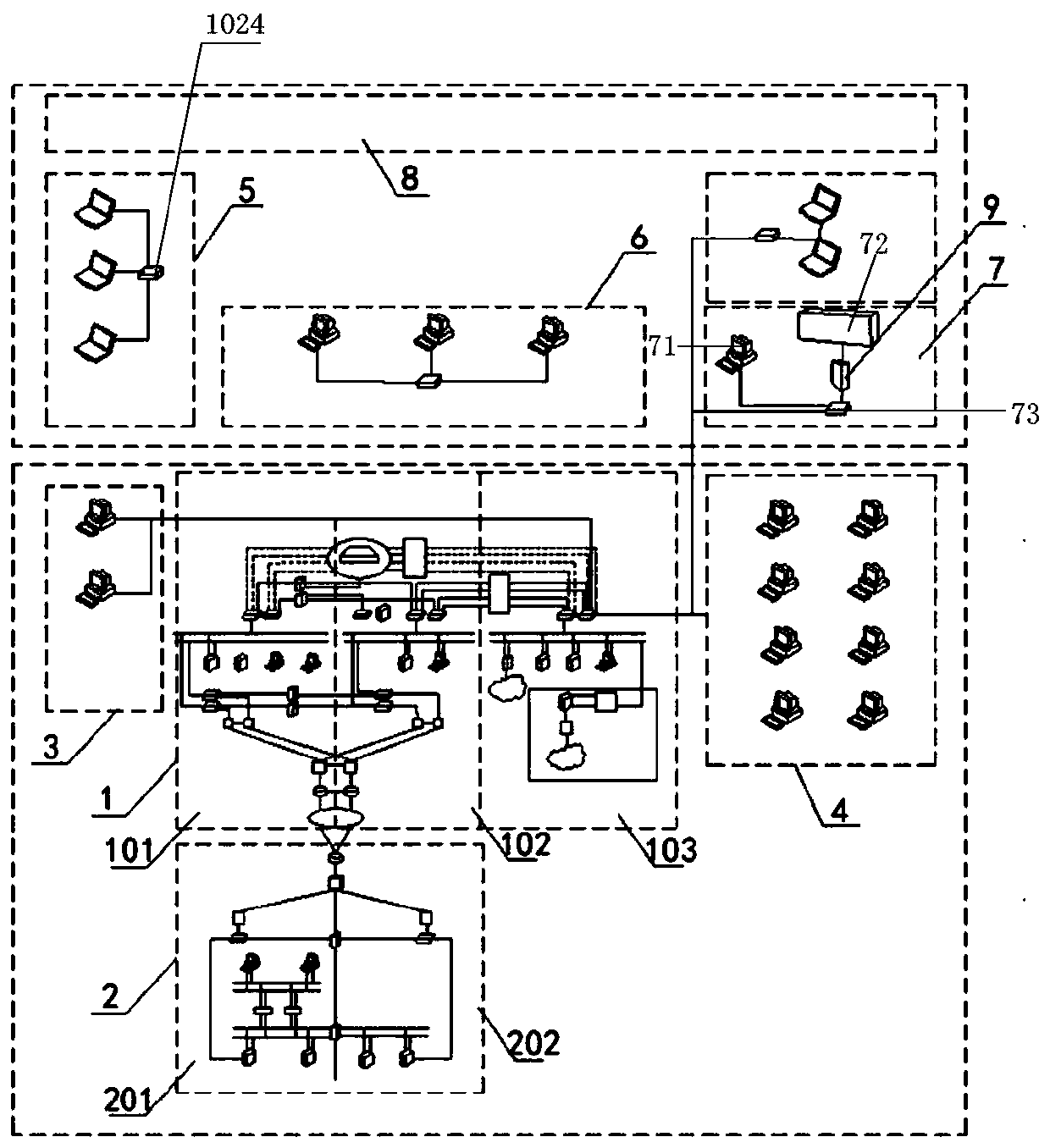

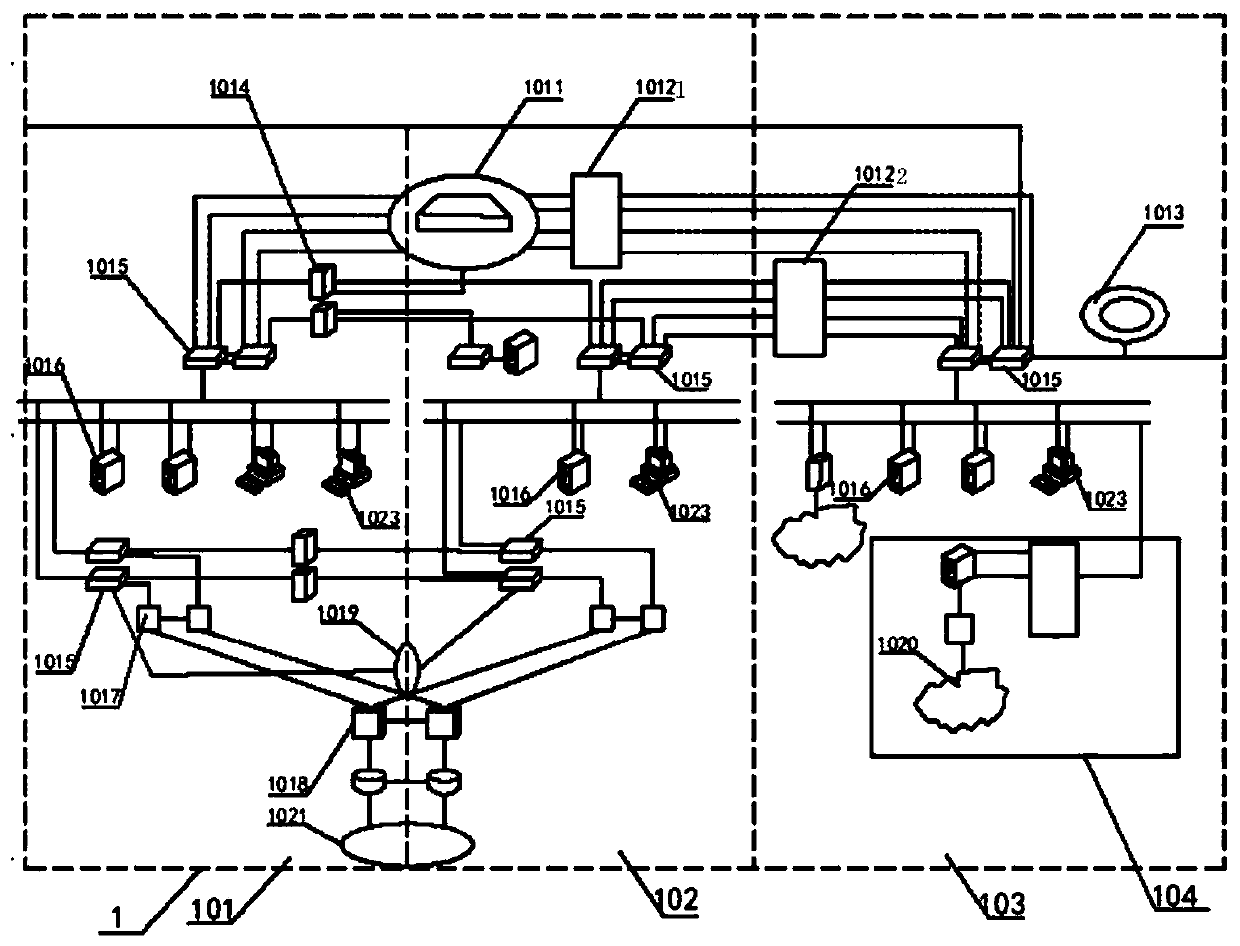

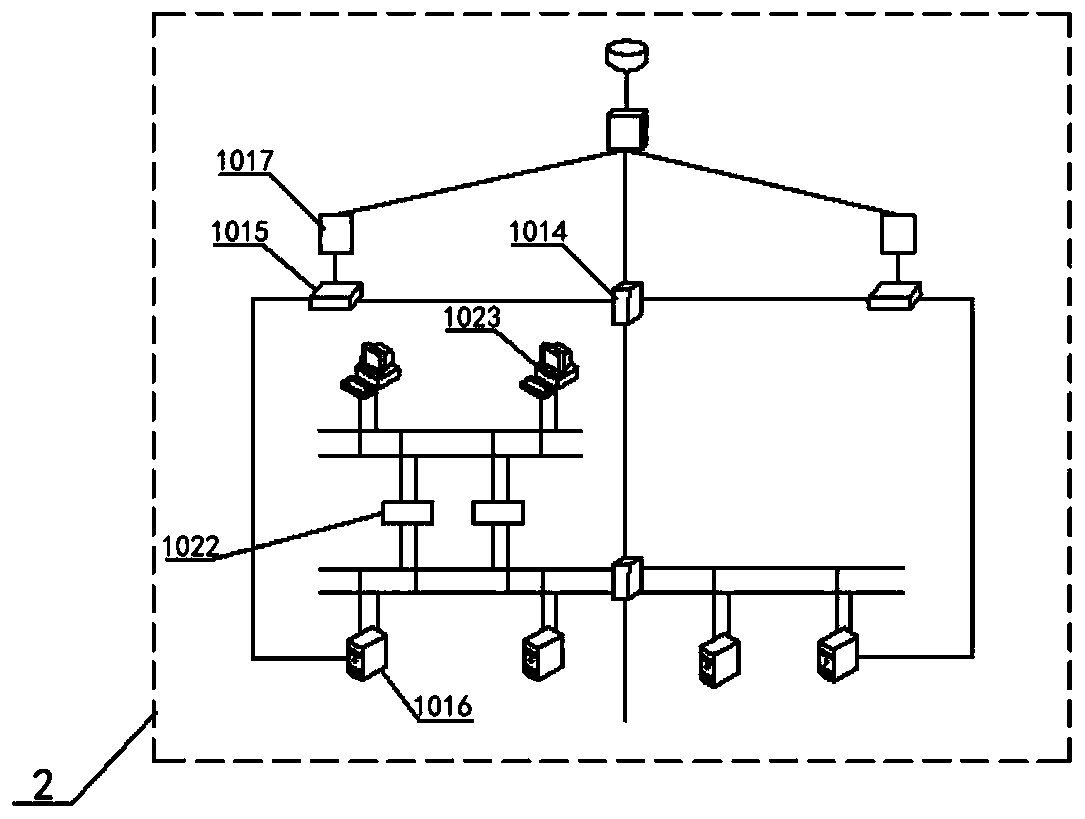

Network security target range system of electric power monitoring system

The invention provides a network security target range system of an electric power monitoring system, which comprises a working area and a machine room area. The working area comprises an attack and defense test area, an electric power monitoring system operation area, a real object target range area and an attack and defense process display area. The machine room area comprises a main station monitoring area, a plant station monitoring area, an attack and defense display monitoring area and a virtual target range machine pool. The system is beneficial for technicians to construct a network security range system which takes a main station monitoring area, a plant station monitoring area, an attack and defense display monitoring area, an attack and defense test area, an electric power monitoring system operation area and a real object range area as a main body pattern. The constructed network security target range system enhances the working association degree and the working coordination degree between the internal unit areas, so that the system pattern tends to be clear, the security degree is improved, and the strain capacity is also improved. The attack and defense target rangecombining virtuality and reality is adopted, the virtual target range with rapid deployment and recovery capacity is achieved, and the physical target range with high intuition and obvious effect is also achieved.

Owner:YUNNAN POWER GRID CO LTD ELECTRIC POWER RES INST

Large-area anti-fracture plate with 3-D coloured blank pattern and its making method

InactiveCN1952318AObvious advantagesGood effectConstruction materialFeeding arrangmentsGlass fiberFiber

The invention relate to an anti-snapped plate of three-dimensional colored body pattern and the production method. The plate is suitable for ceramics decorated board and glass or microcrystal glass board. The thickness of production is 2mm-30mm and the pattern is made of different colored silicate body with two or three to twenty classes. It is characterized in that there are 3-10000 blocks of two body colored pattern with the area of 4cm2-2m2 at least and the thickness is 0.5mm-30mm; ceramic or glass fiber containing alumina exists in the body structure. Said body colored pattern has two different colored areas at least, which are easily differentiable, and the form of 2 of 3-10000 patterns at least is set by the pattern die.

Owner:杨德宁

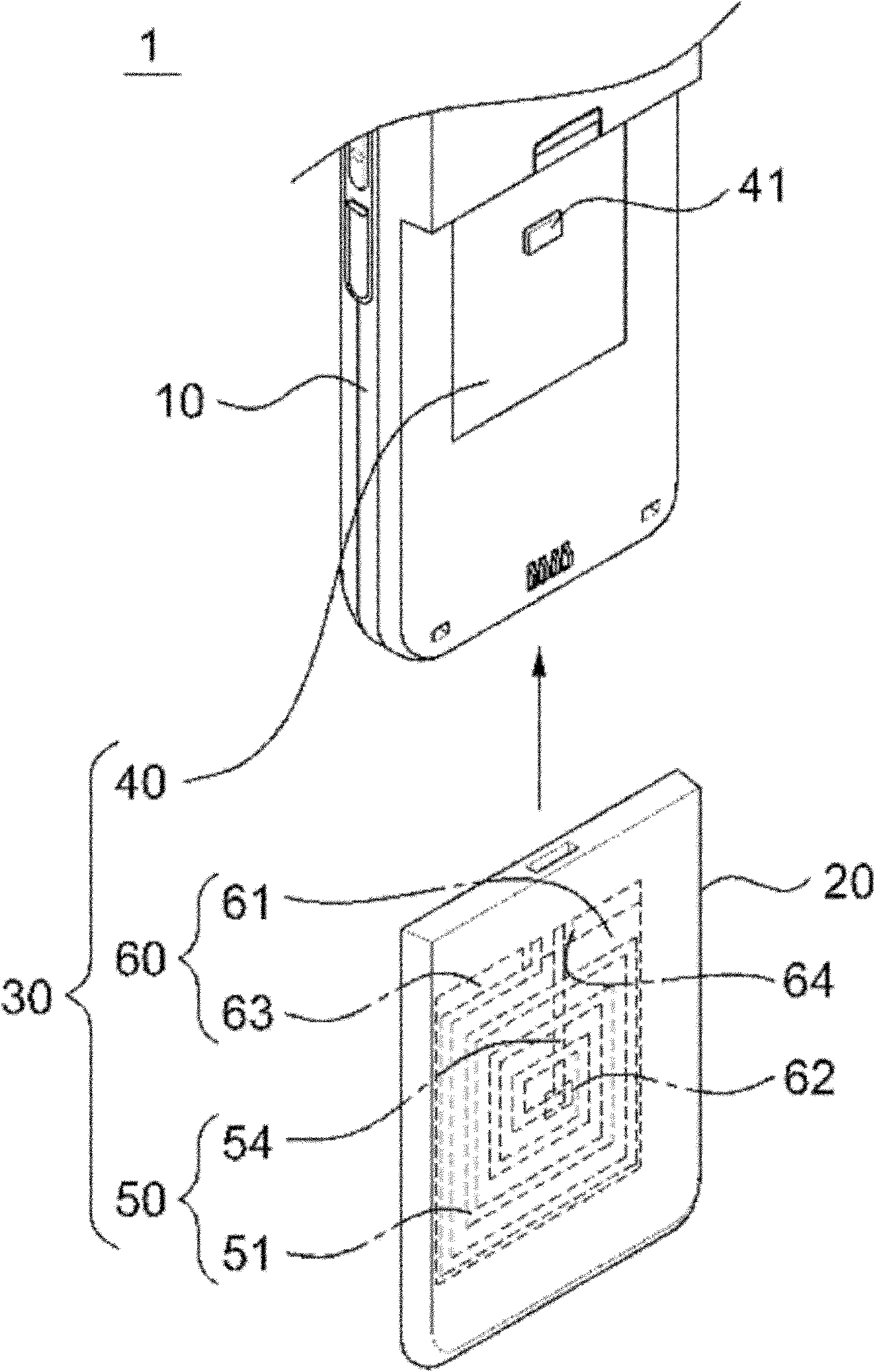

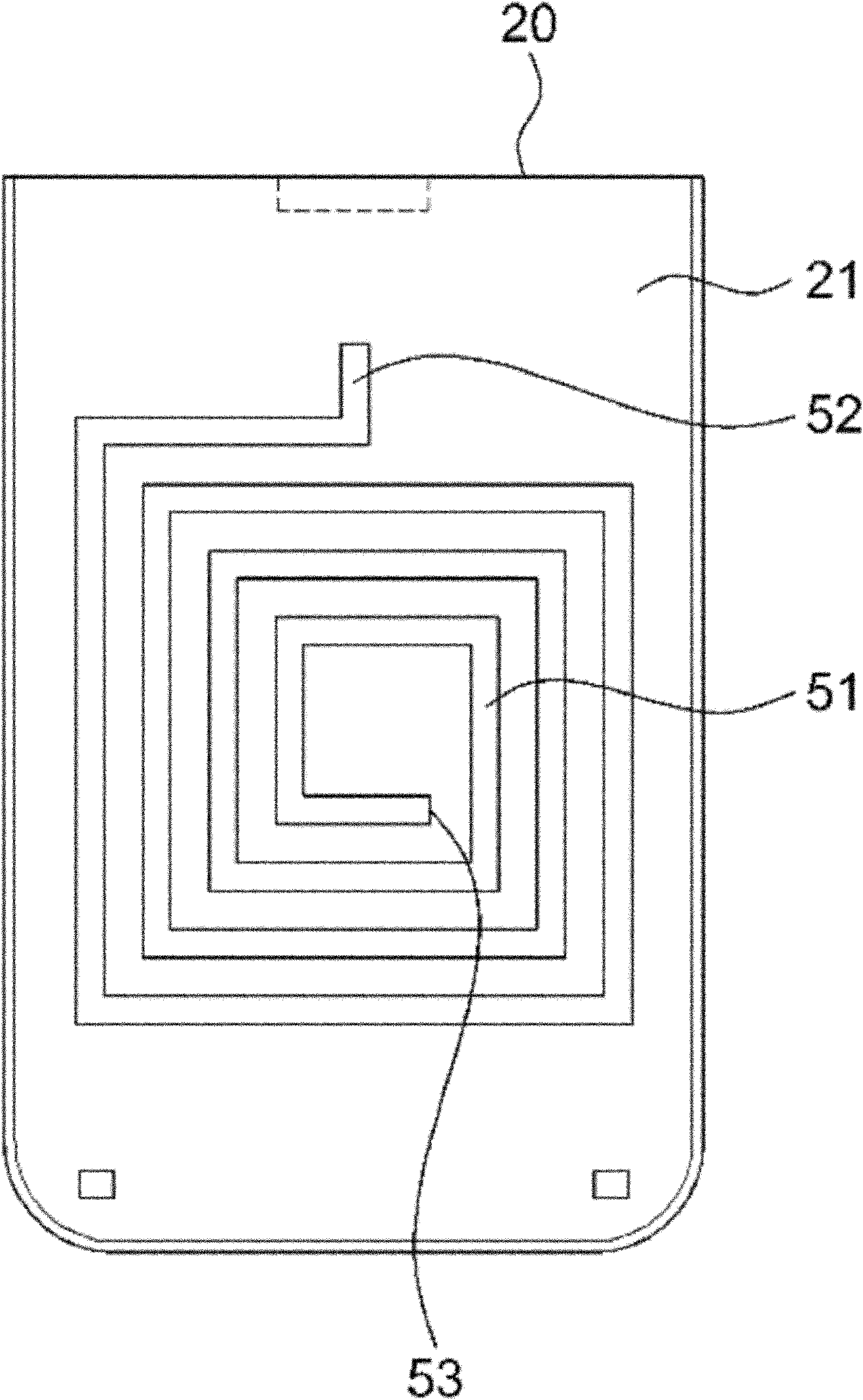

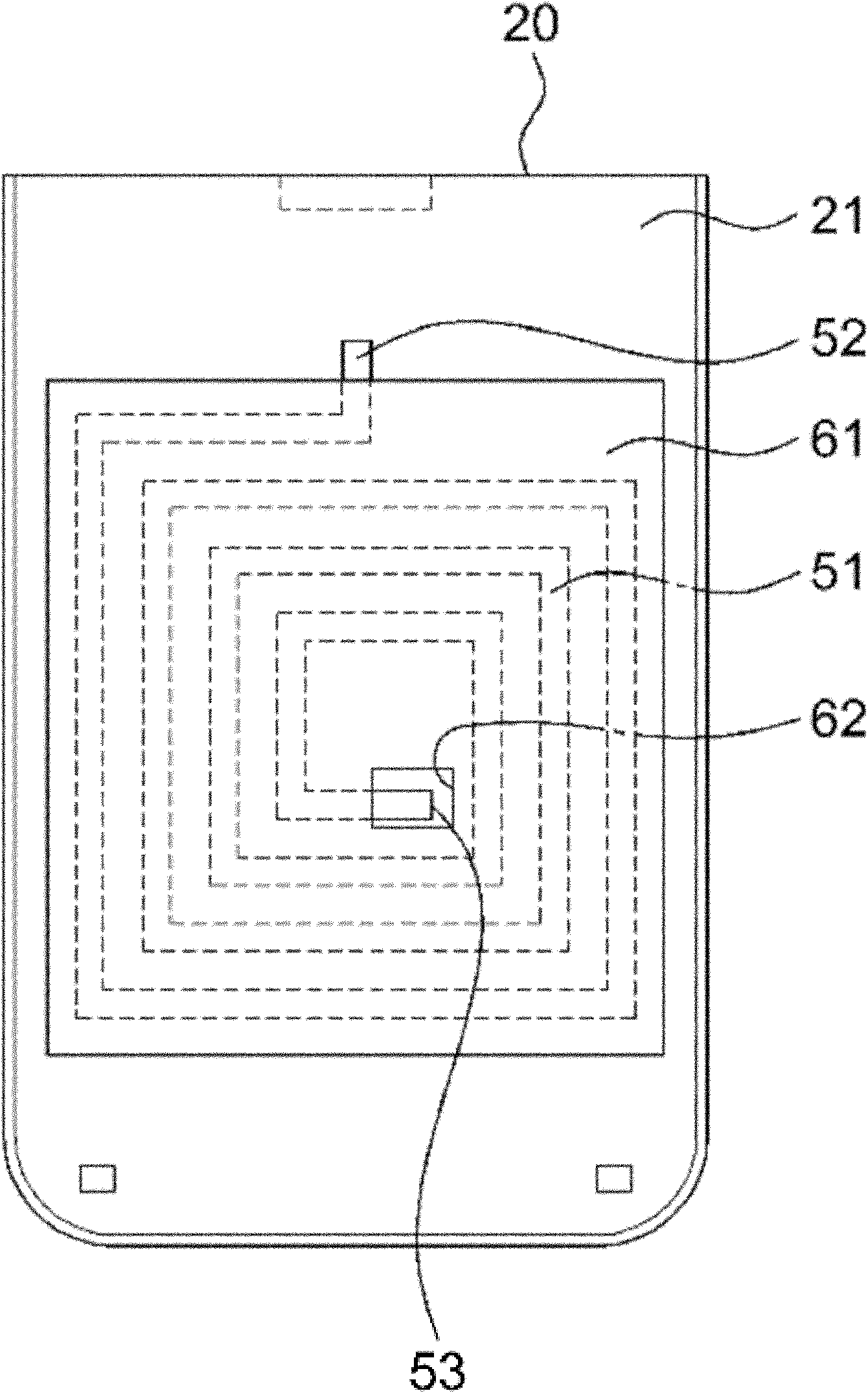

Internal antenna for a wireless device, and a production method therefor

InactiveCN102106037ASimplify the manufacturing processMiniaturizationRadiating elements structural formsProtective material radiating elementsElectricityBody Patterning

The present invention relates to an internal antenna for a wireless device which can be formed by means of pattern printing, and to a production method therefor. The internal antenna for a wireless device according to the present invention comprises: a substrate accommodated in the wireless device; a radio unit which is printed onto the inner surface of the housing of the wireless device, and which is connected to the substrate, and which also sends and receives electrical signals; and an insulating unit which is printed onto the radio unit, and which insulates the radio unit. Here, the radio unit comprises first and second radio bodies pattern printed in sequence on the inner surface of the housing, while the insulating unit comprises first and second insulating bodies printed in such a way as to cover the first and second radio bodies in sequence. This arrangement makes it possible to form the radio unit and the insulating unit to a minimum thickness by means of pattern printing, and thus to minimise the size of the internal antenna in the wireless device.

Owner:EMW CO LTD

Method of fabricating T-type gate

InactiveUS7141464B2Easy to manufactureIncrease productionSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing cost reductionCross-link

Provided is a method of fabricating a T-type gate including the steps of: forming a first photoresist layer, a blocking layer and a second photoresist layer to a predetermined thickness on a substrate, respectively; forming a body pattern of a T-type gate on the second photoresist layer and the blocking layer; exposing a predetermined portion of the second photoresist layer to form a head pattern of the T-type gate, and performing a heat treatment process to generate cross linking at a predetermined region of the second photoresist layer except for the head pattern of the T-type gate; performing an exposure process on an entire surface of the resultant structure, and then removing the exposed portion; and forming a metal layer of a predetermined thickness on an entire surface of the resultant structure, and then removing the first photoresist layer, the blocking layer, the predetermined region of the second photoresist layer in which the cross linking are generated, and the metal layer, whereby it is possible to readily perform a compound semiconductor device manufacturing process, and to reduce manufacturing cost by means of the increase of manufacturing yield and the simplification of manufacturing processes.

Owner:ELECTRONICS & TELECOMM RES INST

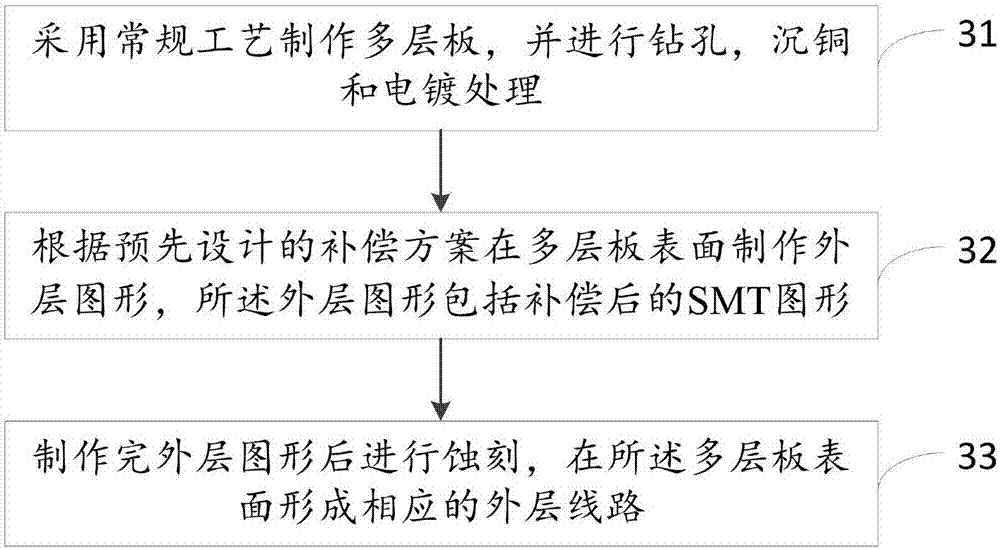

Method for manufacturing millimeter-wave radar PCB

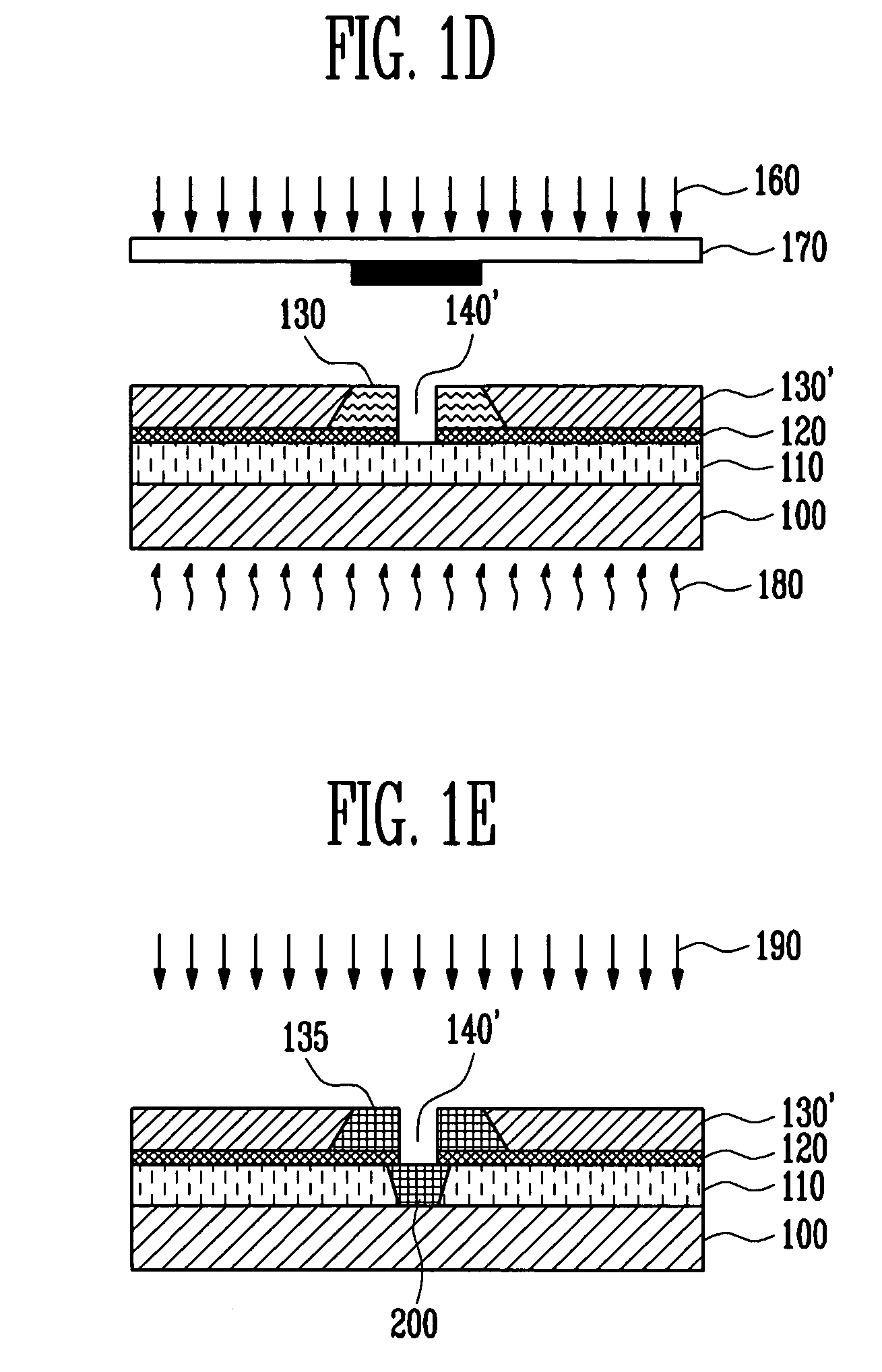

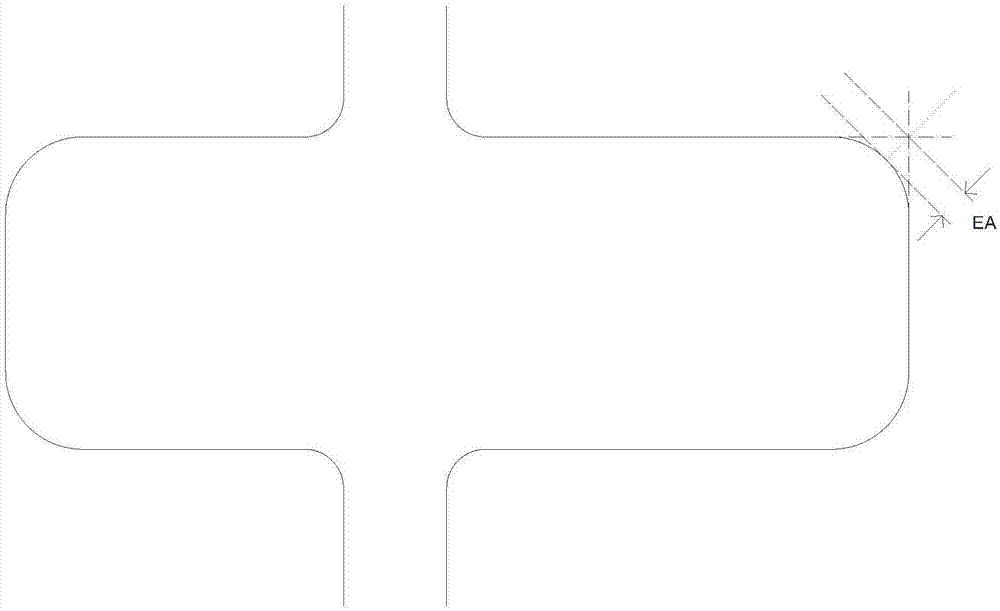

InactiveCN108012432AMeet the requirements of EA value ≤10umPrinted circuit aspectsConductive material chemical/electrolytical removalBody PatterningCopper

The invention discloses a method for manufacturing a millimeter-wave radar PCB. The method comprises the steps of manufacturing a multi-layer board by adopting a conventional process and carrying outdrilling, copper precipitation and electroplating treatment; manufacturing an outer pattern on the surface of the multi-layer board according to a pre-designed compensation scheme, wherein the outer pattern comprises a compensated SMT pattern; the compensated SMT pattern comprises an SMT body pattern, a conventional compensated pattern which surrounds the periphery of the SMT body pattern and is connected to the periphery of the SMT body pattern, and an additional compensated pattern located at the corner of the SMT body pattern; and the additional compensated pattern is a circular compensatedpattern; and etching after manufacturing the outer pattern and forming a corresponding outer circuit on the surface of the multi-layer board. According to the method disclosed by the embodiment of the invention, the outer pattern is designed and manufactured by adopting the special compensation scheme and the requirement that the EA value at the corner of the outer SMT pattern is smaller than orequal to 10mum can be met.

Owner:SHENNAN CIRCUITS