MOS Transistor Gates with Doped Silicide and Methods for Making the Same

a technology of mos transistor gates and doped silicide, which is applied in the direction of transistors, semiconductor devices, electrical equipment, etc., can solve the problems of gate leakage current tunneling through, limited ability to form very thin oxide films with uniform thickness, and electrical and physical limitations on the extent to which siosub>2 /sub>gate dielectrics can be made thinner, etc., to facilitate elimination or simplification of channel engineering and high melting temperature

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

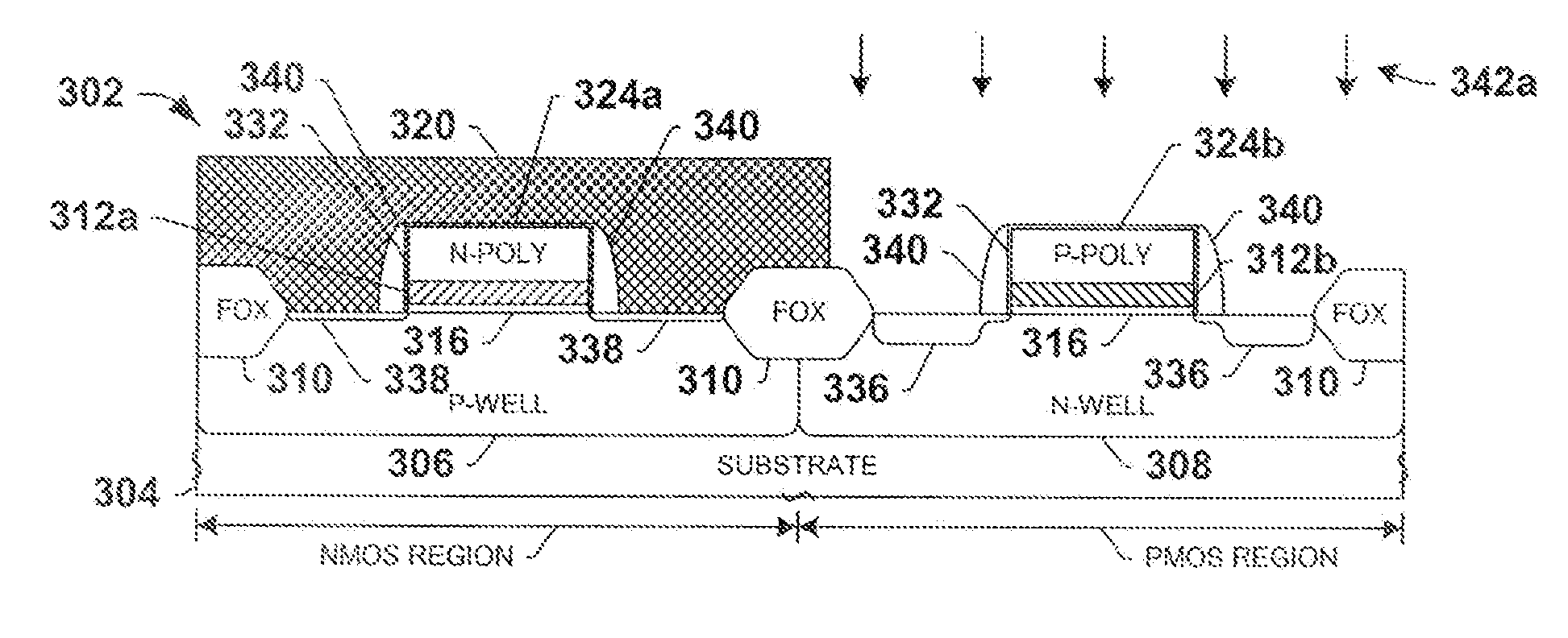

[0028] One or more implementations of the present invention will now be described with reference to the attached drawings, wherein like reference numerals are used to refer to like elements throughout, and wherein the illustrated structures are not necessarily drawn to scale. The invention relates to semiconductor devices, as well as MOS transistor gate structures and fabrication methods therefor, in which first and second metal silicides are formed in a gate structure and the first metal silicide is doped.

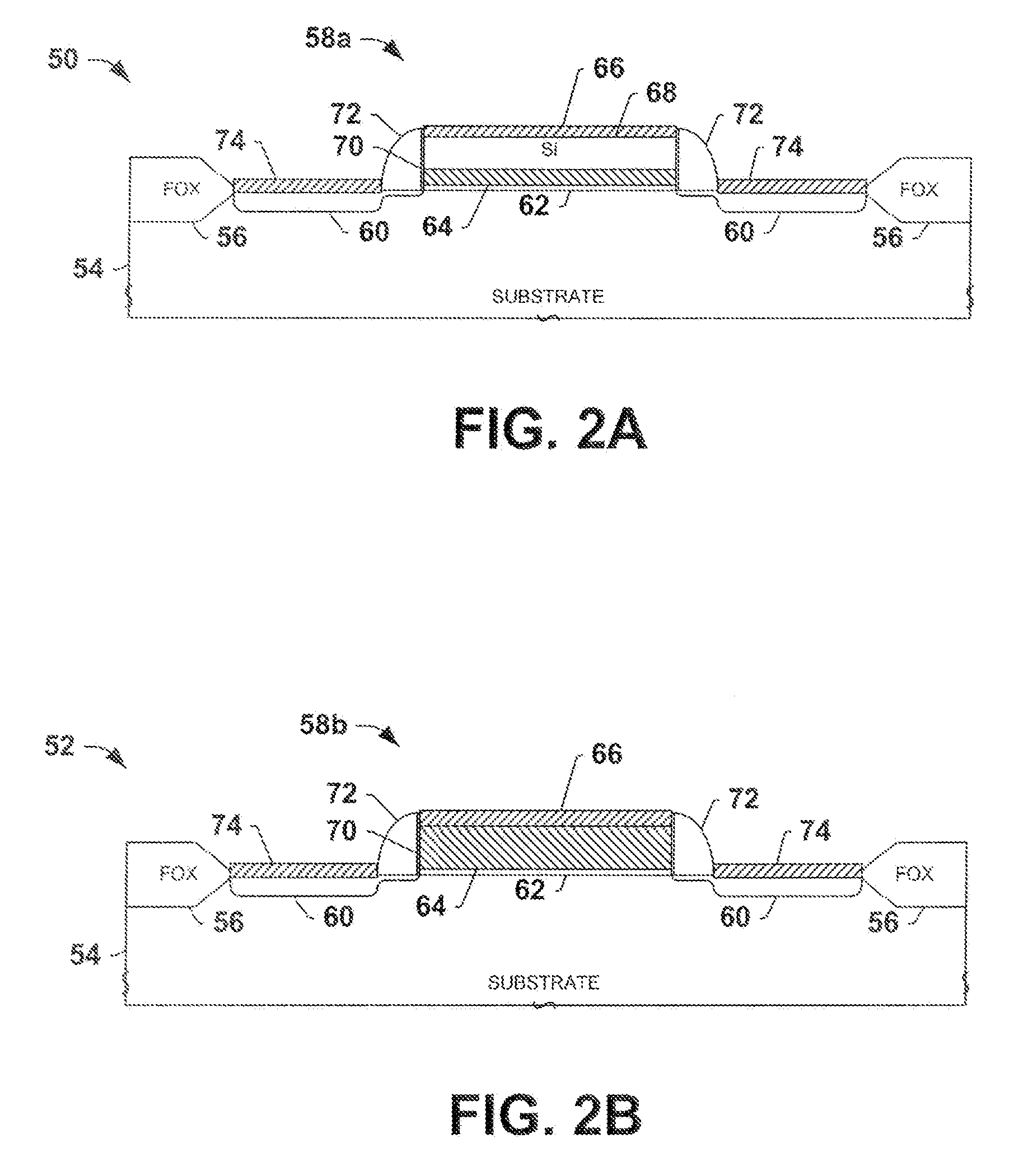

[0029]FIGS. 2A and 2B illustrate exemplary CMOS semiconductor devices 50 and 52, with NMOS transistors 58a and 58b, respectively, having gate structures in accordance with the invention. The devices 50, 52 are fabricated in or on a silicon substrate 54, although the invention may be carried out in association with SOI wafers, epitaxial silicon layers formed over silicon wafers, and any other semiconductor body. N-wells, p-wells, and / or buried layers (not shown) may be formed in t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electric field | aaaaa | aaaaa |

| threshold voltage | aaaaa | aaaaa |

| gate voltage | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More