Apparatus and method for processing pretreated microinstruction asynchronous multilayer nest

A micro-instruction and pre-processing technology, which is applied in the direction of concurrent instruction execution, electrical digital data processing, program control design, etc., to achieve the effect of ensuring correct recovery

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

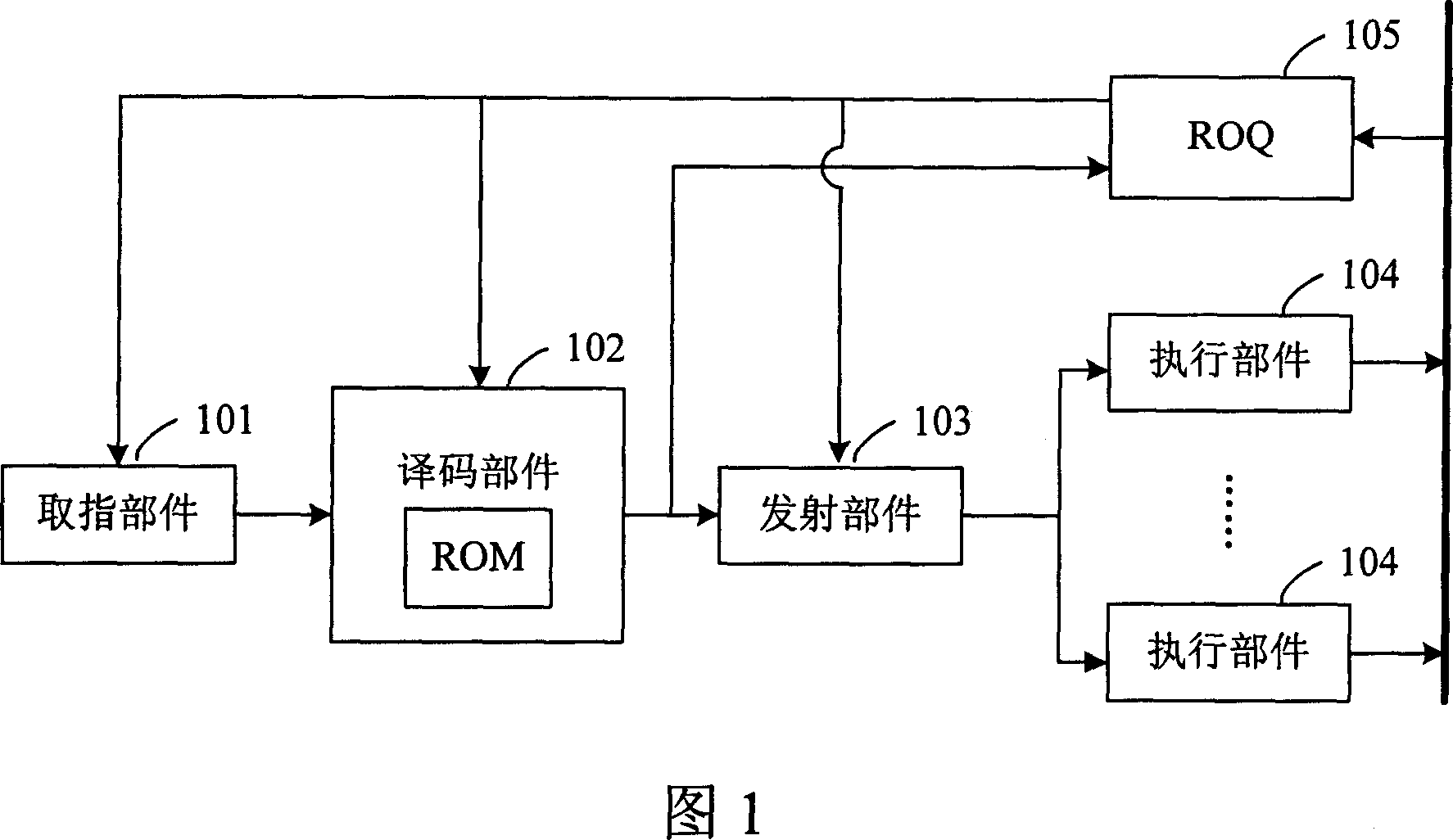

[0057] As shown in FIG. 1 , FIG. 1 is a structural block diagram of a device for processing abnormal multi-layer nesting of preprocessing microinstructions according to the present invention. The equipment provided by the present invention is a central processing unit (CPU) that handles the occurrence of abnormal multi-layer nesting of preprocessing microinstructions. Reorder Buffer (ROQ) 105 .

[0058] Wherein, the instruction fetching unit 101 includes an instruction register, an instruction cache, an instruction bypass buffer, a branch predictor, etc., and the specific composition structure can be adjusted correspondingly according to the complexity of the implemented system. The instruction fetching unit 101 is used ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More