AHB interconnection matrix interface

An interface and matrix technology, applied in the field of AHB interconnection matrix interface, can solve the problems of infeasibility and difficulty in increasing the frequency of the bus system, so as to achieve the effect of increasing the operation efficiency of the matrix and improving the overall operation efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

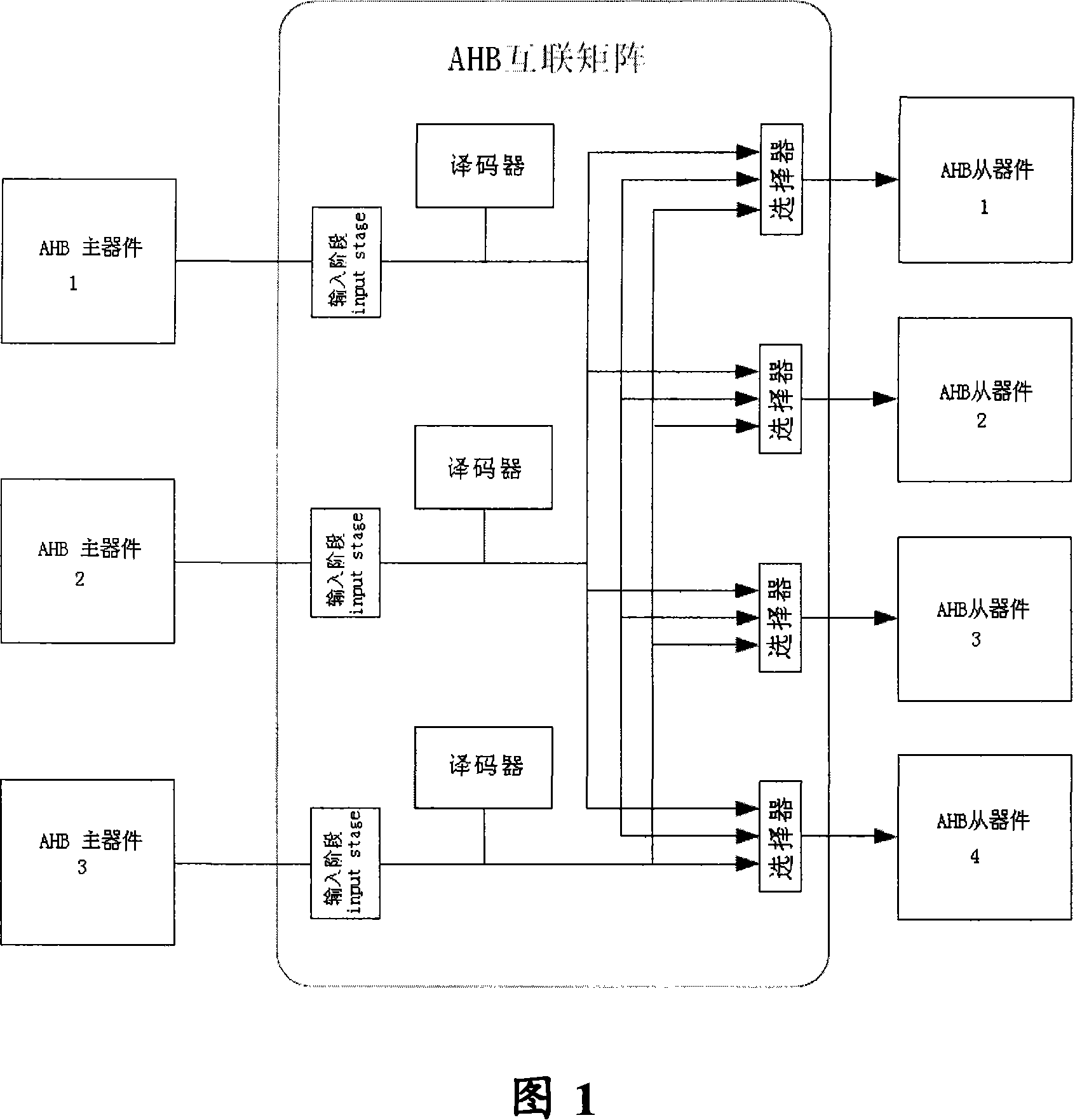

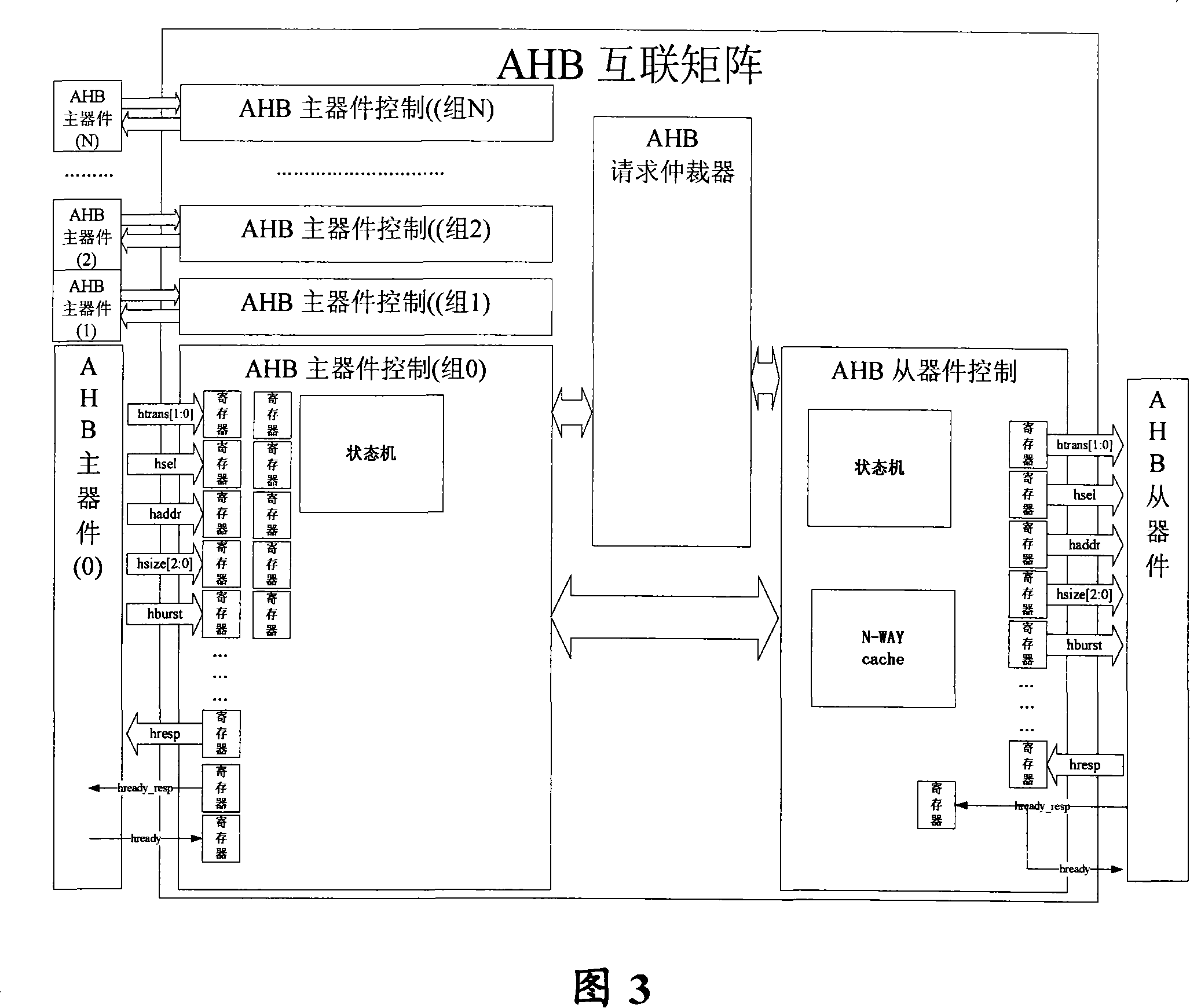

[0022] The AHB bus is a high-speed bus used by many embedded processor (especially ARM CPU) systems for data transmission. This interface design uses multiple AHB master devices to reach the AHB through a streamlined matrix with a cache. From the device side, high-speed, high-efficiency, parallel operation between buses is realized.

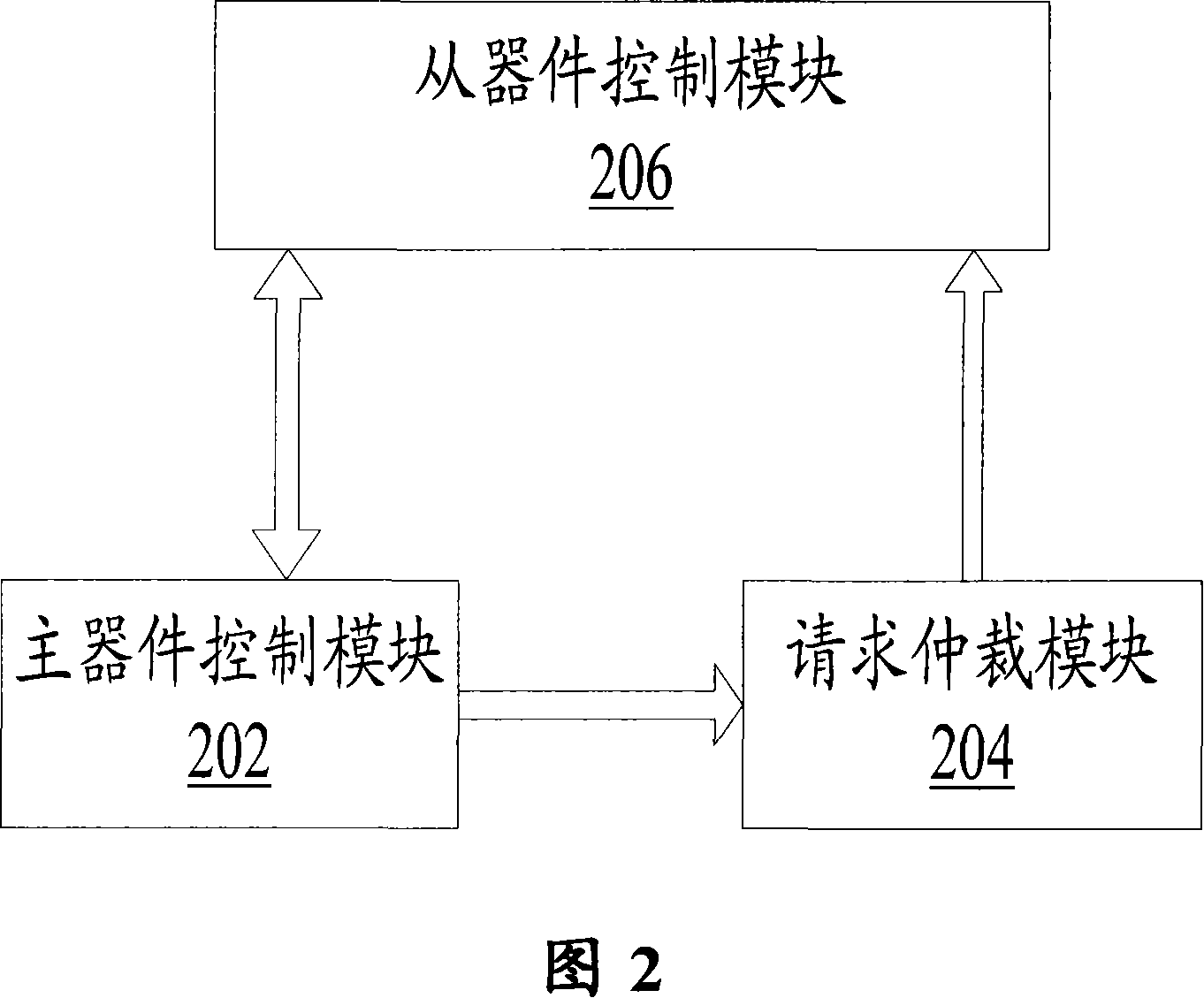

[0023] Aiming at the memory system, the present invention adds an N-way cache to this type of AHB matrix under the condition that the consistency of data is guaranteed at each interface, so that the efficiency of the AHB interface can be greatly improved. Such a matrix may be used as a cache memory for the operating system.

[0024] F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More