Processor

A processor and buffer technology, applied in the field of processors, can solve the problems of difficulty in fully storing and providing instructions, complicated switching of instruction buffer control, and shortening of time, so as to avoid waiting for access, low power consumption, and reduce frequency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0049] Hereinafter, Embodiment 1 according to the present invention will be described with reference to the drawings.

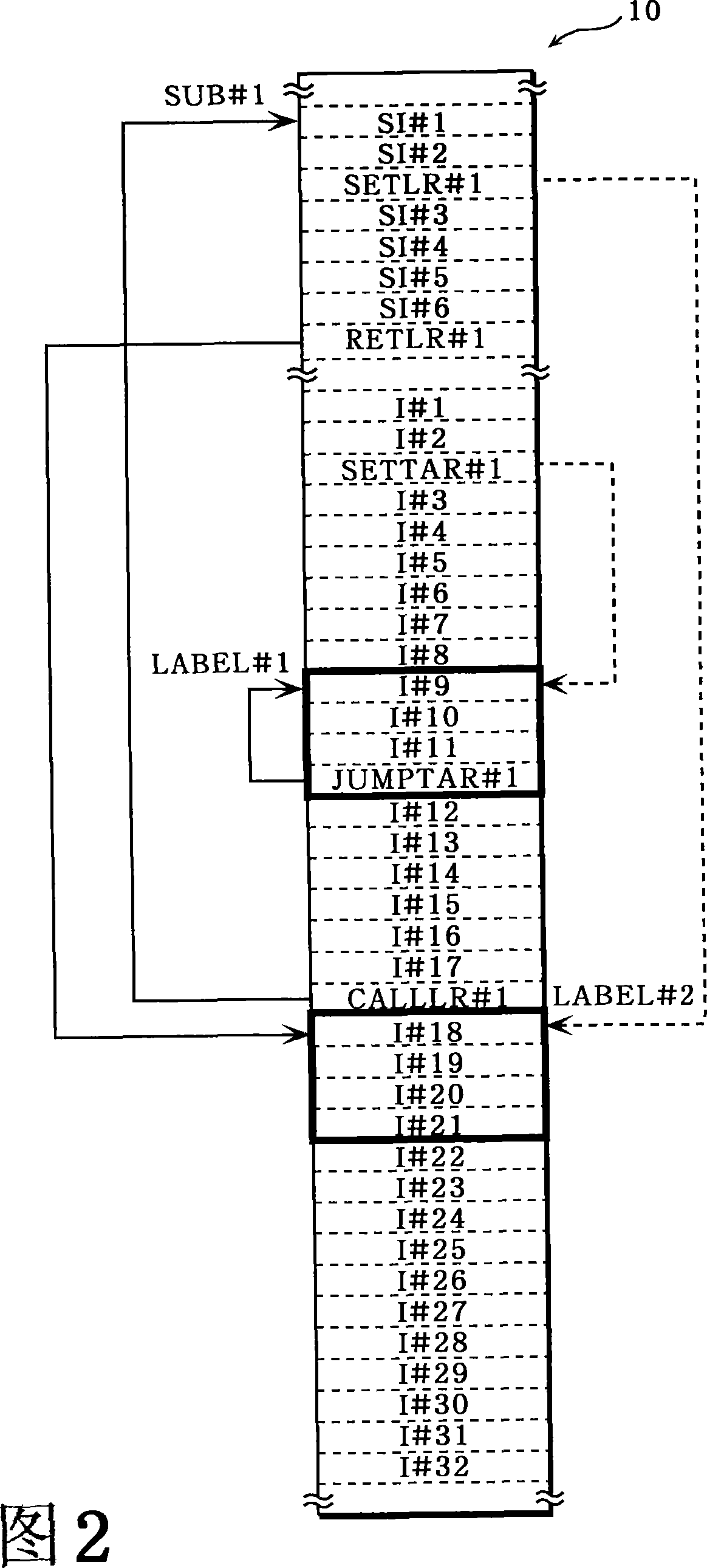

[0050] The processor of this embodiment is characterized in that, in addition to the instruction buffer for storing general instructions, it also includes an instruction buffer for storing the instructions of the loop part. The instruction buffer provides instructions instead of repeatedly fetching them from the instruction cache.

[0051] Further, this feature is that, in addition to including these instruction buffers, it also includes an instruction buffer for storing the instructions of the return part of the subroutine. The buffer provides instructions.

[0052] The processor of this embodiment is explained based on the above.

[0053] First, the configuration of the processor of this embodiment will be described.

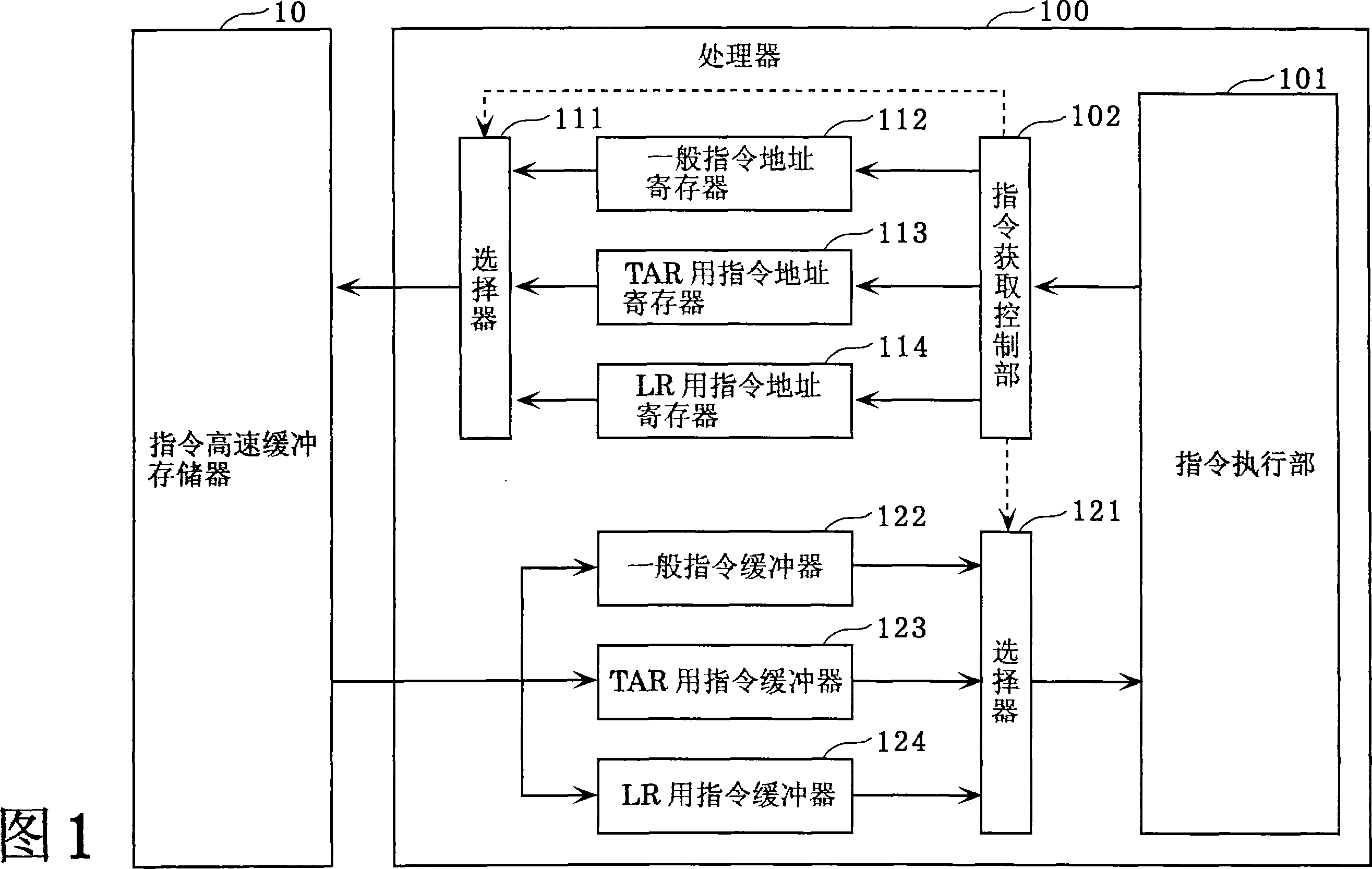

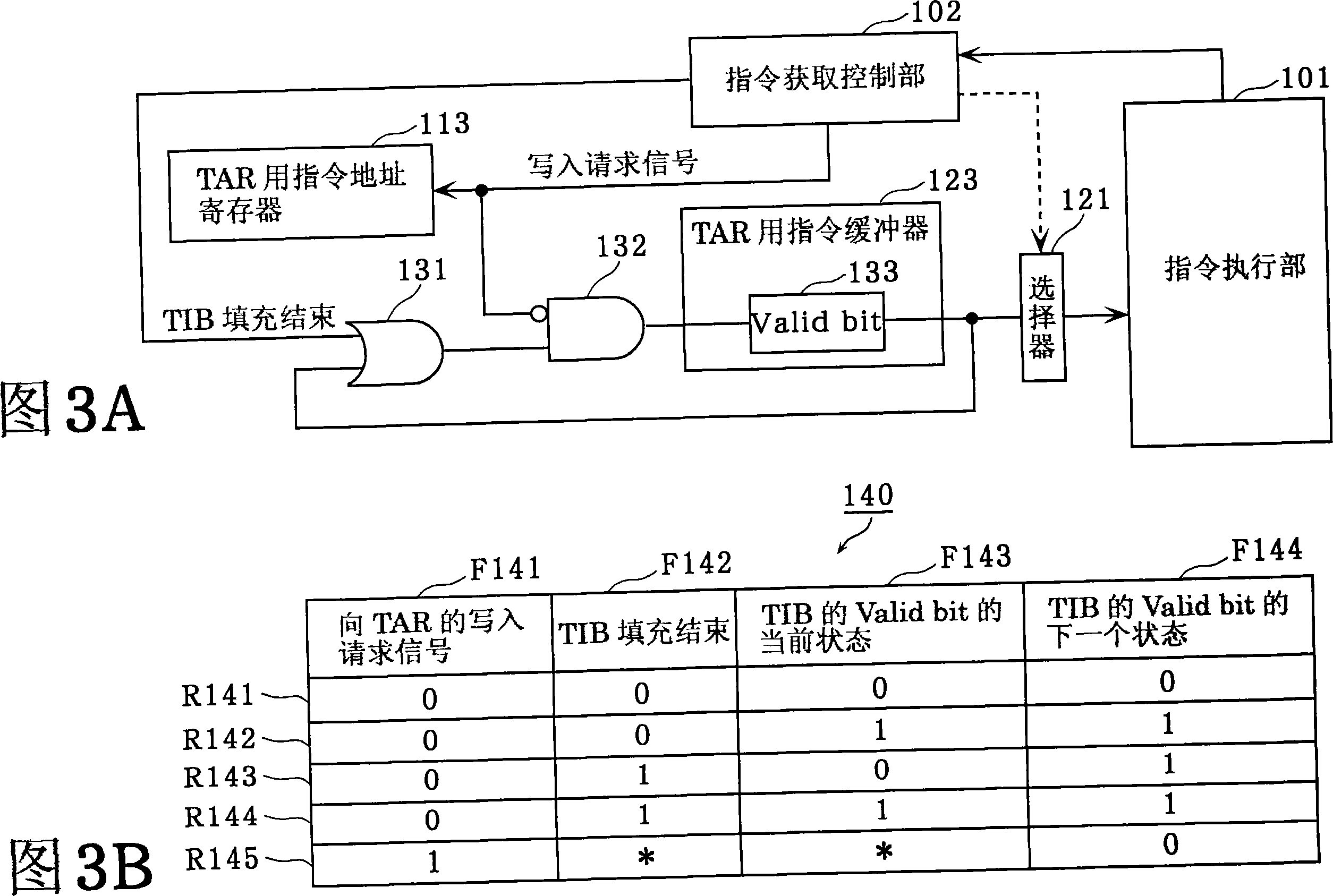

[0054] As shown in FIG. 1 , the processor 100 includes, in addition to a general instruction buffer 122 storing general instructions, an ...

Embodiment 2

[0129] Next, Embodiment 2 according to the present invention will be described with reference to the drawings.

[0130] The processor of this embodiment is characterized in that it includes a plurality of instruction buffers for storing instructions of loop parts, and provides a plurality of instructions of loop parts.

[0131] The processor of this embodiment is explained based on the above.

[0132] In addition, the same reference numerals are assigned to the same structural parts as those of the first embodiment, and description thereof will be omitted.

[0133] First, the structure of the processor of the embodiment will be described.

[0134] As shown in FIG. 10 , the differences between the processor 200 and the processor 100 are the following (1) to (7).

[0135] (1) The command acquisition control unit 202 is included instead of the command acquisition control unit 102 .

[0136] If the instruction execution unit 101 executes the first filling instruction for TAR, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More