Paralleling floating point multiplication addition unit

A floating-point multiply and add operation technology, applied in concurrent instruction execution, machine execution devices, instruments, etc., can solve problems such as reducing precision, reducing execution efficiency, and increasing hardware overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0188] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0189] The invention adopts three-stage assembly line to realize, realizes with VerilogHDL, and uses 0.18 micron standard cell library to carry out circuit synthesis after passing verification.

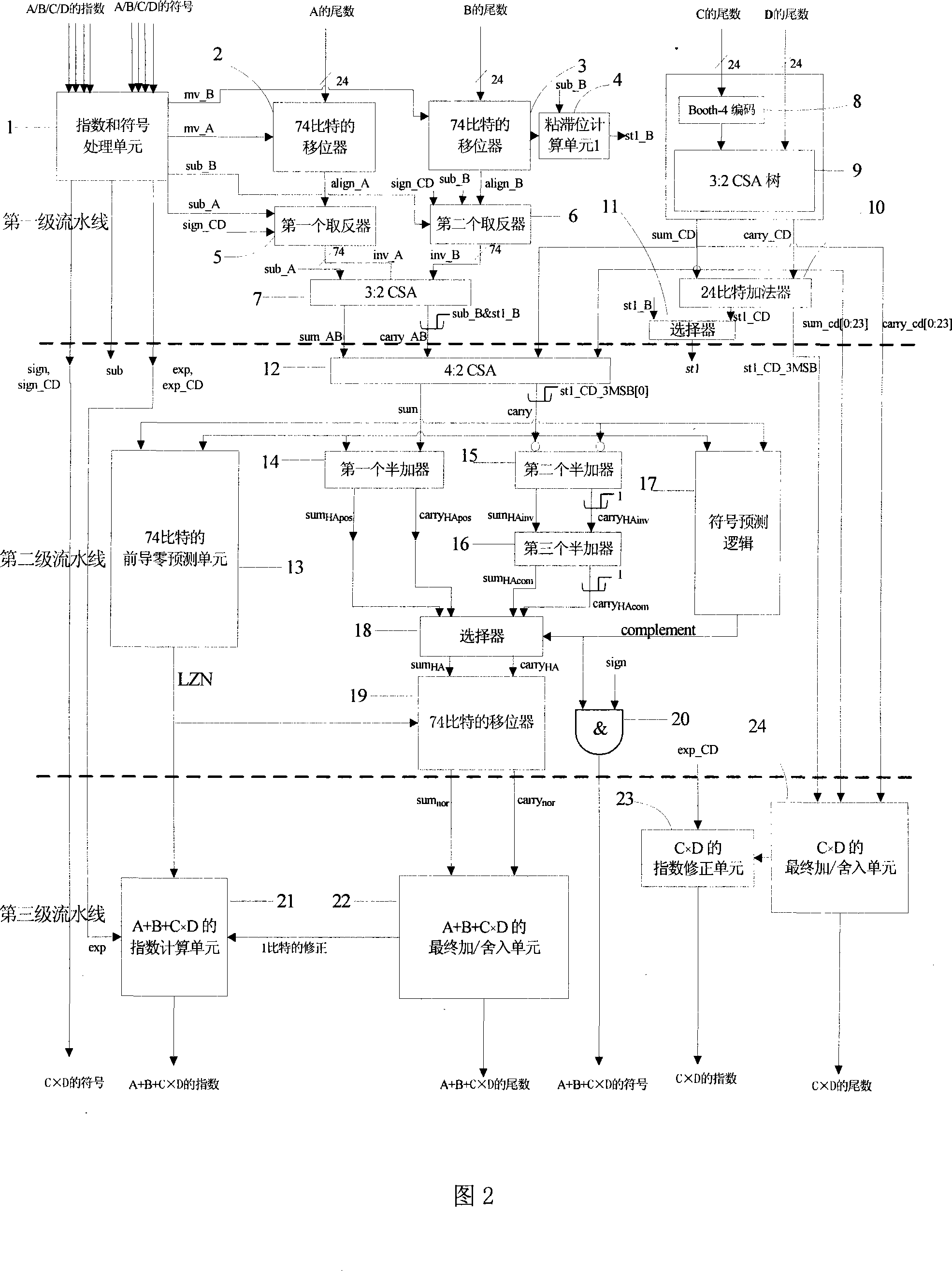

[0190] The single-precision parallel floating-point unit of the present invention is divided into three pipeline beats according to time sequence. The whole working process will be described below with reference to FIG. 2 . In this embodiment, A+B+C×D is still used to represent a parallel multiply-add operation. And here B is less than or equal to A, which is pre-processed by the compiler.

[0191] The first-stage pipeline: shift alignment of A and B, Persian encoding and partial product compression of C×D.

[0192] The base 4 Potts encoder 3 encodes the mantissa of C, and then multiplies the encoded result with the mantissa of D to obtain ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More