A Pipeline Tightly Coupled Accelerator Interface Structure Based on Instruction Expansion

A technology of instruction expansion and interface structure, applied in concurrent instruction execution, instruments, register devices, etc., can solve the problems of poor acceleration effect, difficult software development, poor real-time performance of hardware acceleration, etc., to reduce resource and power consumption overhead, The effect of achieving instruction-level parallelism and reducing performance impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

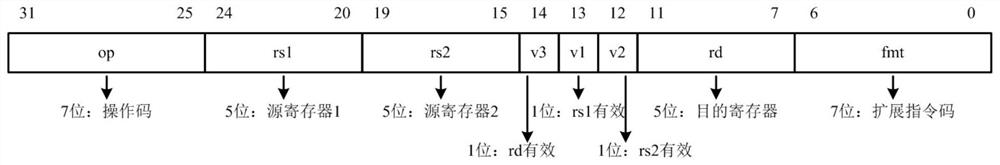

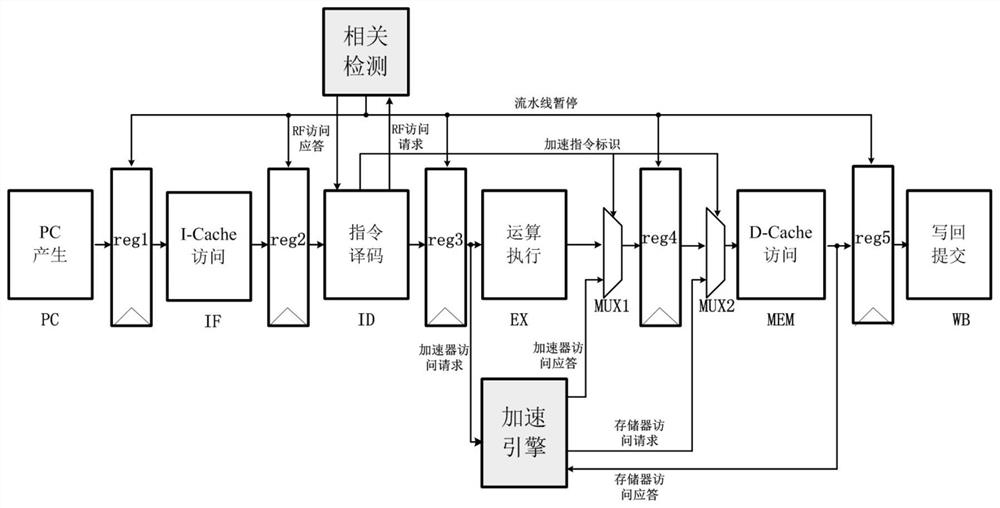

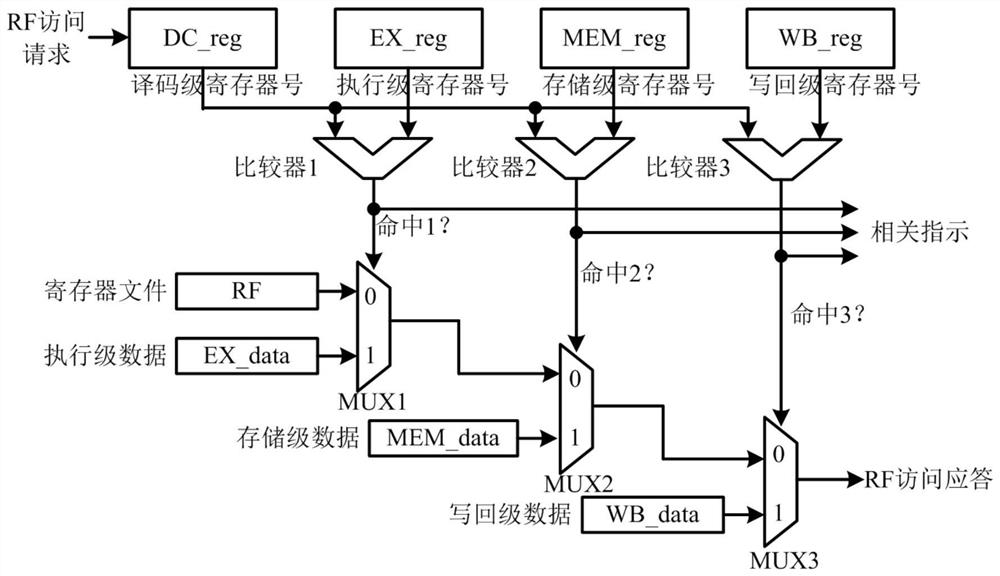

[0035] The present invention provides a pipeline tightly coupled accelerator interface structure based on instruction expansion, which fully taps the extensible ability of the current instruction set, and uses scalable instruction bit field coding to perform unified decoding, avoiding damage to the main Pipeline intrusion, and a "request-response"-based interactive protocol to complete the tight coupling with the main pipeline. At the same time, in order to reduce the impact of acceleration instructions on the performance of the main program, a non-blocking related processing mechanism is proposed, which can greatly improve the applicability of the accelerator interface. The accelerator interface design structure realized by this technology does not depend on a specific instruction set system and is not destructive to the original pipeline. It also has some advantages of instruction-level parallelism. This technology does not depend on a specific processor structure and bus p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More