Method for improving hardware acceleration performance of fire wall chip

A hardware acceleration and firewall technology, applied in the network field, can solve the problems of firewall performance degradation, failure to implement hardware, paralysis, etc., and achieve the effects of improving efficiency, reducing conflict probability, and shortening length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

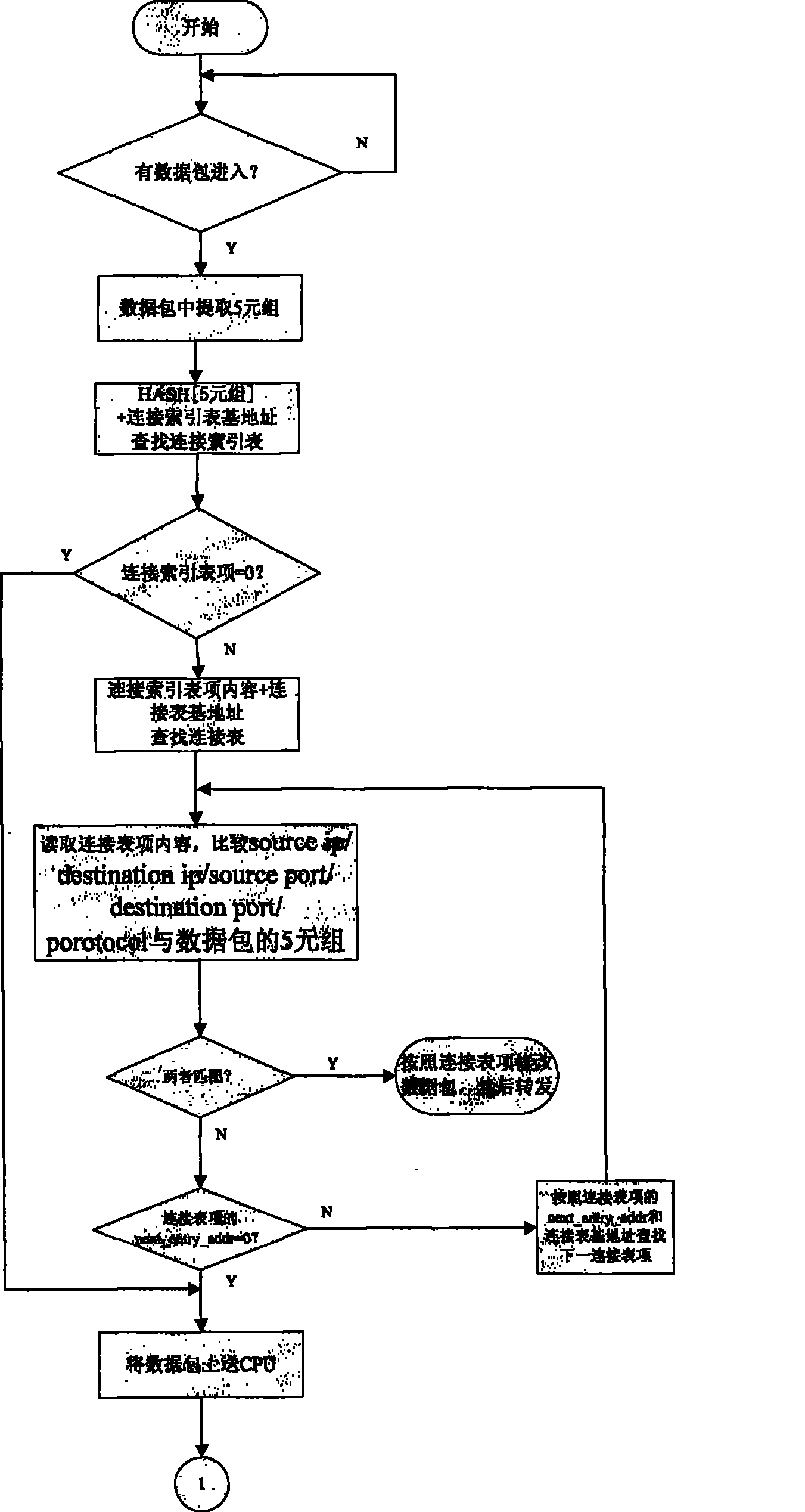

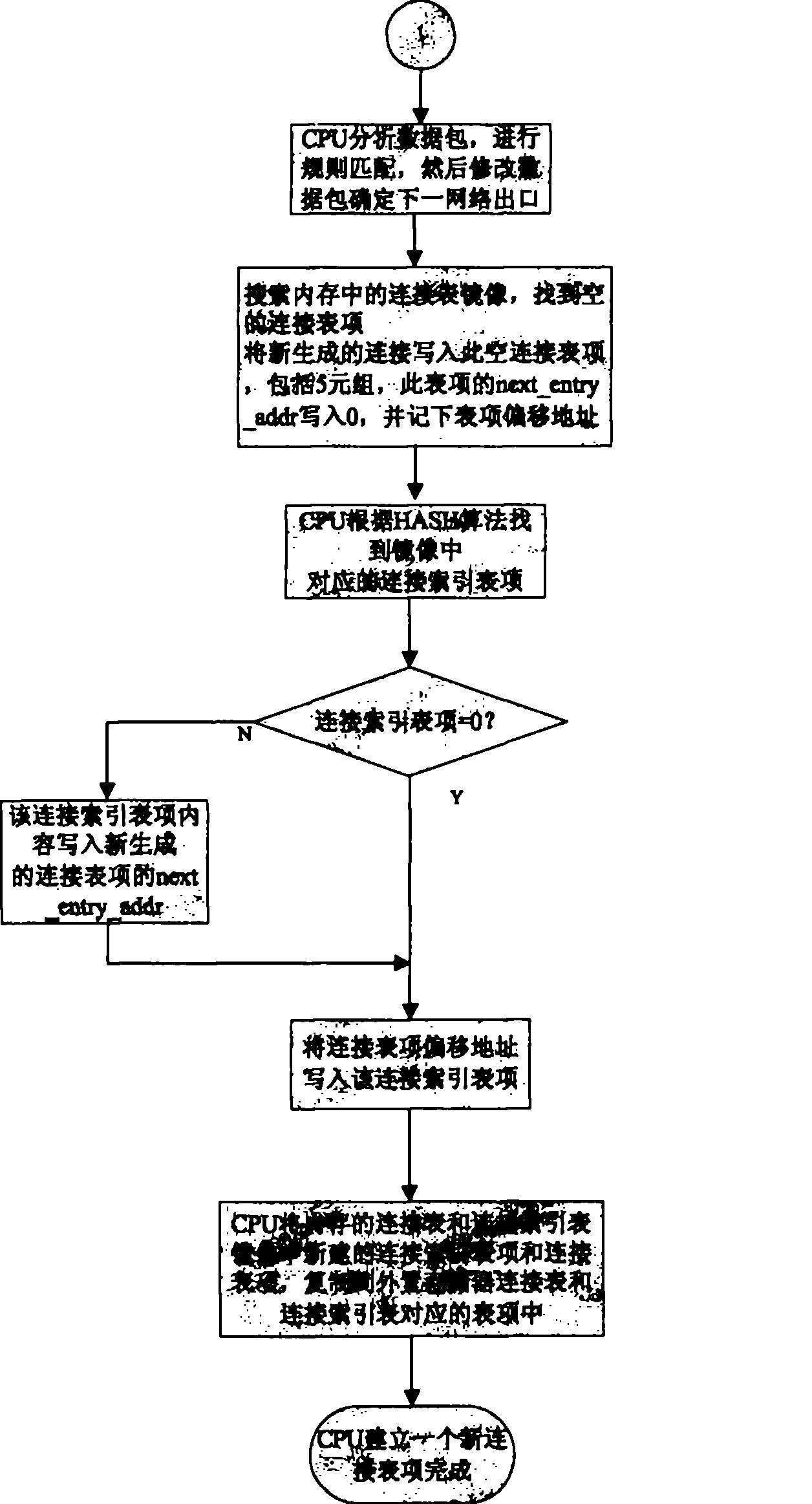

[0025] The method of the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

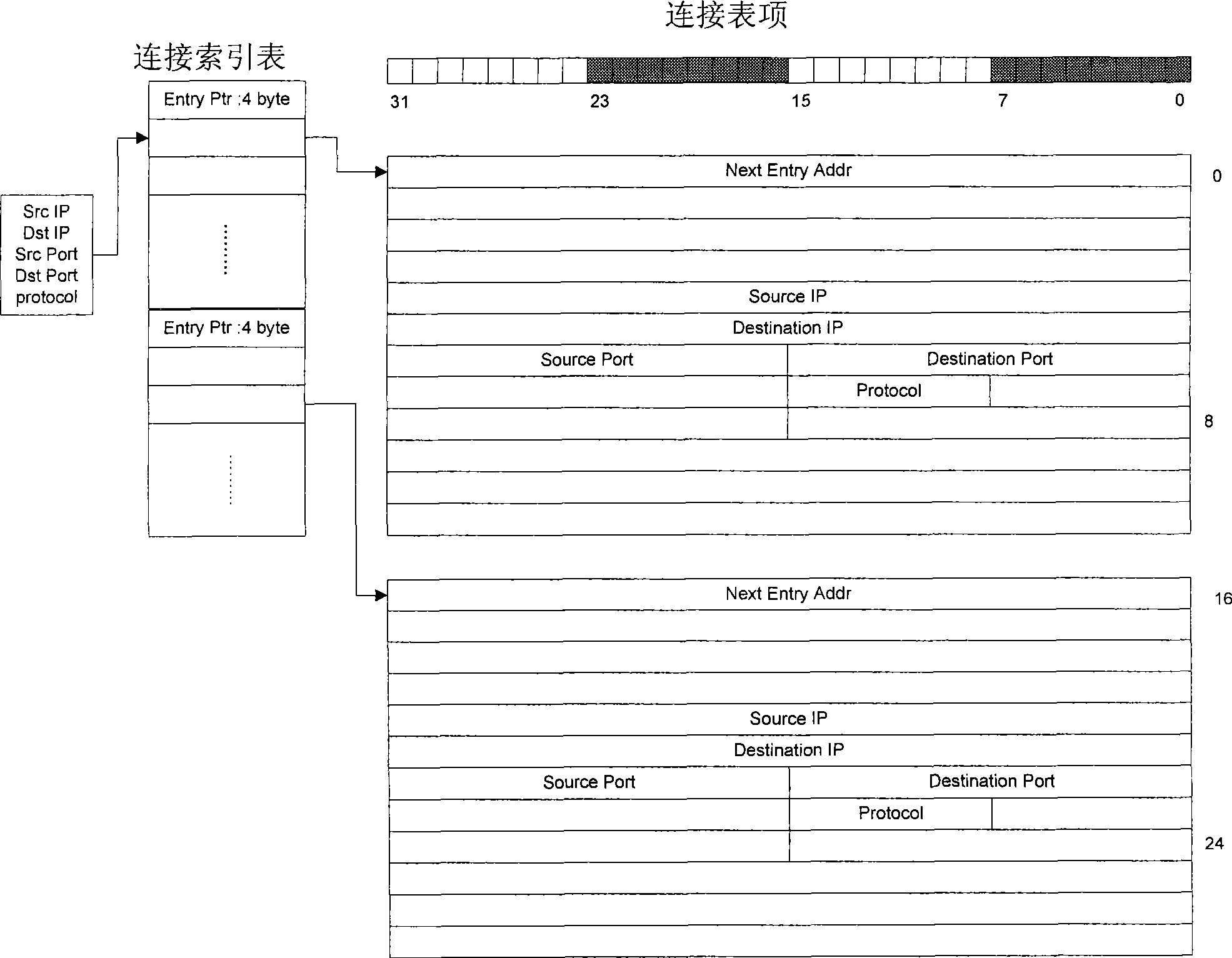

[0026] Firstly, the present invention configures an external memory outside the firewall chip, separates an area for the connection index table and the connection table in the memory, and stores the base addresses of the connection index table and the connection table in the firewall chip and the CPU. A connection index table and a mirror image of the connection table are established in the CPU memory, and the mirror image is kept in sync with the connection index table and the connection table in the external memory of the firewall chip.

[0027] The structure of the connection index table entry and the connection table entry is as follows figure 1 shown. Wherein, each connection index entry stores the offset address of the head of the connection table entry chain. The address of the index entry corresponds to the result of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com