Serial port caching control method, controller and microcontroller system thereof

A microcontroller and controller technology, applied in the direction of memory address/allocation/relocation, input/output to the record carrier, etc., can solve the problems affecting the execution efficiency of the microcontroller system, and achieve the effect of increasing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

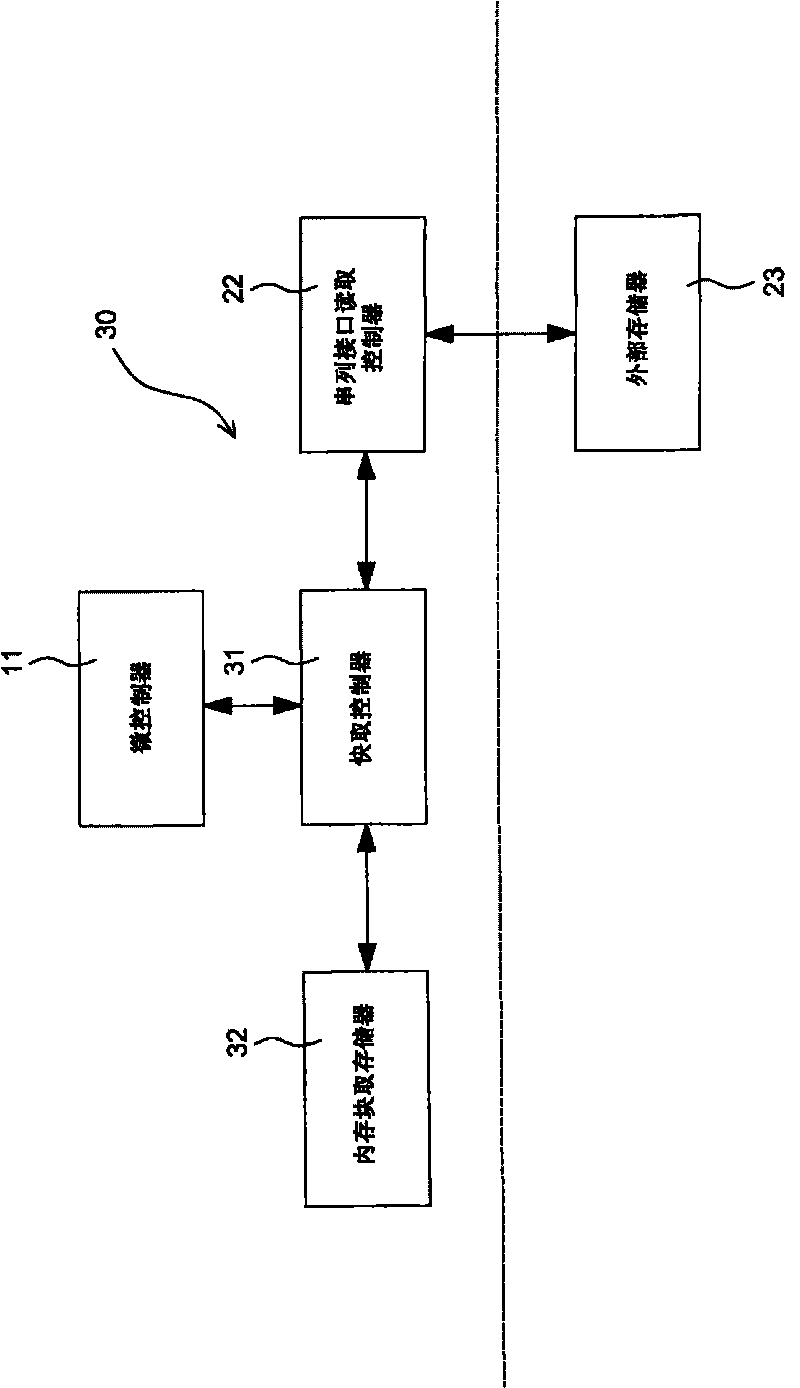

[0029] The serial interface cache controller, control method and microcontroller system using the controller of the present invention will be described in detail below with reference to the drawings.

[0030] For a general cache controller, its tag address column is only used to record the highest M-bit address, for example, an 8-bit address. Therefore, the amount of data corresponding to each tag address column is 256 bits. If the value of M is increased, although the amount of data corresponding to each tag address row will decrease, correspondingly, the tag address row must be increased so that the stored cache data amount remains the same. The higher the number of tag address columns, the higher the complexity and cost of the cache controller. For example, if the value of M is 8, and the cache controller has 8 tag address columns, an internal cache memory of 2048 bytes is required, and the amount of data downloaded from the external memory each time is 256 bytes. If the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More