Semiconductor Device Leadless Package Structure

A packaging structure, leadless technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of increasing the package size, increasing equipment cost, sensitivity, etc., to reduce the package size, reduce Distance, the effect of reducing product cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

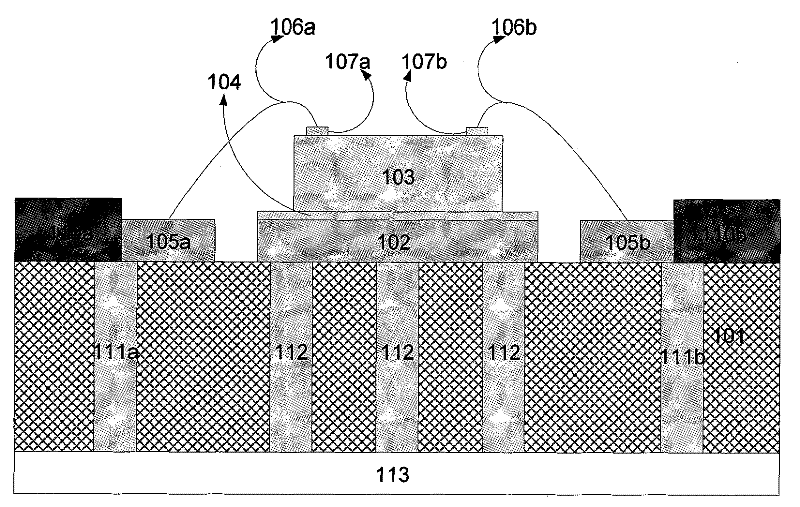

[0017] The invention discloses a leadless packaging structure of a semiconductor device, such as figure 2 and image 3 As shown, it includes substrates 201, 301 and circuit dies 203, 303. The substrates 201, 301 at least include the upper top layer metal, the middle dielectric layer and the lower bottom metal 213, the bottom metal 213 is ground, and the The top layer metal includes circuit die sticking areas 202, 302, the circuit die sticking areas 202, 302 and the circuit dies 203, 303 are bonded together by an adhesive 204, and the circuit die sticking areas A raised first solder resist layer 209a, 209b, 309a, 309b is provided above the edge 214a, 214b, and the top layer metal is provided outside the circuit die attaching area 202, 302 with the circuit die attaching area 202, 302 Electrically connected substrate ground bonding areas 205a, 205b, 305a, 305b, the second solder resist layer 211a, 211b is arranged outside the substrate ground bonding areas 205a, 205b, 305a, 305...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More