Equivalence verification method for eliminating misjudgment by combining constraint satisfaction

A technology of equivalence verification and constraint satisfaction, applied in the field of effective misjudgment elimination and cost-effectiveness verification, it can solve the problems of integrated circuit chip design scale growth and complex functions, so as to speed up time-to-market, improve success rate, and eliminate errors. the effect of judgment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] Below by specific embodiment and accompanying drawing, the present invention is described in further detail:

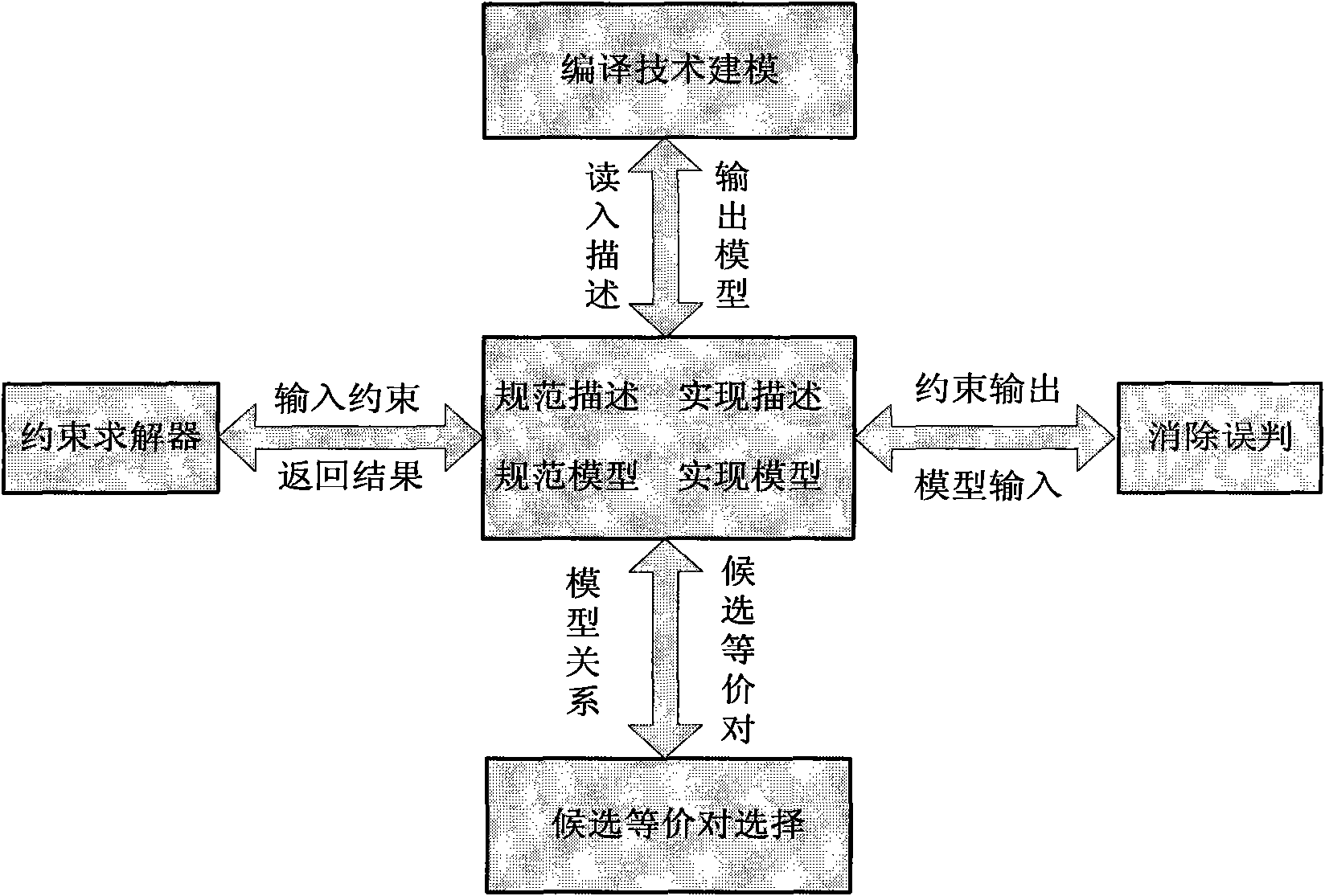

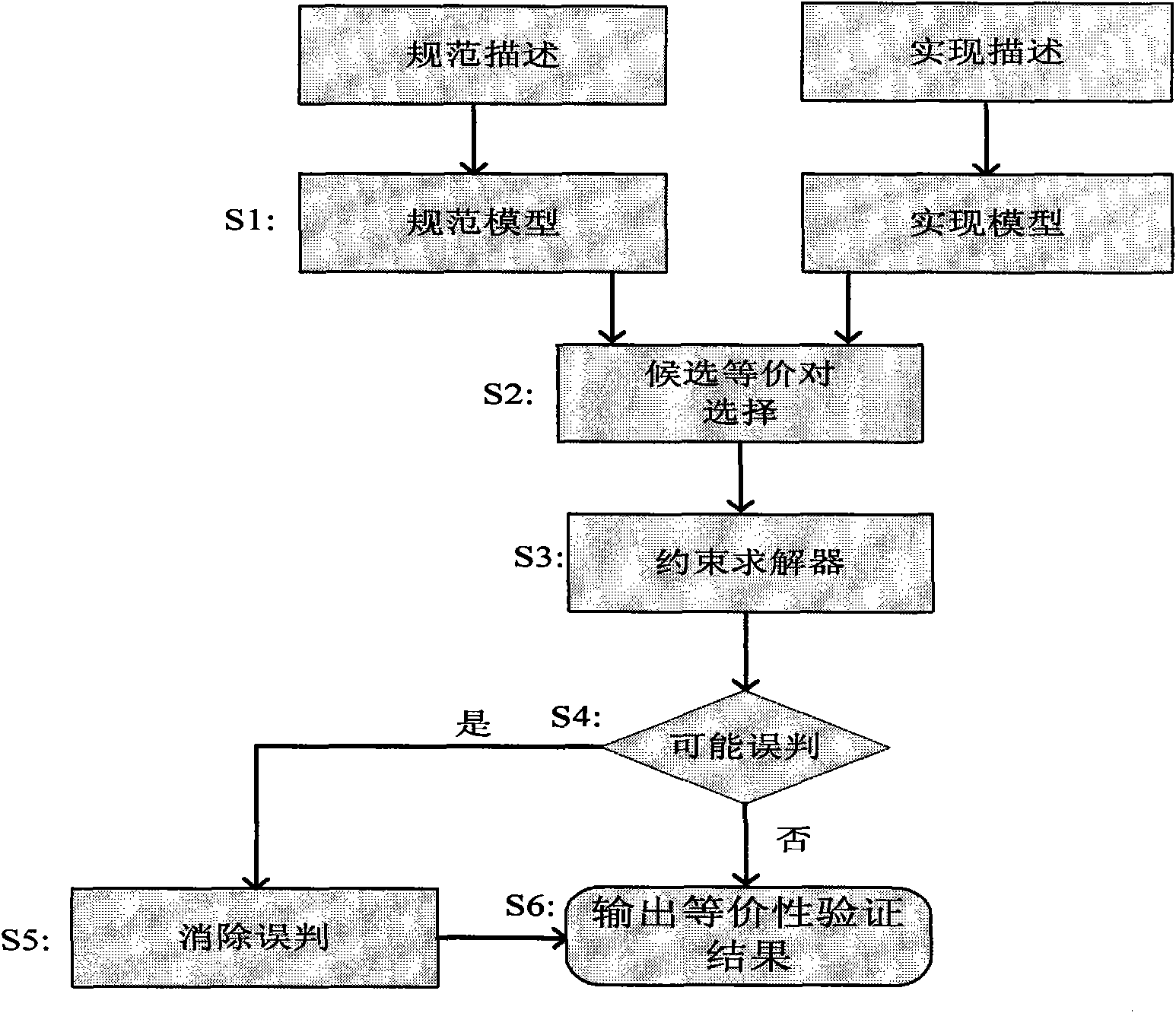

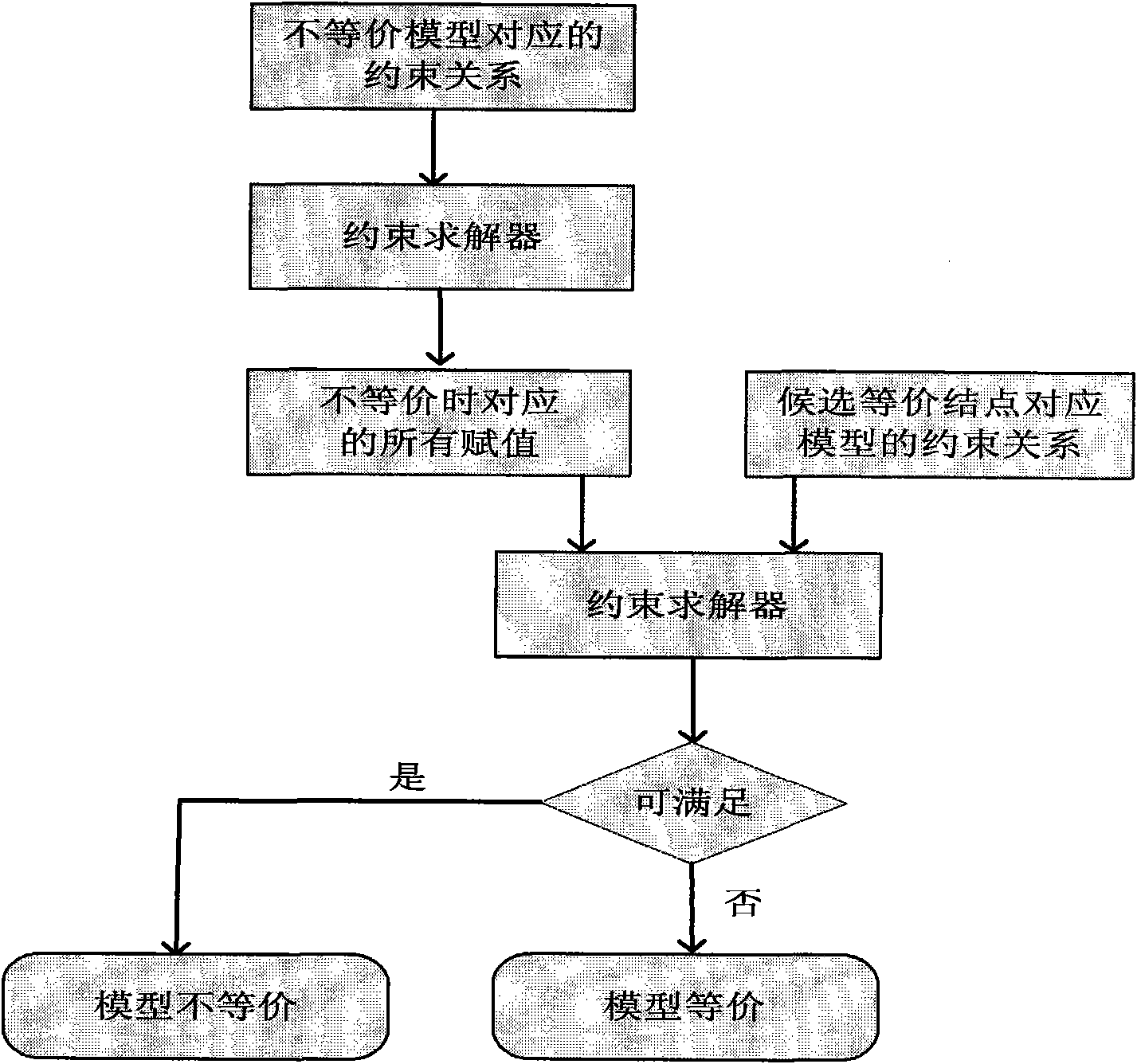

[0037] see figure 1 and figure 2 , an equivalence verification method that combines constraint satisfaction and eliminates misjudgments, and its steps include at least:

[0038] Step 1: Establish a model for specification description and implementation description;

[0039] Step 2: Select the appropriate candidate equivalence pair positions in the specification model and the implementation model to facilitate the equivalence verification based on the cut set method;

[0040] Step 3: quickly solve the candidate equivalence pairs using a constraint solver;

[0041] Step 4: Judging whether there is a misjudgment: If the specification model and the implementation model are equivalent, the verification result is equivalent, and there is no misjudgment, go to step 6; if the specification model and the implementation model are not equivalent, but this time is not ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap