LDPC (low-density parity-check) decoding method

A decoding and square matrix technology, applied in the field of decoding, can solve the problems of single parallel mode and large consumption of FPGA resources, and achieve the effects of low power consumption, reduction of parallel scale, and reduction of the number of memories

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

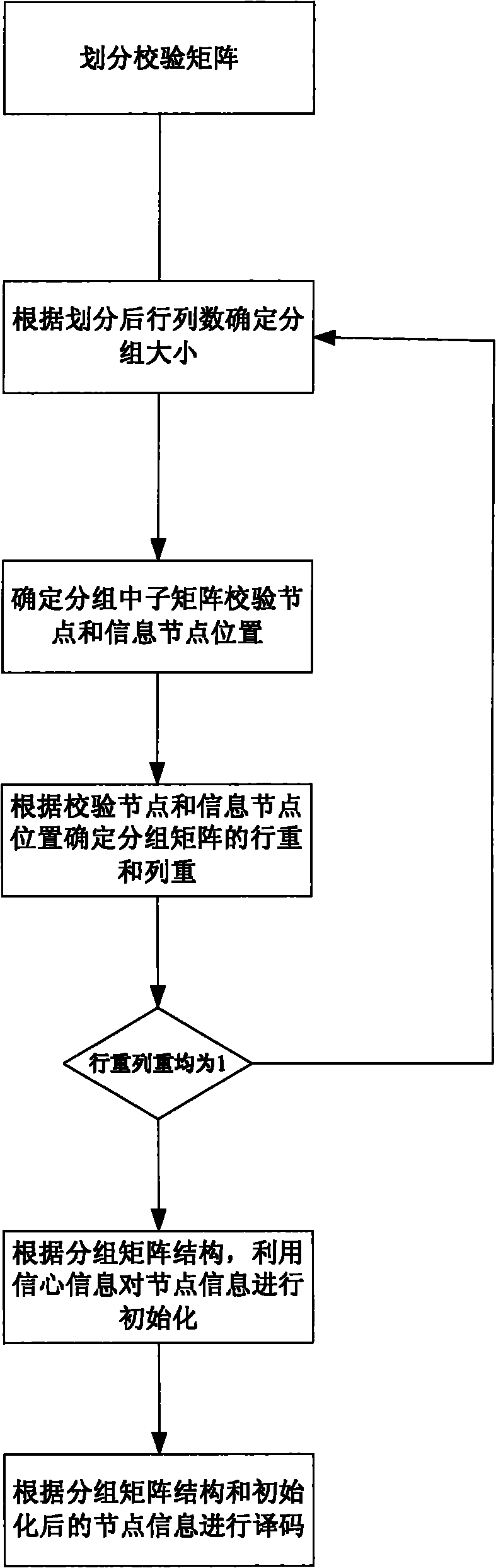

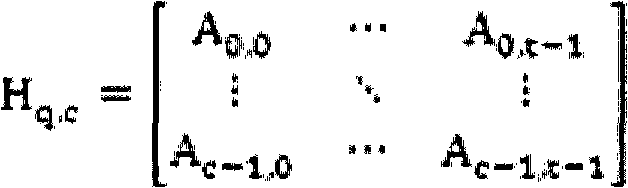

[0019] The following provides specific implementation methods for the LDPC code with a code rate of 0.4 in the national standard DMB-TH standard. Sub-matrix A for parity check matrix H of 0.4 code rate LDPC code in the national standard DMB-TH standard i,j expressed as H q,c The form is shown in formula (1):

[0020]

[0021] where A i,j It is a matrix of 127×127, which is a cyclic matrix or a matrix of all 0s with a row weight of 1. Other relevant parameters of the H matrix are: c=35, t=59, namely the matrix H q,c It is 35 rows and 59 columns; the size of the entire H is 4445 rows and 7493 columns; the row weight is 7 and 8, and the column weight is 3, 4 and 11. The total number of 1's in the H matrix is 275×127.

[0022] The following sub-matrix A is represented by the position of 1 in the first row of each non-zero cyclic sub-matrix i,j , the entire parity check matrix H q,c It can be expressed in the form shown in Table 1:

[0023] Table 1 check matrix H q,c ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More