Hardware coding method and circuit based on FEC (forward error correction) in 10G EPON ONU (Ethernet passive optical network optical network unit)

A coding method and coding circuit technology are applied in the field of FEC hardware coding methods and circuits to achieve the effects of strong operability, simple and effective implementation method, and small circuit cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0052] The present invention provides a method and circuit based on FEC hardware encoding in 10G EPON ONU, which is used to realize FEC hardware encoding in the uplink direction in 10G EPON ONU. Hardware timing speed.

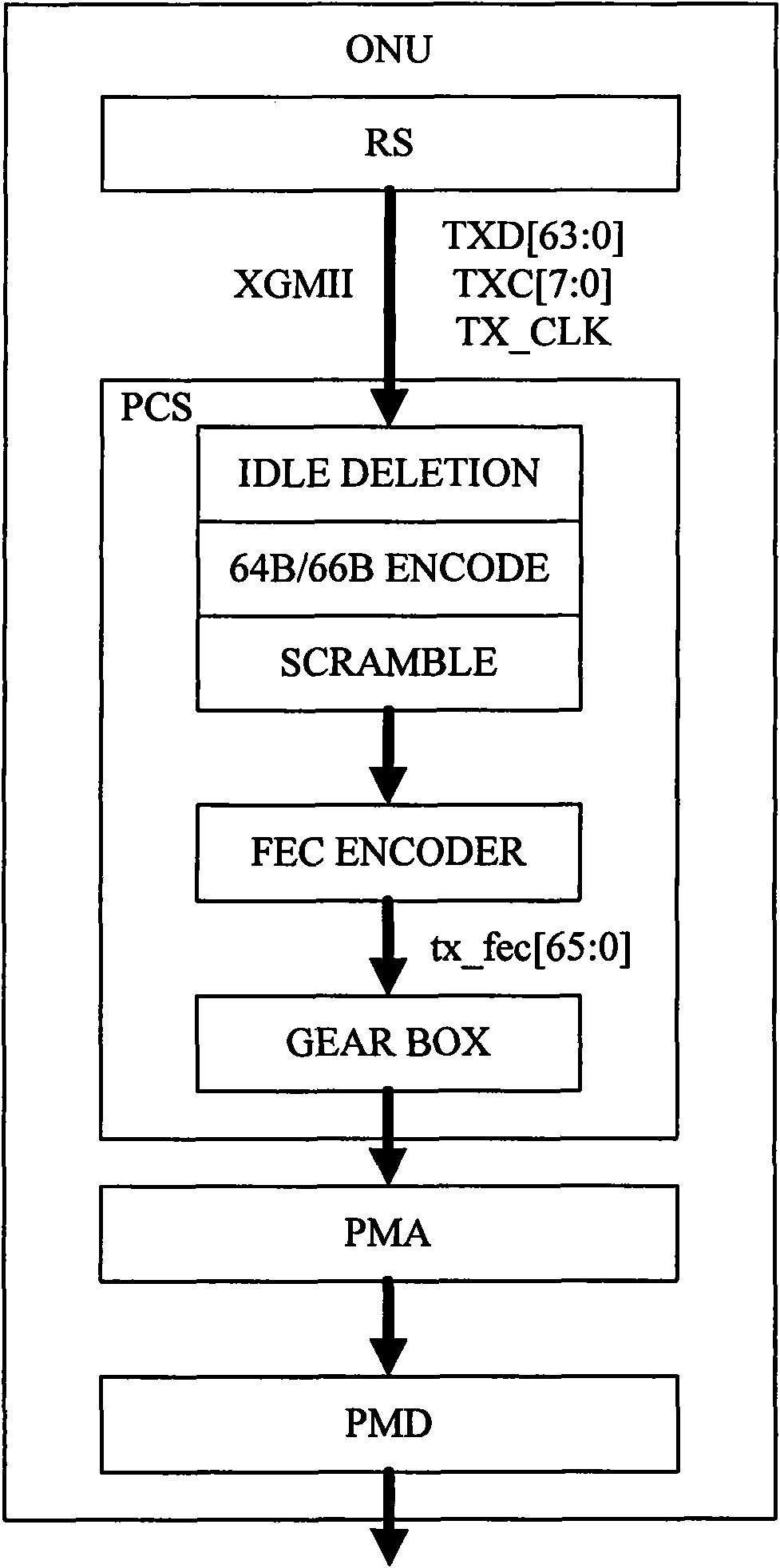

[0053] In order to better understand the present invention, the structure of the upstream direction of the 10G EPON ONU is first introduced below.

[0054] The structure of the 10G EPON ONU upstream direction specified in the IEEE802.3ay standard is as follows: figure 1 As shown, according to the transmission direction of the upstream data stream in the ONU (Optical Network Unit), the upstream processing process in the ONU is described as follows: the RS layer (coordination sublayer) transfers the data of the upper layer according to the XGMII interface (10Gigabit Media Independent Interface, 10Gb is independent of the media After the format...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More