Chip-on-board package structure and method for manufacturing the same

A technology of packaging structure and carrier board, which is applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of plastic overflow, poor light extraction rate, complicated manufacturing process, etc., to avoid colloid overflowing the packaging area, reduce the internal resistance of the chip carrier board, The effect of avoiding colloid waste

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] In order to fully understand the purpose, features and effects of the present invention, the present invention will be described in detail through the following specific embodiments and accompanying drawings, as follows:

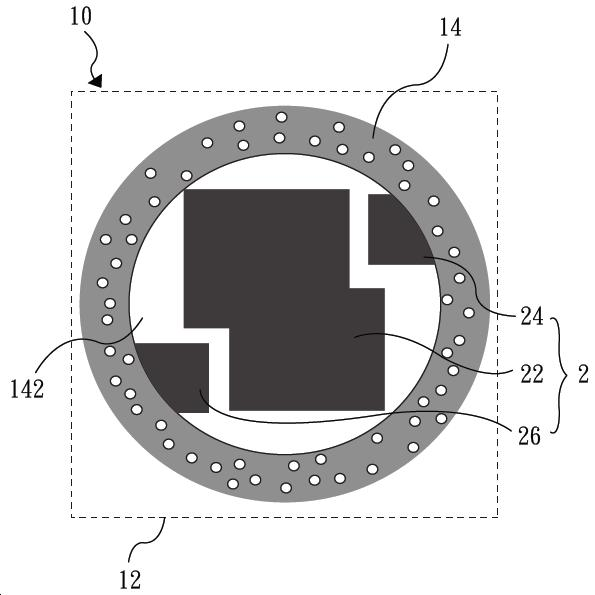

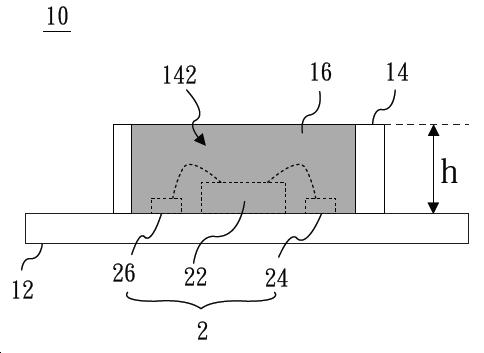

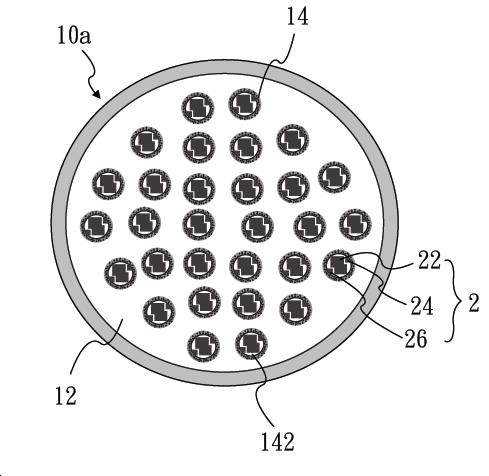

[0014] Please also refer to figure 1 and figure 2 . in, figure 1 It is a structural schematic diagram of a chip carrier packaging structure according to an embodiment of the present invention; figure 2 is used to illustrate the figure 1 The cross-sectional schematic diagram of the chip carrier package structure. In the figure, the chip carrier package structure 10 is used to package a light emitting diode 2 . Wherein, the LED 2 includes a bare chip 22 and two electrodes 24 , 26 . The chip carrier packaging structure 10 includes a substrate 12 , a sealing wall 14 and a sealing layer 16 . Wherein, the substrate 12 may further include at least one conductive layer (not shown in the figure) and an insulating layer (not shown in the figure), and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More