Method for testing high-voltage MOS device

A technology of MOS devices and testing methods, which is applied in the direction of single semiconductor device testing, semiconductor/solid-state device testing/measurement, etc., can solve problems such as inaccurate source-drain current testing, and achieve the effect of avoiding too small source-drain current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

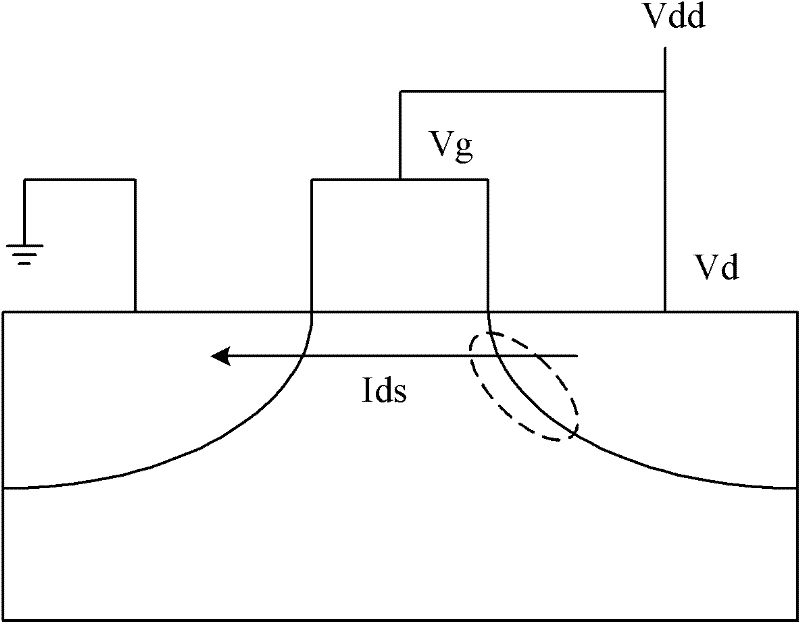

[0024] As can be seen from the background technology section, the existing high-voltage MOS device testing method applies a fixed test voltage to the gate and source to test the source-drain current flowing through, which is likely to affect the parasitic effect of the MOS device due to the parasitic effect caused by the high voltage. Electrical performance, resulting in inaccurate testing.

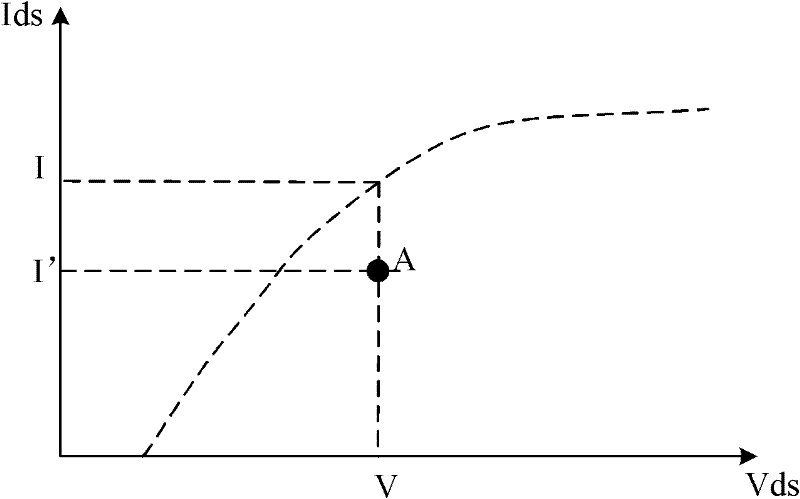

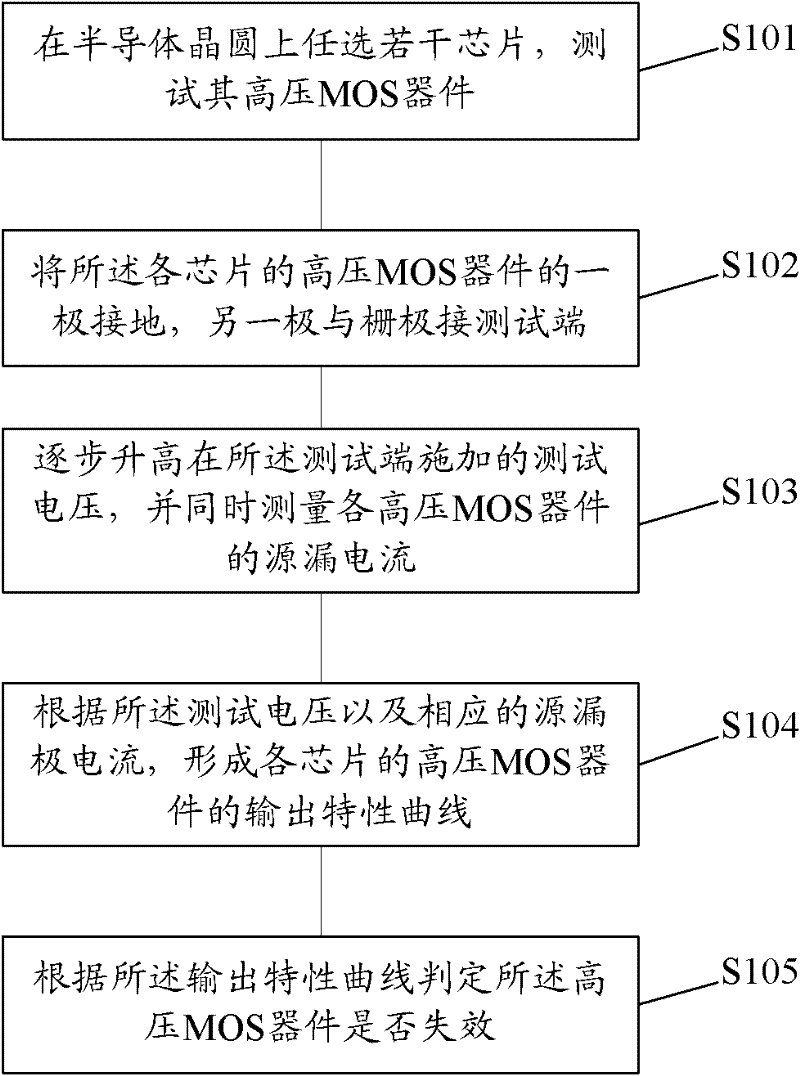

[0025] figure 2 The output characteristic curve of the transistor using the existing test method is shown. like figure 2 As shown, it is assumed that under normal circumstances, the output characteristic curve of the high-voltage MOS device should be a dotted line (because the gate is usually connected to the drain during testing, the high-voltage MOS device is not turned on at the beginning of the characteristic curve, and the source-drain current is 0). The critical voltage value of its saturation region is V, and the saturation current is I. And if the test voltage is suddenly ap...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More