Semiconductor device structure and method for manufacturing same

A device structure and semiconductor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of lateral and vertical diffusion semiconductor device electrical characteristics deterioration, etc., to improve the SCE effect, improve the overall electrical performance, The effect of saving manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

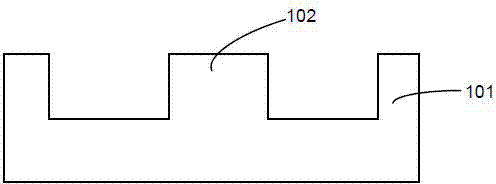

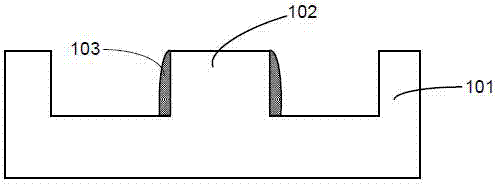

[0035] Below, will combine Figure 1A to Figure 1E , figure 2 as well as image 3 A method for fabricating a semiconductor device structure according to a first embodiment of the present invention will be described in detail.

[0036] Please refer to Figure 1A to Figure 1E , which shows schematic cross-sectional views of method steps for fabricating a semiconductor device structure according to a first embodiment of the present invention.

[0037] First, if Figure 1A As shown, a front-end device structure is provided, and the front-end device structure includes a semiconductor substrate 101 .

[0038] Wherein, the material constituting the semiconductor substrate 101 may be undoped single crystal silicon, single crystal silicon doped with impurities, or silicon-on-insulator (SOI) or the like. As an example, in this embodiment, the semiconductor substrate 101 is made of undoped single crystal silicon material.

[0039] Here, it should be noted that the structures of the ...

no. 2 example

[0069] Next, the first embodiment and Figure 4 to Figure 6 A method for fabricating a semiconductor device structure according to a second embodiment of the present invention will be described in detail. In the second embodiment, only the lateral diffusion barrier wall is formed to prevent the lateral diffusion of impurities in the S / D region, which is mainly based on the consideration of the complexity of the process. Other than that, other process steps and process parameters are the same as those of the first embodiment. Therefore, descriptions of these same process steps as well as process parameters and the like will be omitted.

[0070] Please refer to Figure 4 , which shows a flow chart of a method for fabricating a semiconductor device structure according to a second embodiment of the present invention, which is used to briefly show the flow of the entire method.

[0071] First, in step S401, a front-end device structure is provided, and the front-end device struc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More