Verification method and system for interface protocol compatibility of multi-interface protocol chip

A protocol chip and interface protocol technology, which is applied in the field of interface protocol verification of multi-interface protocol chips, can solve the problems of large hardware overhead, slow simulation speed, and verification of correctness, and achieve flexible verification methods, save hardware overhead, and improve Validate the effect of efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

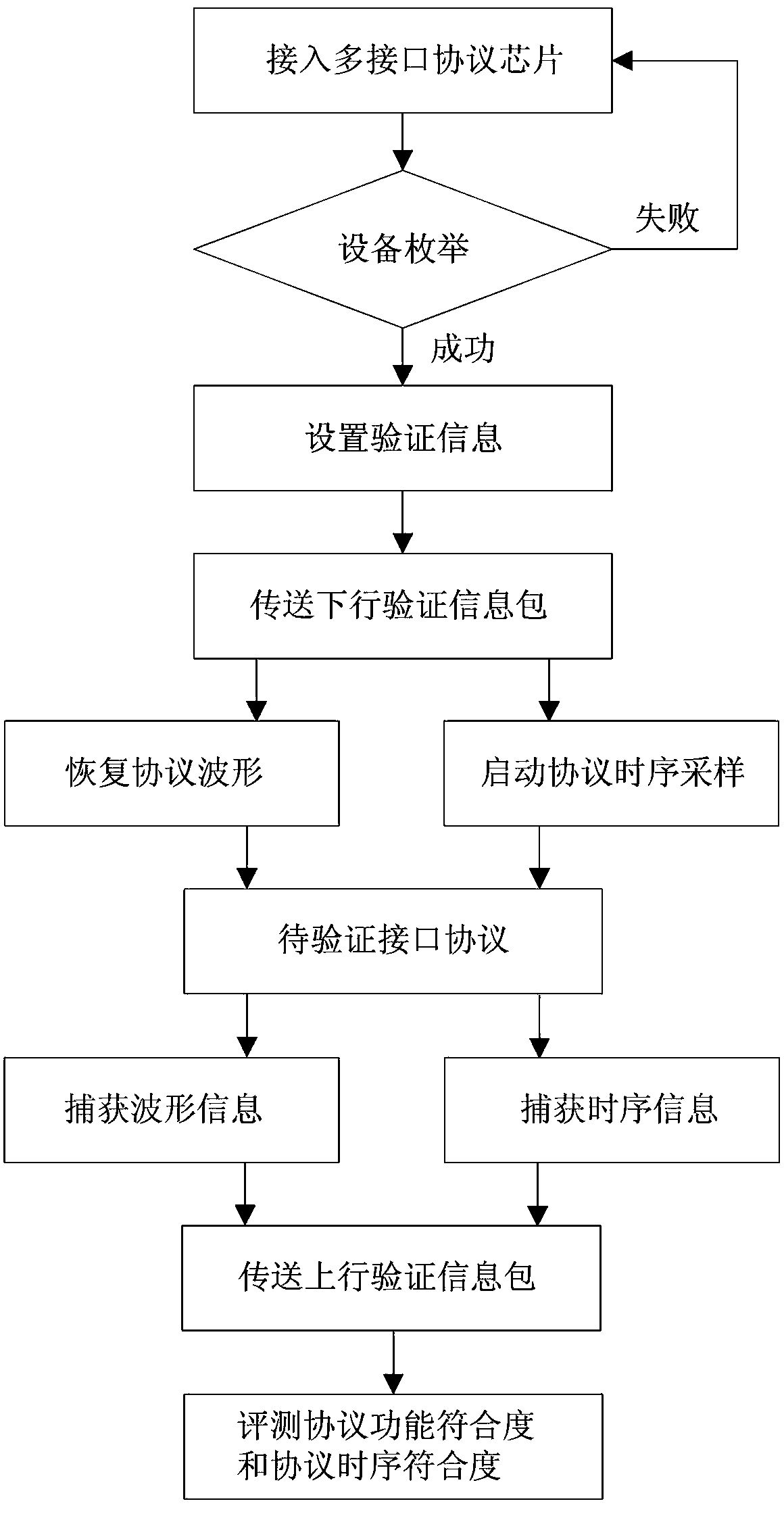

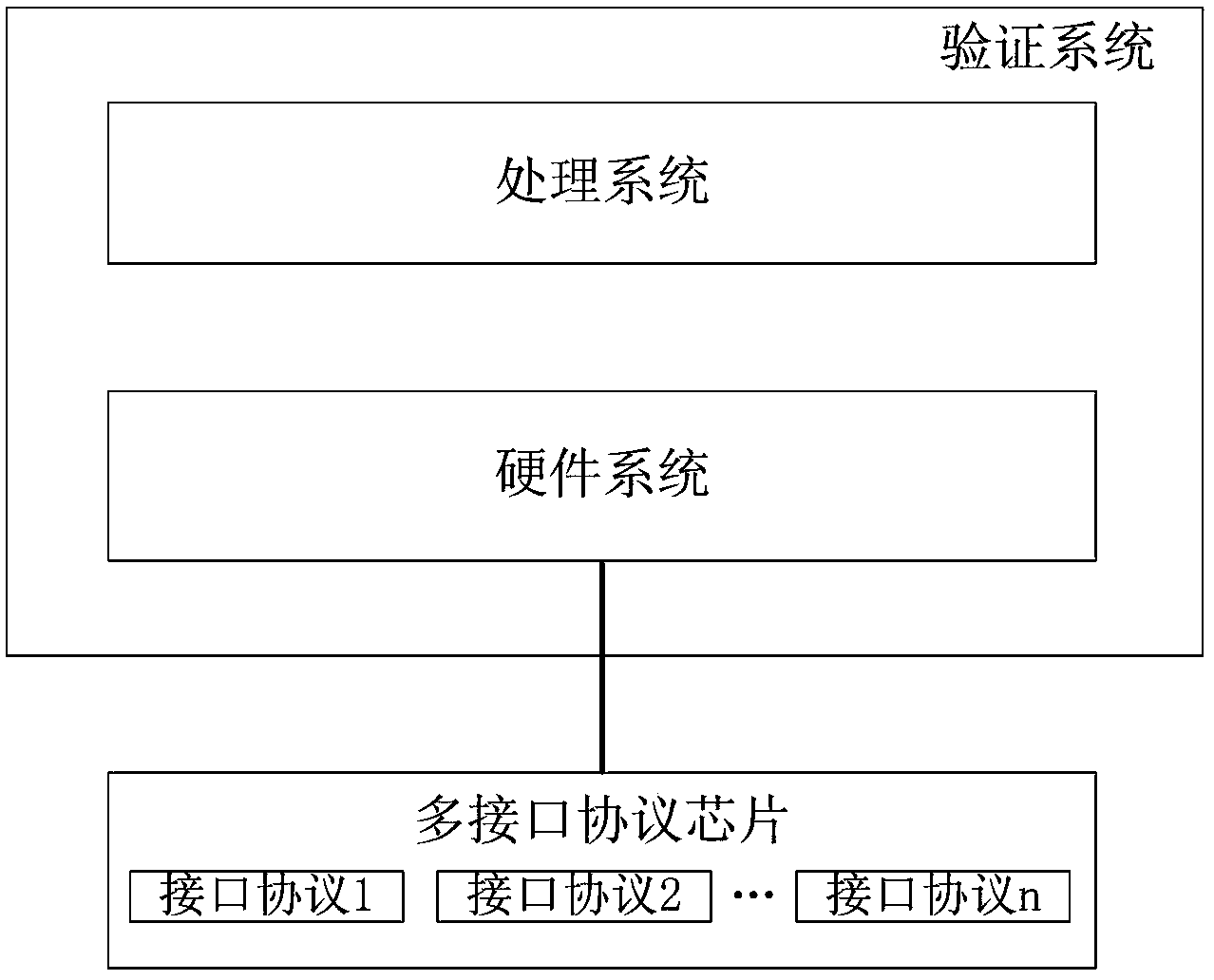

[0032] Such as figure 2 , image 3 , Figure 4 As shown, the interface protocol compatibility verification system of the multi-interface protocol chip of the present invention includes a processing system arranged in a computer and a hardware system for connecting the multi-interface protocol chip and the computer.

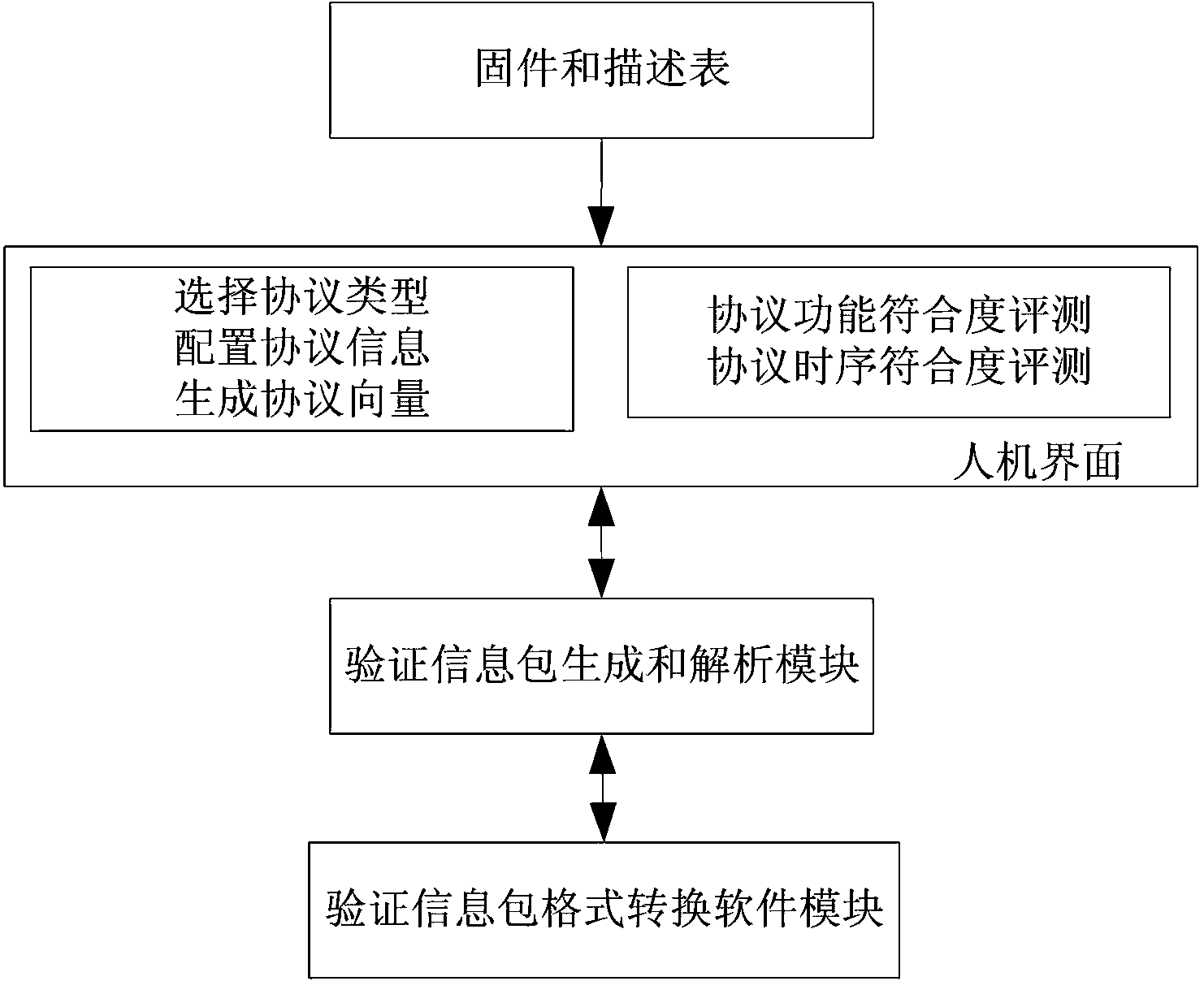

[0033] Such as image 3 As shown, the processing system includes sequentially connected: a description table and firmware, a man-machine interface, a verification information packet generation and analysis module, and a verification information packet format conversion software module.

[0034] The description table and firmware are integrated in the device driver file. The description table contains the characteristic description information of the hardware device, and the firmware covers the waveform description in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More