Method for packaging semiconductor

A packaging method and semiconductor technology, applied in radiation control devices, etc., can solve problems such as poor light reception and emission, and affect the overall performance of the chip, so as to achieve smooth reception and emission and improve the overall performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

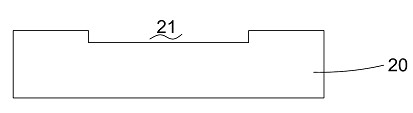

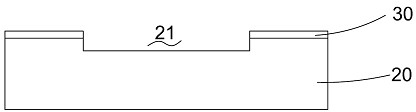

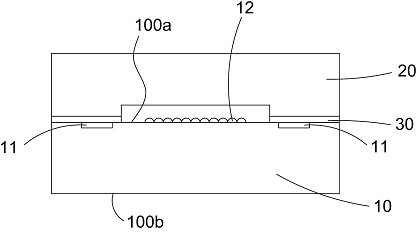

[0063] The present invention will be described in detail below in conjunction with specific embodiments shown in the accompanying drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

[0064] Furthermore, repeated reference numerals or designations may be used in different embodiments. These repetitions are only for the purpose of simply and clearly describing the present invention, and do not represent any relationship between the different embodiments and / or structures discussed.

[0065] In addition, the reference numerals related to the steps mentioned in the various embodiments of the present invention are only for the convenience of description, and there is no relationship of actual sequence. Different steps in each specific implementation manner can be combined in different se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More