Semiconductor substrate and manufacturing method thereof

A semiconductor and manufacturing method technology, applied in the field of semiconductor substrate manufacturing, can solve problems such as bottom silicon pollution, unavoidable energy loss, and damage to semiconductor device functions, so as to achieve good shielding effect and enhanced heat dissipation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

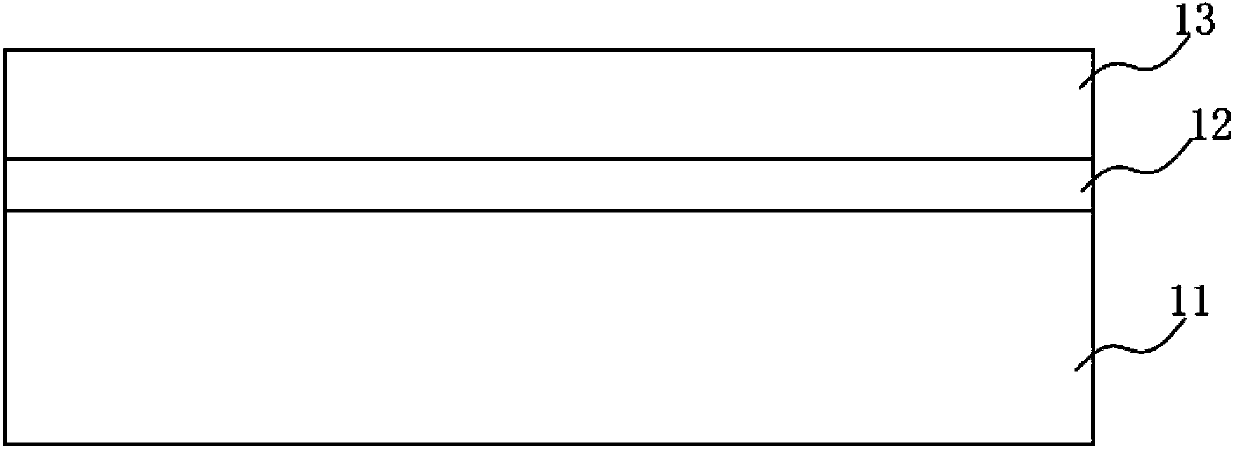

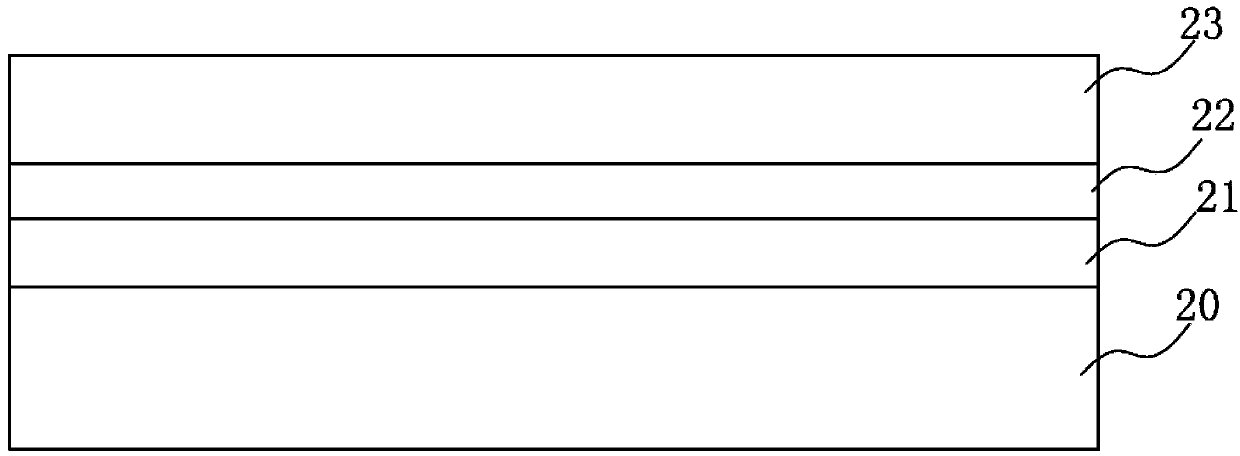

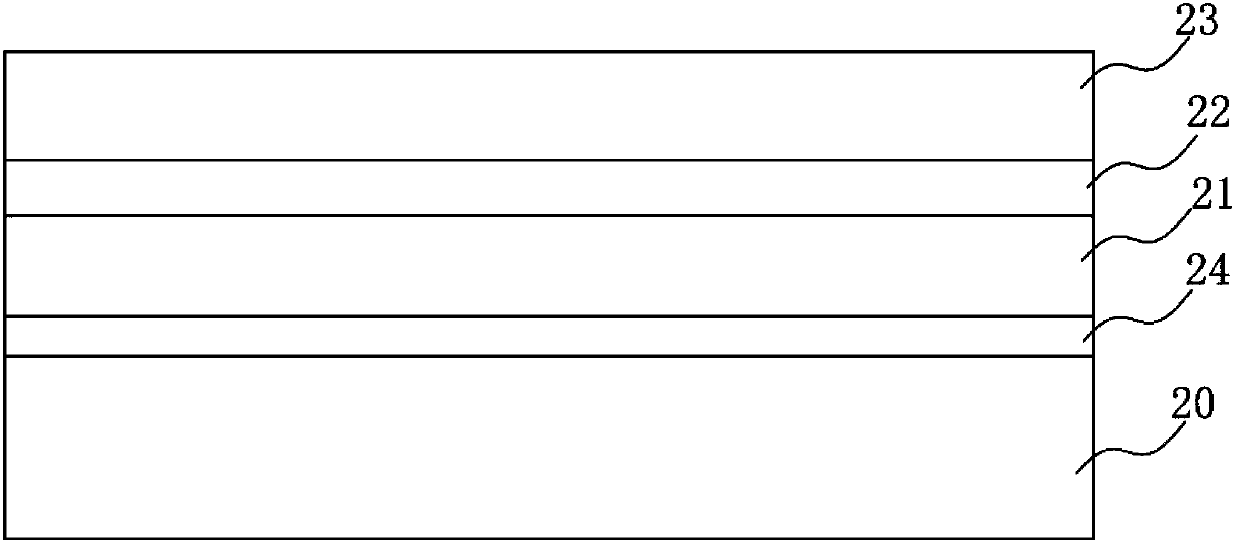

[0040] As mentioned in the background technology, in order to reduce the leakage loss caused by the bottom silicon when the existing silicon-on-insulator semiconductor substrate is used in some high-frequency devices, some high-resistivity single-crystal silicon supports are specially designed However, this not only increases the cost of SOI technology, but also does not really solve the problem. No matter how much the resistivity of single crystal silicon increases, there will always be problems of leakage current and power loss. In Soitec's technology, polysilicon is used as the shielding layer, although it can reduce the leakage current in the bottom silicon, but this method of improving the overall resistivity always faces the problems of impurity pollution and high temperature in processing engineering. In addition, in the existing semiconductor substrates, since the supporting substrate at the bottom is an insulating substrate, semiconductor devices fabricated on such sem...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap