Compiling method and device for memory

A memory and buffer technology, applied in the electronic field, can solve the problems of wasting verify and program time, and achieve the effects of improving efficiency, reducing time, and saving time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

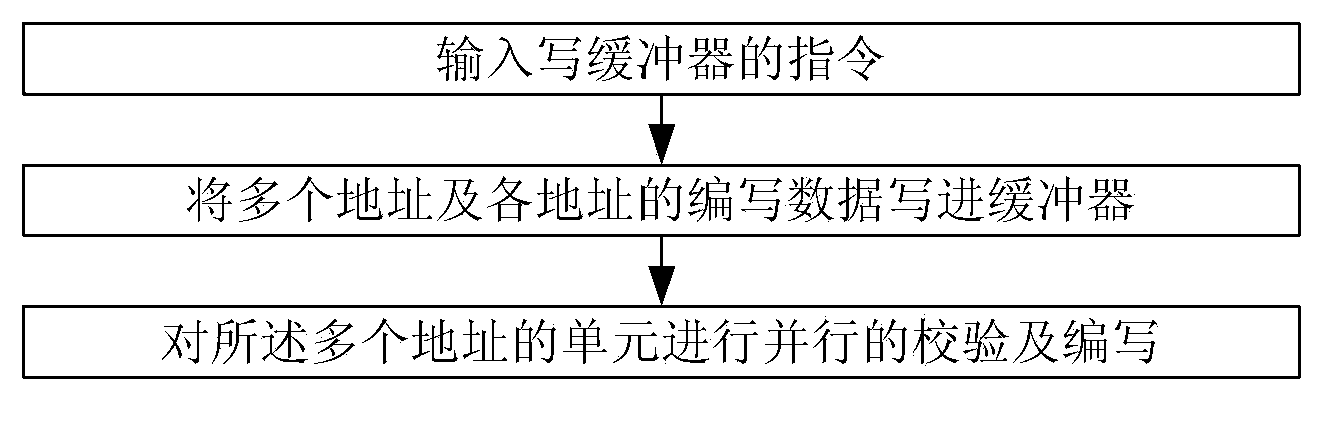

[0030] Embodiment 1, a method for writing a memory, such as figure 2 shown, including:

[0031] Input the command to write the buffer to clear the data in the buffer;

[0032] Write the addresses of N units in the memory and the programming data corresponding to each address into the buffer; wherein, N is a positive integer;

[0033] Perform verification and programming on the N units in parallel according to the writing data in the buffer; wherein, writing to any unit means: writing the writing data corresponding to the address of the unit in the buffer into the unit.

[0034] In an implementation manner of this embodiment, N is 64 or 128.

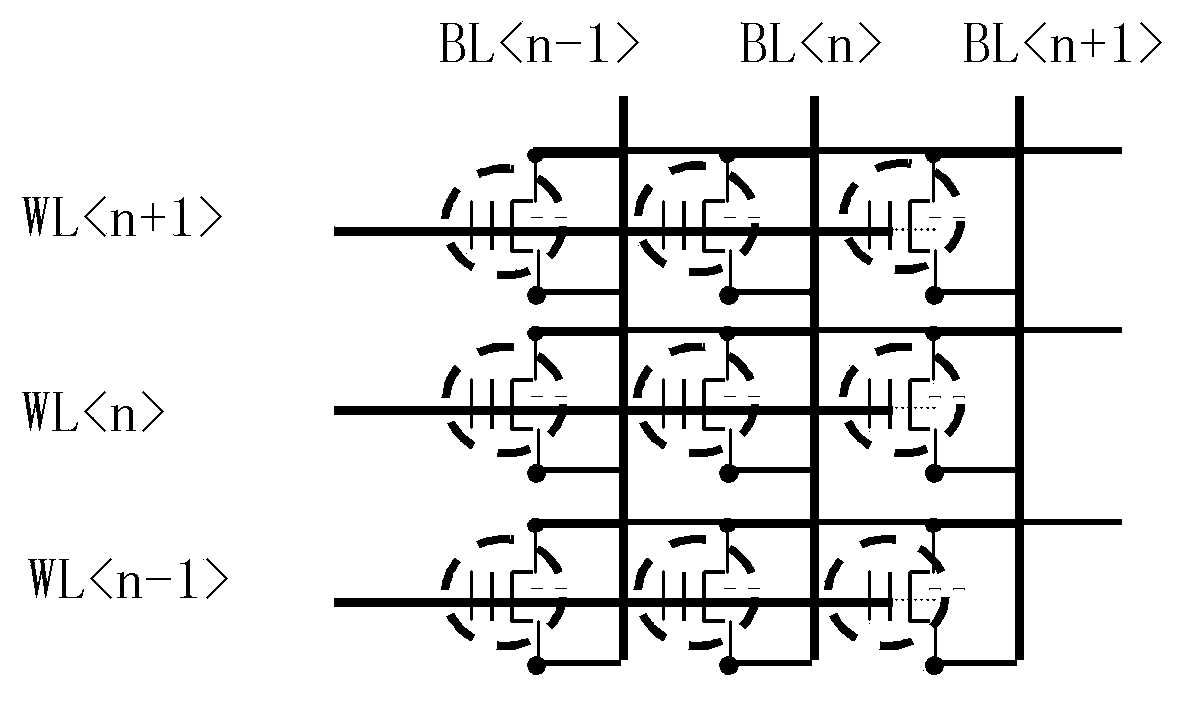

[0035] This embodiment can write 64bits or 128bits data at one time; taking the situation when writing 128bit data as an example, the circuit is changed from the original word line connecting 8 or 16 bit lines to one word line connecting 128 bits Wire. If the drive capability (strength) of the pump is not enough to supp...

Embodiment 2

[0060] Embodiment 2. A device for writing a memory, comprising:

[0061] buffer;

[0062] The control unit is used to input an instruction for writing the buffer, and clear the data in the buffer; and write the addresses of the N units in the memory and the writing data corresponding to each address into the buffer; N is a positive integer;

[0063] A writing unit, configured to verify and write the N units in parallel according to the writing data in the buffer; wherein, writing any one unit refers to: writing the address of the unit in the buffer Write data is written to the unit.

[0064] In an implementation manner of this embodiment, N is 64 or 128.

[0065] In an implementation manner of this embodiment, the control unit can also be used to reload the one or more addresses if it is judged that the data in one or more addresses has an error before inputting the command to write the buffer. , and writing data of the one or more addresses to the buffer; input...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com