FPGA (field programmable gate array)-based failure recovery method

A fault recovery and watchdog technology, applied in the direction of response errors, etc., can solve problems that affect FPGA programming, configuration, lack of configuration of the working status monitoring system, and failure to reset in time to achieve the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be further introduced below in conjunction with the accompanying drawings and specific embodiments.

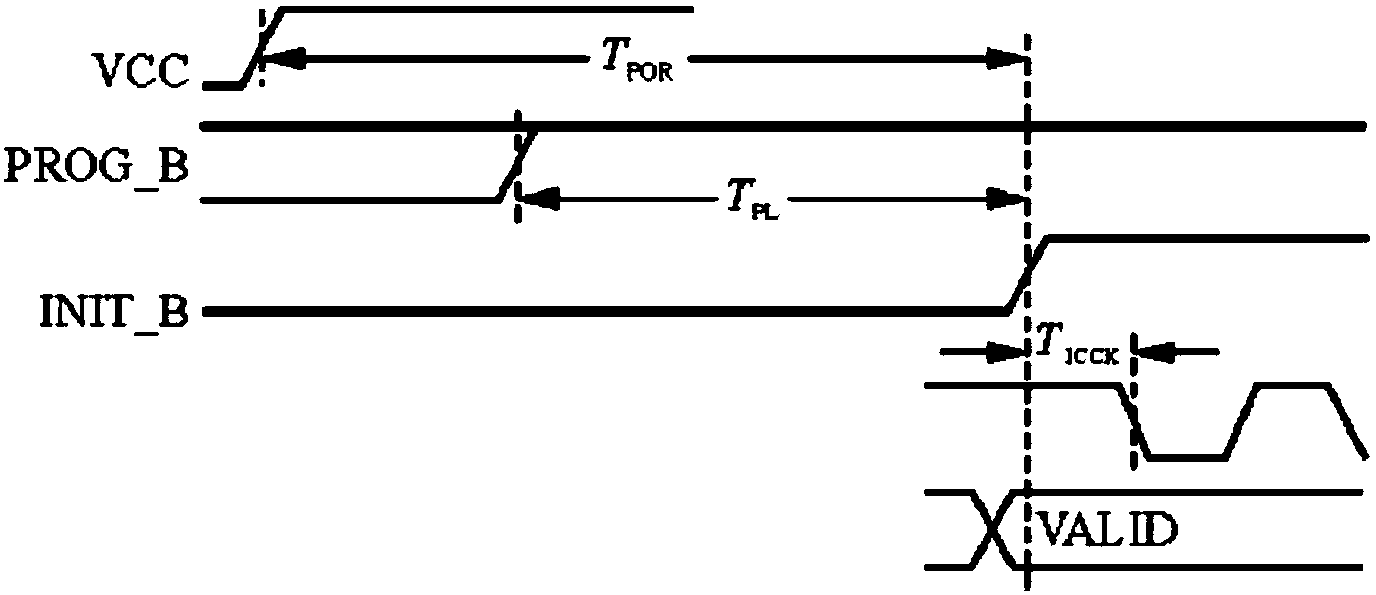

[0019] Such as figure 1 As shown, when the PROG_B signal of Xilinx FPGA is low, the configuration register is cleared, and the FPGA reloads the program from the configuration Flash.

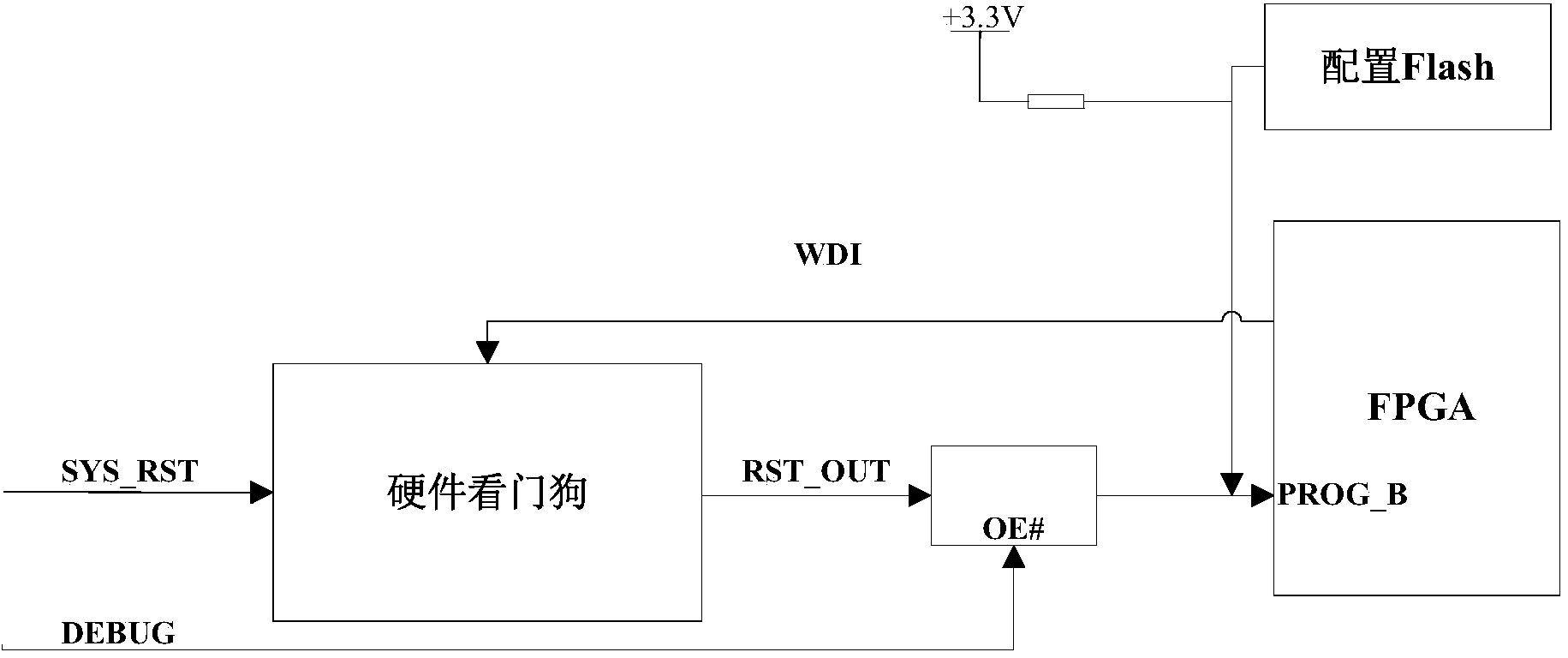

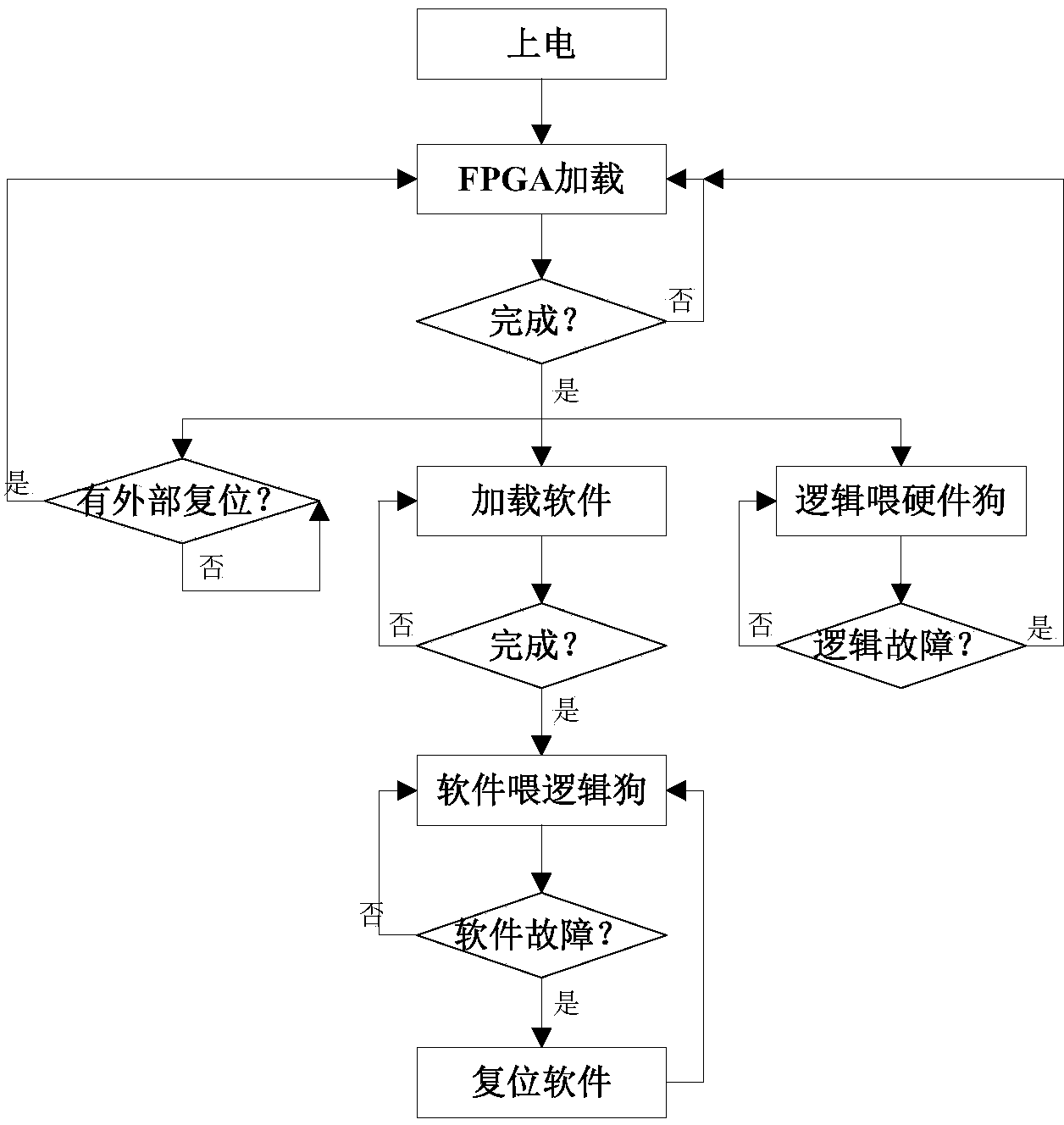

[0020] Such as figure 2 As shown, the fault recovery system is mainly composed of a hardware circuit unit and a logic watchdog unit. The hardware circuit unit mainly includes hardware watchdog chip, Xilinx FPGA and configuration Flash; the logic watchdog unit is mainly implemented by coding the logic written on the PC, and compiling and generating software or logic suitable for chip loading format. Configuration Flash and hardware watchdog are connected to PROG_B of Xilinx FPGA.

[0021] In addition, if the DEBUG signal is not connected, there will be a problem that the bit file cannot be burned during the debugging process, but the mcs file can be burned nor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More